4;:

;о

00

со

4;

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОЧАСТОТНЫЙ ФАЗОЦИФРОВОЙ ДЕТЕКТОР | 1988 |

|

RU2040851C1 |

| Синтезатор частот | 1987 |

|

SU1478327A1 |

| Цифровой фазовый детектор | 1985 |

|

SU1352638A2 |

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Делитель-синтезатор частот | 1982 |

|

SU1149395A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Цифровой фазовый детектор для синтезаторов частот | 1988 |

|

SU1539677A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР, содержащий последовательно соединенные цифроаналоговый преобразователь, фильтр нижних частот и импульсно-фазовый Детектор, выход которого является выходом детектора, а также первый накапливающий сумматор, первый вход которого является первым входом, а первый кодовый вход - первым информационным входом детектора, отличающийся тем, что, с целью повыщения динамической точности детектирования, в него введены последовательно соединенные фазорасщепитель и RS-триггер, а также второй накапливающий сумматор и блок деления, входы делителя и делимого которого подключены соответственно к первому и второму информационным входам устройства, а выход частного и выход остатка - соответственно к кодовому входу второго накапливающего сумматора и к второму кодовому входу первого накапливающего сумматора, выход импульсов переполнения которого соединен с входом переноса второго накапливающего сумматора, выход которого подключен к входу цифроаналогового преобразователя, вход старщего разряда которого соединен с выходом RS-триггера, S-вход которого подключен к выходу переполнения второго накапливающего сумматора, тактовый вход которого соединен с тактовым входом блока деления и .первым Q входом детектора, причем вход фазорасщепиS теля соединен с вторым входом детектора, (Л а выход задержанных импульсов - с входом управления детектора.

Фиг.1

Изобретение относится к радиотехнике, а именно к устройствам цифрового фазового детектирования импульсных последовательностей на неравных частотах, и может быть использовано для детектирования радиосигналов с угловой модуляцией, формирования сетки стабильных частот в приемопередающей и измерительной аппаратуре и в ряде других случаев.

Наиболее близким к изобретению по технической сущности является устройство цифрового фазового детектирования на неравных частотах, содержащее последовательно соединенные накапливающий сумматор, цифроаналоговый преобразователь (ЦАП), фильтр нижних частот и импульсно-фазовь1Й детектор 1.

Недостатком известного устройства является наличие помех дробности, снижающих динамическую точность детектирования.

Целью изобретения является повыщение динамической точности детектирования.

Поставленная цель достигается тем, что в цифровой фазовый детектор, содержащий последовательно соединенные цифроаналоговый преобразователь, фильтр нижних частот и импульсно-фазовый детектор, выход которого является выходом детектора,-а также первый накапливающий сумматор, первый вход которого является первым входом, а первый кодовый вход - первым информационным входом детектора, введены последовательно соединенные фазорасщепитель и RS-триггер, а также второй накапливающий сумматор и блок деления, входы делителя и делимого которого подключены соответственно к первому и второму информационным входам устройства, а выход частного и выход остатка - соответственно к кодовому входу второго накапливающего сумматора и к второму кодовому входу первого накапливающего сумматора, выход импульсов переполнения которого соединен с входом переноса второго накапливающего сумматора, выход которого подключен к входу цифроаналогового преобразователя, вход старщего разряда которого соединен с выходом RS-триггера, S-вход которого подключен к выходу переполнения второго накапливающего сумматора, тактовой вход которого соединен с тактовым входом блока деления и первым входом детектора, причем вход фазорасщепителя соединен с вторым входом детектора, а выход задержанных импульсов - с входом управления детектора.

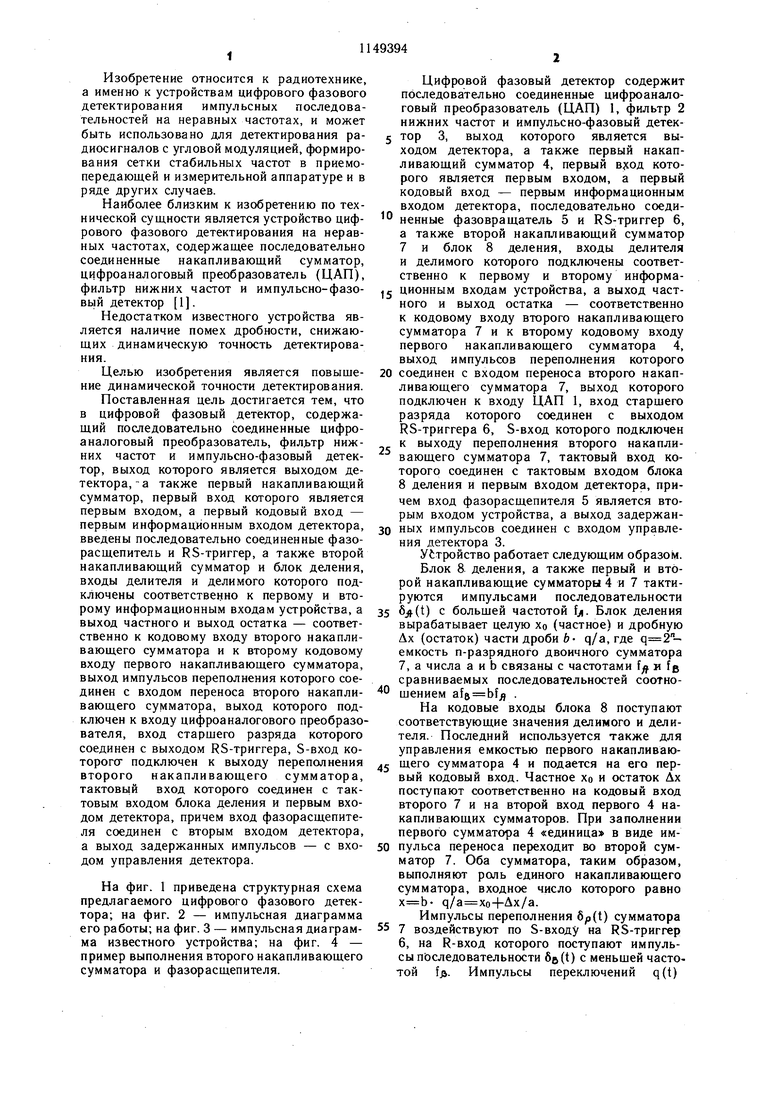

На фиг. 1 приведена структурная схема предлагаемого цифрового фазового детектора; на фиг. 2 - импульсная диаграмма его работы; на фиг. 3 - импульсная диаграмма известного устройства; на фиг. 4 - пример выполнения второго накапливающего сумматора и фазорасщепителя.

Цифровой фазовый детектор содержит последовательно соединенные цифроаналоговый преобразователь (ЦАП) 1, фильтр 2 нижних частот и импульсно-фазовый детектор 3, выход которого является выходом детектора, а также первый накапливающий сумматор 4, первый которого является первым входом, а первый кодовый вход - первым информационным входом детектора, последовательно соединенные фазовращатель 5 и RS-триггер 6, а также второй накапливающий сумматор

7и блок 8 деления, входы делителя и делимого которого подключены соответственно к первому и второму информационным входам устройства, а выход частного и выход остатка - соответственно к кодовому входу второго накапливающего сумматора 7 и к второму кодовому входу первого накапливающего сумматора 4, выход импульсов переполнения которого

0 соединен с входом переноса второго накапливающего сумматора 7, выход которого подключен к входу ЦАП 1, вход старщего разряда которого соединен с выходом RS-триггера 6, S-вход которого подключен к выходу переполнения второго накапливающего сумматора 7, тактовый вход которого соединен с тактовым входом блока

8деления и первым Входом детектора, причем вход фазорасщепителя 5 является вторым входом устройства, а выход задержанных импульсов соединен с входом управления детектора 3.

У&тройство работает следующим образом. Блок 8 деления, а также первый и второй накапливающие сумматоры 4 и 7 тактируются импульсами последовательности

5 6jf(t) с больщей частотой fj). Блок деления вырабатывает целую хо (частное) и дробную Дх (остаток) части дроби 6- q/a, где q 2 емкость п-разрядного двоичного сумматора 7, а числа а и b связаны с частотами i и fg сравниваемых последовательностей соотно щением .

На кодовые входы блока 8 поступают соответствующие значения делимого и делителя. Последний используется также для управления емкостью первого накапливающего сумматора 4 н подается на его первый кодовый вход. Частное Хо и остаток Дх поступают соответственно на кодовый вход второго 7 и на второй вход первого 4 накапливающих сумматоров. При заполнении первого сумматора 4 «единица в виде импульса переноса переходит во второй сумматор 7. Оба сумматора, таким образом, выполняют роль единого накапливающего сумматора, входное число которого равно q/a xo+Дх/а.

Импульсы переполнения 6p(t) сумматора

5 7 воздействуют по S-входу на RS-триггер б, на R-вход которого поступают импульсы пЬследовательности 6e(t) с меньшей частотой f. Импульсы переключений q(t)

RS-триггера 6 поступают на вход старшего разряда ЦАП 1. Входы остальных разрядов ЦАП 1 подключаются к выходу второго накапливающего сумматора 7, формирующего функцию x(t), дискретно изменяющуюся на величину хо с тактовой частотой f/i .При этом старший разряд сумматора

7подключается к второму от старшего разряду ЦАП 1. Этим достигается весовое соответствие процессов x(t) и q(t), необходимое для полной компенсации помех дробности.

Полярность включения триггера 6 выбирается такой, чтобы триггер в момент переполнения сумматора 7 создавал на выходе ЦАП 1 перепад аналоговой величины, противоположный по знаку перепаду, получаемому за счет указанных переполнений.

Сумма q(t)x(t)-j-q(t) преобразовывается с помощью ЦАП в аналоговый эквивалент G(t) (фиг. 2), содержащий две регулярные пилообразные составляющие- высокочастотную Gfl(t) с частотой f, подавляемую фильтром 2, и низкочастотную &в(1), проходящую через фильтр в искаженном виде GftCt) на линейный (коммутируемый) вход импульсно-фазового детектора 3.

8импульсно-фазовом детекторе производятся выборки и запоминание значений Ge(t) в моменты поступления на его импульсный (коммутирующий) вход импульсов 6e(t±t), сдвинутых на время относительно импульсов Sf (t), поступающих на R-вход триггера 6. Сдвиг импульсов по времени осуществляется с помощью фазорасщепителя 5 и необходим для обеспечения работы импульсно-фазового детектора на участках статической характеристики, достаточно удаленных от областей разрыва.

Поскольку функция GR (t) периодическая искажения ее в фильтре 2 (Gg(t), фиг. 2) не приводят к появлению помех дробности, и выходной сигналы (t) детектора представляет собой постоянную составляющую Uo, зависящую от разности фаз входных импульсных последовательностей б (t) и

6B(t).

Таким образом, из сравнения диаграмм (фиг. 2 и фиг. 3) следует, что помеха дробности, возникающая в известном устройстве за счет искажений сигнала в фильтре, принципиально исключается в предлагаемом устройстве, благодаря чему существенно повышается динамическая точность детектирования.

На фиг. 2 и 3 выбраны следующие значения параметров: х q- . Масщтабный множитель при переводе цифровых величин в аналоговые выбран равным единице (например, ординату Хо и соответствующую ей ординату Хо).

0 Число разрядов п. ЦАП 1, а следовательно, и второго накапливающего сумматора 7 выбирается, исходя из требований к подавлению помех дробности, возникающих за счет нециклического характера переносов из первого сумматора во второй. Подавление

5 помех растет пропорционально емкости q, и выбором достаточно больщого значения q долю нецикличности, вносимой переполнениями первого накапливающего сумматора 4, можно свести к пренебрежимо малой величине. Поэтому работа указанного сумматора не отражена () на фиг. 2.

Тактовый вход блока 8 деления может отсутствовать, например, при выполнении его на элементах комбинационной логики. Делимое q- b на входе этого блока фактически представляет собой число Ь, подаваемое со сдвигом на п разрядов в сторону старшего.

На фиг. 4а приведен пример выполнения накапливающего сумматора 7. Он состоит из сумматора С и регистра Р, включенных последовательно и охваченных цепью положительной обратной связи. Для получения импульсов 6p(t), управляющих RS-триггером 6, используется одновибратор, построенный на RSD-триггере Т.

J На фиг. 46 приведен пример выполнения фазорасщепителя 5. На вход счетного триггера Т поступают импульсы $(i) с частотой следования 2Гв. Четные импульсы проходят на выход одного из элементов Ui или U2, а нечетные - на выход другого

0 из них, образуя последовательности импульсов соответственно t(i) и 6(t±T/2) с равными частотами f , сдвинутые на полтакта друг относительно друга. Элементы задержки Т служат для устранения неопределенности в срабатывании элементов

5

и во время переходного процесса в триггере Т.

6(t)

зЛ

Ai

GeM I

ад

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой фазовый детектор | 1980 |

|

SU894854A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-07—Публикация

1982-10-15—Подача