Изобретение относится к радиотехнике, а именно к устройствам цифрового фазового, детектирования на неравных частотах, и может быть использовано для детектирования радиосигналов с угловой модуляцией, получения сигналов рассогласования в системах АПЧ, формирования сетки стабильных частот в приемопередающей и измерительной аппаратуре и в ряде других случаев. Известно устройство цифрового фазового детектирования на неравных частотах, основанное на приведении частот к равенству путем их деления в целое число раз с помощью цифрового делителя частоты с переменным коэффициентом деления 1. Однако из-за инерционности, вносимой делителями частоты в случае, когда частоты имеют малый общий множитель, устройства такого типа не удовлетворяют возросщим требованиям к динамической точности детектирования и применение их в настоящее время ограничено. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство цифро-фазового детектирования, содержащее делитель с переменным коэффициентом деления, соединенный через цифро-аналоговый преобразователь (ЦАП) с суммирующим блоком, и фазовый детектор (ФД) 2. Точность компенсации помехи дробности, т. е. точность цифрового фазового детектирования, обеспечиваемая известным устройством, определяется точностью установки и стабильностью коэффициентов передач ФД, ЦАП и весовых коэффициентов при суммировании, поддержание которых на высоком уровне связано с известными трудностями. Удается достичь устойчивой ко.мпенсации помех дробности до уровня 40 дБ,-что чаще всего оказывается недостаточным. К тому же, указанная величина ослабления помех достигается за счет тщательной настройки и регулировки соответствующи.ч узлов схемы, что снижает экономические показатели при производстве. Целью изобретения является повышение точности детектирования. Поставленная цель достигается тем, что в цифровой фазовый детектор, содержащий делитель частоты и накапливающий регистр, соединенные по входам с арифметическим блоком, введены последовательно соединенные первый переключатель кода.

первый элемент ИЛИ и запоминающий регистр, включенные между кодовым выходом накапливающего регистра и входом введенного цифро-аналогового преобразователя, второй переключатель кода, включенный между кодовым входом арифметического блока и свободным входом первого элемента ИЛИ, введены также последовательно соединенные первый RS-fpnrrep, элемент И, первый триггер со счетны вхоАом и второй RS-триггер, включенные между выходом делителя частоты и управляющим входом второго переключателя кодов, первый элемент задержки, включенный между тактовым входом делителя частоты и свободным входом элемента И, второй триггер со счетным входом, включенный между выходом элемента И и соединенным вместе одним из входов первого RS-триггера и установочным входом первого триггера со счетным входом, и последовательно соединенные вторые элемент ИЛИ и элемент задержки, включенные между выходом элемента И и тактовым входом запоминающего регистра, причем свободный вход второго RS-триггера и свободный вход второго элемента ИЛИ подключены к тактовому входу накапливаюнлего регпстра, а управляющий вход первого переключателя кода соединен с выходом первого триггера со счетным входом.

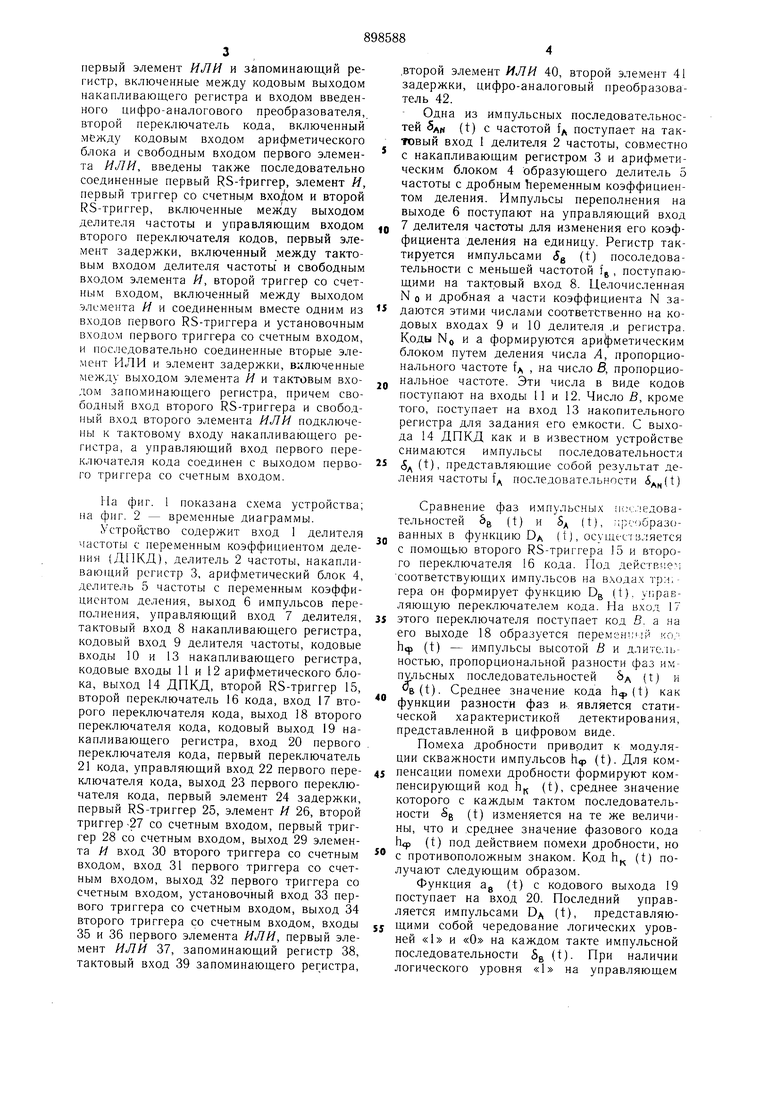

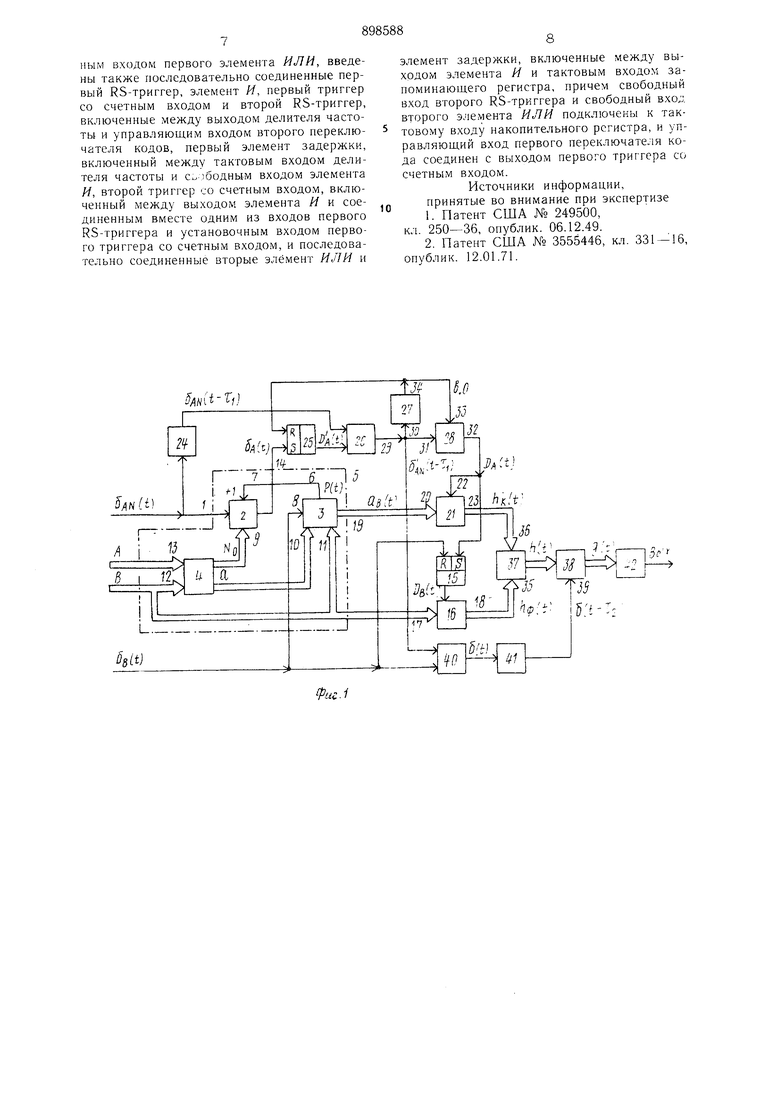

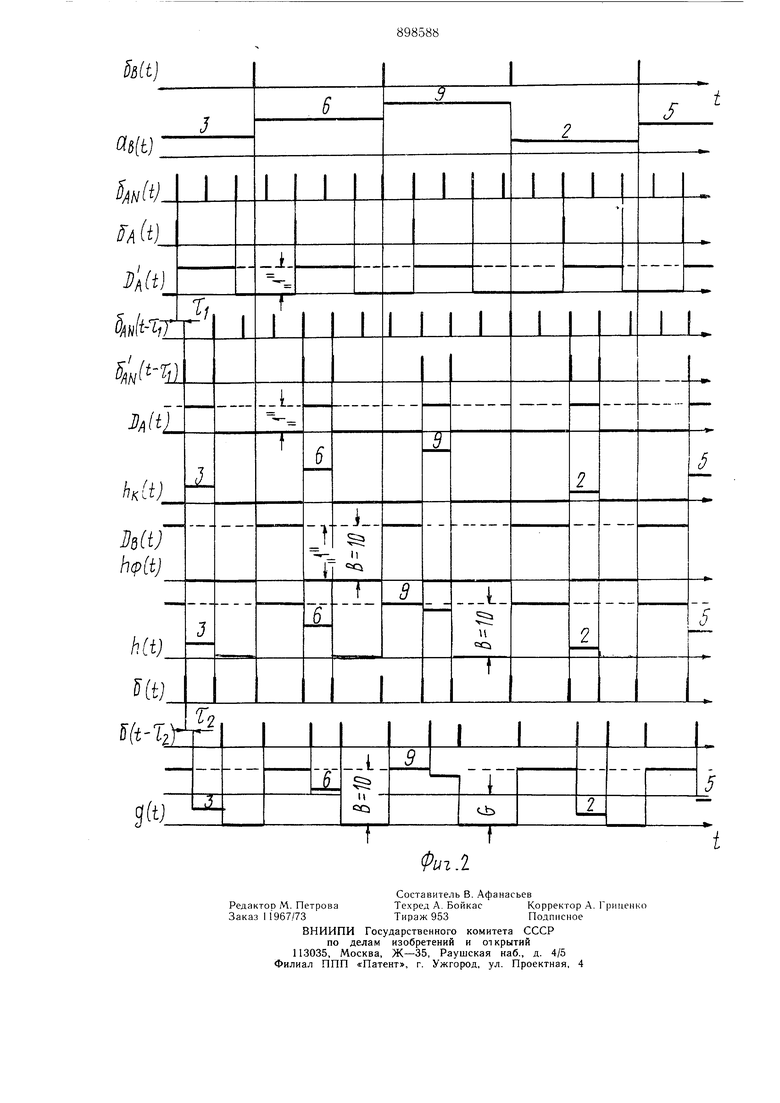

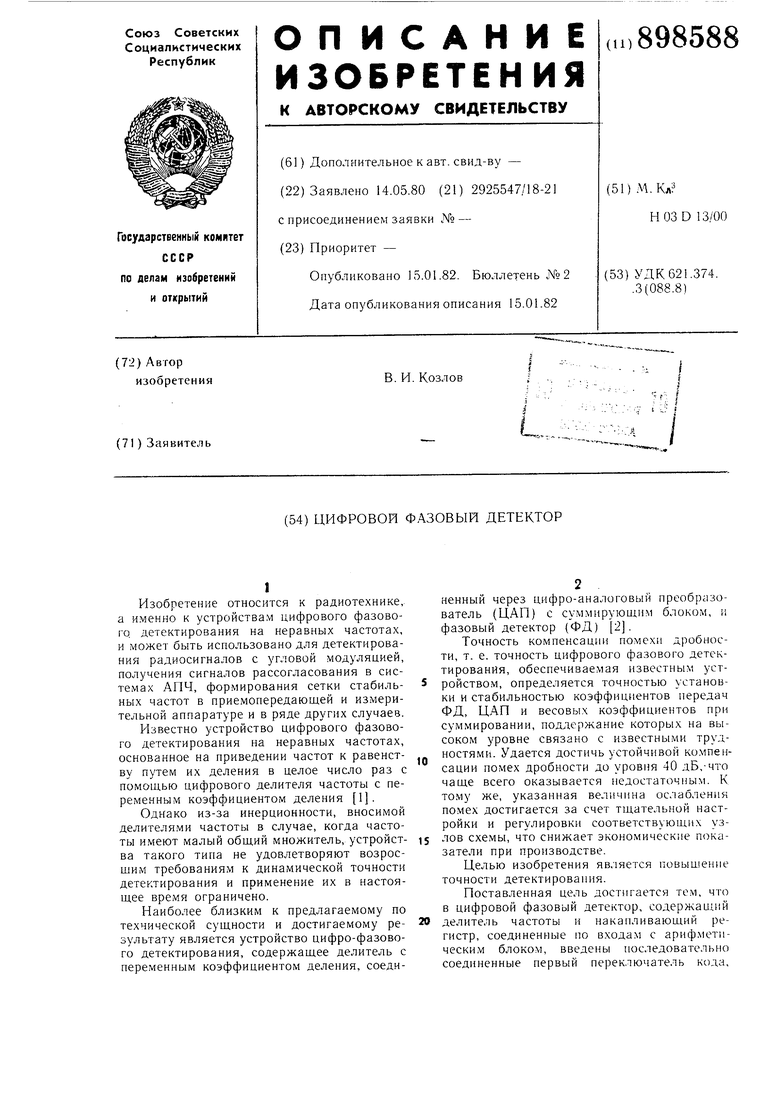

На фиг. 1 показана схема устройства; на фиг. 2 - временные диаграммы.

Устройство содержит вход 1 делителя частоты с переменным коэффициентом деления (ДИКД), делитель 2 частоты, накапливающий регистр 3, арифметический блок 4, делитель 5 частоты с переменным коэффициентом деления, выход 6 импульсов переполнения, управляющий вход 7 делителя, тактовый вход 8 накапливающего регистра, кодовый вход 9 делителя частоты, кодовые входы 10 и 13 накапливающего регистра, кодовые входы И и 12 арифметического блока, выход 14 ДПКД, второй RS-триггер 15, второй переключатель 16 кода, вход 17 второго переключателя кода, выход 18 второго переключателя кода, кодовый выход 19 накапливающего регистра, вход 20 первого переключателя кода, первый переключатель 21 кода, управляющий вход 22 первого переключателя кода, выход 23 первого переключателя кода, первый элемент 24 задержки, первый RS-триггер 25, элемент И 26, второй триггер-27 со счетным входом, первый триггер 28 со счетным входом, выход 29 элемента И вход 30 второго триггера со счетным входом, вход 31 первого триггера со счетным входом, выход 32 первого триггера со счетньЕМ входом, установочный вход 33 первого триггера со счетным входом, выход 34 второго триггера со счетным входом, входы 35 и 36 первого элемента ИЛИ, первый элемент ИЛИ 37, запоминающий регистр 38, тактовый вход 39 запоминающего регистра.

,второй элемент ИЛИ 40, второй элемент 41 задержки, цифро-аналоговый преобразователь 42.

Одна из импульсных последовательностей 5/IH (t) с частотой д поступает на тактовый вход 1 делителя 2 частоты, совместно

с накапливающим регистром 3 и арифметическим блоком 4 образующего делитель 5 частоты с дробным беременным коэффициентом деления. Импульсы переполнения на выходе 6 поступают на управляющий вход

7 делителя частоты для изменения его коэффициента деления на единицу. Регистр тактируется импульсами 5 (t) посоледовательности с меньшей частотой fg , поступающими на тактовый вход 8. Целочисленная N о и дробная а части коэффициента N задаются этими числами соответственно на кодовых входах 9 и 10 делителя .и регистра. Коды NO и а формируются арифметическим блоком путем деления числа А, пропорционального частоте f , на число В, пропорциональное частоте. Эти числа в виде кодов поступают на входы 11 и 12. Число В, кроме того, поступает на вход 13 накопительного регистра для задания его емкости. С выхода 14 ДПКД как и в известном устройстве снимаются импульсы последовательности

6д (t), представляющие собой результат деления частоты f последовательности SA(t)

Сравнение фаз импульсны.; 1;;г,: едовательностей &в () и S; (t), ;1рс)бразс)ванных в функцию DA (t), осуществляется с помощью второго RS-триггера 15 и второго переключателя 16 кода. Под действием соответствующих импульсов на входа.х rpri; гера он формирует функцию Dg (t), управляющую переключателе.м кода. На вход 17 5 этого переключателя поступает код В. а на его выходе 18 образуется перемень й кол (t) - импульсы высотой В и длительностью, пропорциональной разности фаз импульсных последовательностей &А (t) и Ов(1). Среднее значение кода , (t) как функции разности фаз и- является статической характеристикой детектирования, представленной в цифрово.м виде.

Помеха дробности приводит к модуляции скважности импульсов (t). Для ком5 пенсации помехи дробности формируют компенсирующий код h, (t), среднее значение которого с каждым тактом последовательности SB (t) изменяется на те же величины, что и .среднее значение фазового кода Ьф (t) под действием помехи дробности, но с противоположным знаком. Код h (t) получают следующим образом.

Функция ag (t) с кодового выхода 19 поступает на вход 20. Последний управляется импульсами Од (1), представляюJ щими собой чередование логических уровней «1 и «О на каждом такте импульсной последовательности Sg (t). При наличии логического уровня «1 на управляющем входе 22 на его выход 23 передается- функция ag (t). Длительность управляющих импульсов D, (t), а следовательно, и длительность импульсов h (t) равны периоду следования импульсов 5 ()- Амплитуда импульсов h| (t) переменна и равна соответствующим значениям а (t). Импульсы Од (t) формируются с помощью схемы, включающей в себя первый элемент задержки 24, первый RS-триггер 25, элемент И 26, первый триггер 28 со счетным входом и второй триггер 27 со счетным входом. На выход 29 элемента И на каждом такте последовательности Sg (t) проходят два импульса последовательности 8лц(1-Т,) образуя последовательность импульсов лн (t - Т, ). Достигается это тем, что импульсом 5д (t) на одном из входов первого RS-триггера, подключенном к выходу делителя частоты, триггер переводится в состояние, когда его выходной сигнал DA (t) разрешает импульсам (t - i ) проходить через элемент И и поступать на вход 30 второго триггера со счетным входом. Последний по прошествии двух импульсов возвращает триггер 25 в исходное состояние, и элемент И запирается. Импульсы 8Ai,(t-T,) на одном из входов элемента И получают с помощью первого элемента 24 задержки, подключенного ко входу 1 ДПКД. Первый из двух в пачке импульс последовательности 5j (t) на входе 31 триггера 28 устанавливает его в состояние «1, а второй - в состояние «О, благодаря чему на выходе 32 триггера формируется функция переключений DA (t). Для фазирования переключений триггера 28 с переключениями триггера 25 таким образом, чтобы обеспечить необходимую полярность импульсов РА (t), триггер 28 устанавливается в состояние «О одновременно с установкой в «О триггера 25. Для этого установочный вход 33, также как и один из входов триггера 25, подключается к выходу 34. Элемент задержки 24 служит для устранения неопределенностей при работе элемента И. Из фиг. 1 и 2 следует, что время задержки Tj должно равняться или несколько превышать су.ммарную задержку переключеяий делителя 2 и триггера 25, но не повыщать величины Тд 1/Уд Фазовый hip (t) и компенсирующий h| (t) коды с выходов соответственно 18 и 23 поступают на входы 35 и 36. Суммарный код h (t) (t) + h (t) .c выхода элемента ИЛИ передается на запоминающий регистр 38, тактируемый импульсами 8 (t- 2) на его тактовом входе 39. Запоминающий регистр введен для исключения влияния задержки и искажений фронтов функции h (t). Тактирующая импульсная последовательность S(t-T,) фррмируется с помощью второго элемента ИЛИ 40, второго элемента 41 задержки. Входы элемента ИЛИ подключены к выходу 29 и ко входу импульсной последовательности 5g(t). На выходе элемента ИЛИ образуется суммарная последовательность &(t) Sg(t)-t+ AN (-1) выходе элемента задержки - последовательность 5 (t - 2 ) Элемент 41 задержки служит для устранения неопределенностей при записи кодов в регистр 38. На фиг. 1 и 2 видно, что время задержки 2 должно равняться или превышать время установления значений кодов в функции h (t), но так же как и Tj не превосходить величины . Результирующий код g(t) с выхода запоминающего регистра передается на цифро-аналоговый преобразователь 42, осуществляющий преобразование кода в аналоговый эквивалент Выход ЦАП является выходом устройства. Площадь под функцией g (t) -на интервале времени, равном периоду Tg импульсной последовательности 6 (t), на любом участке функции остается постоянной. Объясняется это тем, что приращения площади за счет изменений периода последовательности 6(t), равных ДТ, ;ДТ;, ( I ) соответственно при коэффициенте N, и коэффициенте NO + 1, компенсируются приращениями площади за счет изменений высоты импульсов h(t). Эти приращения соответственно равны ASi аТд ; ЛЗ (В-а)ТА (2) Умножая значения отклонений ATi и ДТ, определяемые выражением (1), на высоту В импульсов (t), и учитывая, что АТд BTg , получим выражения, равные выражениям (2), но с противоположными знаками. Помеха дробности, таким образом, полностью исключается. Аналоговая величина, соответствующая постоянной составляющей G кода g (t), является резу.тьтатом цифрового фазового детектирования и выделяется далее известными метода.ми путем фильтрации гармоник частоты fg. Формула изобретения Цифровой фазовый детектор, содержащий делитель частоты и накапливающий регистр, соединенные по входам с арифметическим блоком, отличающийся тем, что, с целью повыщения точности детектирования, в него введены последовательно соединенные первый переключатель кода, первый элемент ИЛИ и запоминающий регистр, включенные между кодовым выходом накапливающего регистра и входом введенного цифро-аналогового преобразователя, второй переключатель кода, включенный между кодовым входом арифметического блока и свободным входом первого элемента ИЛИ, введены также последовательно соединенные первый RS-триггер, элемент Я, первый триггер со счетным входом и второй RS-триггер, включенные между выходом делителя частоты и управляющим входом второго переключателя кодов, первый элемент задержки, включенный между тактовым входом делителя частоты и Ci. юодным входом элемента И, второй триггер со счетным входом, включенный между выходом элемента И и соединенным вместе одним из входов первого RS-триггера и установочным входом первого триггера со счетным входом, и последовательно соединенные вторые элемент ИЛИ и

элемент задержки, включенные между выходом элемента И и тактовым входом запоминающего регистра, причем свободный вход второго RS-триггера и свободный вход второго элемента ИЛИ подключены к тактовому входу накопительного регистра, и управляющий вход первого переключателя кода соединен с выходом первого триггера со счетным входом.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 249500, кл 250-36, опублик. 06.12.49.

2.Патент США № 3555446, кл. 331 - 16, опублик. 12.01.71.

SAN. fAii)

hii}

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Цифровой фазовый детектор | 1980 |

|

SU1352615A1 |

| Делитель-синтезатор частот | 1982 |

|

SU1149395A1 |

| Цифровой фазовый детектор | 1980 |

|

SU894854A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

Mi) h()

hH) Hi

(

Авторы

Даты

1982-01-15—Публикация

1980-05-14—Подача