Изобретение относится к радиотехнике и может использоваться для получения сетки стабильных частот в приемопередающей и измерительной аппаратуре.

Известен синтезатор частот, содержащий первый и второй накопительные регистры, выходы которых через цифровой сумматор соединены с цифроаналоговым преобразователем, а также фильтр нижних частот и перестраиваемьй генератор, выход которого йбдключен к тактовому входу первого накопительного регистра, а к тактовому входу второго накопительного регистра подклйчен выход опорного генератора Г i , .

Однако данный синтезатор частот имеет недостаточно щирокий диапазон рабочих частот, который ограничен быстродействием цифрового сумматора, а также высокий уровень помех в выходном сигнале синтезатора.

Наиболее близким по технической сущности к изобретению является синтезатор частот, содержащий два генератора, один из которых является onopHbiM генератором, а второй управляемым генератором, последовательно соединенные первый накопительный регистр, цифроаналоговый преобразователь и фильтр нижних частот, выход которого соединен с управляющим входом управляемого генератора, второй накопительный регистр и К-5-триггер, первый вход и выход которого подключены соответственно к выходу переполнения первого накопительного регистра и к входу старшего разряда цифроаналогового преобразователя, при этом тактовый вход первого накопительного регистра соединен с выходом одного из двух генераторов (2 ).

Однако известный синтезатор частот также имеет высокий уровень помех.

Цель изобретения - уменьшение уровня помех в выходном сигнале синтезатора частот.

Поставленная цель достигается тем, что в синтезатор частот, содержащий два генератора, один из которых является опорным генератором, а другой - управляемым генератором, последовательно соединенные первый накопительный регистр, цифроаналоговый преобразователь и фильтр нижних частот, выход которого соединен с управляющим входом управляемого генератора, второй накопительный регистр и R-S-триггер, первый вход и выход которого подключены соответственно к выходу переполнения первого накопительного регистра и к входу старшего разряда цифроаналогового преобразователя, при зтом тактовый вход первого накопительного регистра соединен с выходом одного из

.. двух генераторов, введен блок деления кодов, выходы целой и дробной частей которого подключены соответственно к кодовому входу первого накопительного регистра и к первому кодовому входу второго накопительного регистра, выход переполнения которого соединен с входом переноса первого накопительного регистра, первый кодовый вход блока деления кодов является входом делимого син0 тезатора частот, второй кодовый вход блока деления кодов объединен с вторым кодовым входом второго накопительного регистра и является входом делителя синтезатора частот,

5 тактовый вход второго накопительного регистра объединен с тактовым входом блока деления кодов и подключен к тактовому входу первого накопительного регистра, а .второй вход

0 R-5-триггера соединен с выходом другого из двух генераторов.

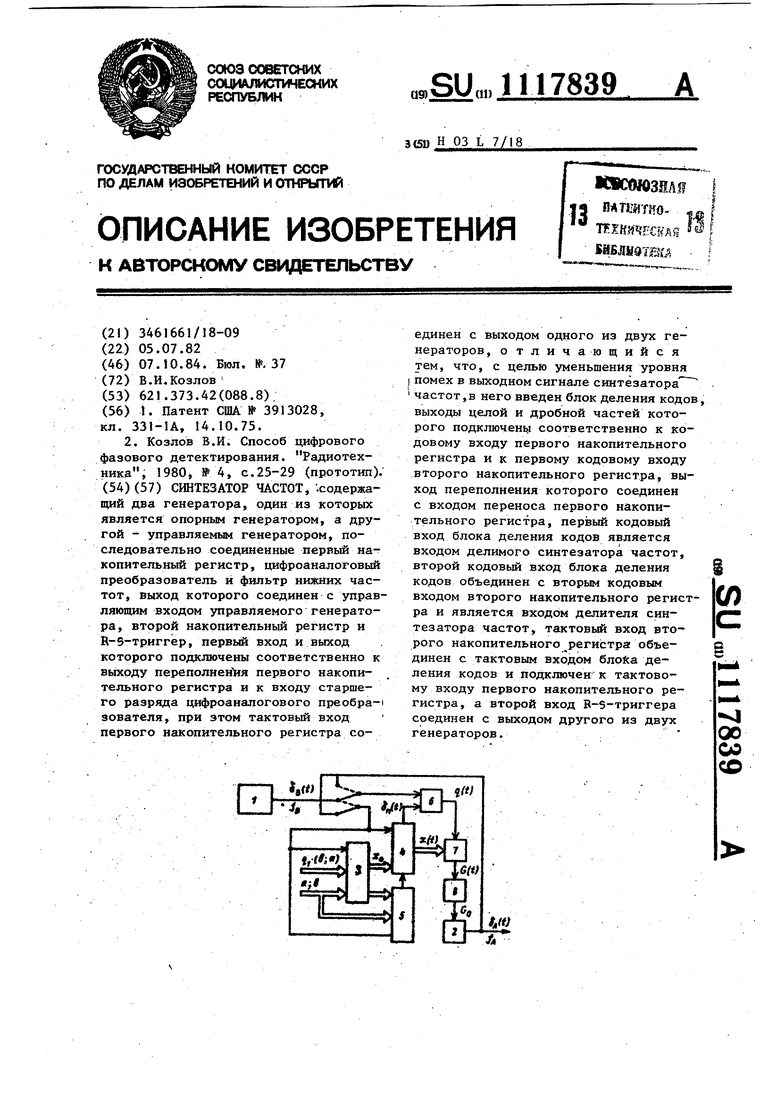

На чертеже изображена структурная электрическая схема синтезатора частот.

Синтезатор частот содержит опорный 1 и управляемый 2 генераторы, блок 3 деления кодов, первый накопительный регистр (НР) 4, вtopoй ИР 5, R-S-триггер 6, цифроаналог овый

преобразователь (ЦАП) 7, фильтр нижних частот (ФНЧ) 8.

Синтезатор частот работает следующим образом.

Блок 3 деления кодов, а также первый и второй HP Аи 5 тактируются импульсами последовательности с большей частотой, например выходными импульсами A(t) управляемого генератора с частотой fд. Этот случай показан на чертеже сплошными линиями. Блок 3 деления кодов вырабатывает целую Хо и дробную Лх части дроби(i где ),2 - емкость первого HP 4, П - число разрядов HP 4, аи Ънаименьшие целые числа, удовлетворя5 ющие условию «,частота опорного генератора I. На кодовые входы блока 3 деления кодов поступают соответственно значения делимого и де3nлителя. Последний используется также для управления емкостью второго HP 5, т.е. в данном случае Частное х и остаток Лх поступаю кодовые входы соответственно пер .вого HP 4 и второго HP 5. При запол нении второго HP 5 импульс переноса переходит в первый HP 4. Оба накопительньпс регистра вьтолняют, таким образом, роль единого регистра, производящего накопление числа I X(Vib/« Xo-e4X/o(. Импульсы переполнения o)(t) первого HP 4 воздействуют на один из входов R-5-триггера 6, на другой вход которого поступают импульсы последовательности с меньшей частотой, например импульсы опорной частоты с выхода опорного генератора 1, как показано на чертеже сплошной линией. Триггер выполняет роль фазового детектора. Импульсы. переключений ci,(-tlc его выхода передаются через старший разряд ДАЙ 7 на вход ФНЧ 8, который вьщеляет постоянную составляющую используемую для управления частотой управляемого генератора 2. В петле фазовой автоподстройки достигается равенство опорной частоты fg среднему значению частоты переполнения fn первого HP 4, т.е. fe fn f «/V.f/jWo(. Следовательно, выходная частота синтезатора равна f д f g « /t. Изменяя числа о( и Ь, можно управлять выходной частотой и шагом сетки частот синтезатора. 94 Помеха дробности, возникающая в системе за счет некратности чисел XQ и q/ , компенсируется путем преобразования текущего значения числа x(t) на выходе HP 4 с помощью ЦАП 7. При этом старший разряд ИР 4 подключается к второму от старшего разряда ЦАП 7. Этим достигается весовое соответствие процессов x{t/и с(Ь), необходимое для полной компенсации помех дробности. Число разрядов ЦАП 7 и первого HP 4 выбирается исходя из Требований к подавлению помех дробности. Долей нецикличности, вносимой переполнениями второго HP 5, в этом случае можно пренебречь. Подавление помех растет пропорционально емкости Тактовый вход у блока 3 деления кодов может отсутствовать, например, при:выполнении его на элементах комбинациоиной логики. Делимое,Ь на входе этого блока фактически представляет собой число Ъ , подаваемое со сдвигом на г разрядов в сторону старшего числа., При и, соответственно, b с( ( связи для этого случая показаны на чертеже штриховыми линиями ) числа с| и. Ъ взаимно меняются местами. Тогда у, п в Vqi-fe / Делимое и делитель меняются местами, и при постоянном шаге сетки частот емкость второго HP 5 при этом остается неизменной. Кроме того, уровень помех дробности в этом случае ниже, так как коэффициент передачи / системы фазовой автоподстройки для этих помех уменьшается в соответствующее число раз. ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1983 |

|

SU1202054A1 |

| Делитель-синтезатор частот | 1982 |

|

SU1149395A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Синтезатор частот | 1987 |

|

SU1478327A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

СИНТЕЗАТОР ЧАСТОТ, -.содержащий два генератора, один из которых является опорным генератором, а другой - управляемым генератором, последовательно соединенные первый накопительный регистр, цифроаналоговый преобразователь и фильтр нижних частот, выход которого соединен с управ ляющим входом управляемого генератора, второй накопительный регистр и Н-5-триггер, первый вход и выход которого подключены соответственно к вьпсоду переполненИя первого накопительного регистра и к входу старшего разряда цифроаналогового преобразователя, при зтом тактовый вход первого накопительного регистра соединен с выходом одного из двух генераторов, о тличающийся тем, что, с целью уменьшения уровня помех в выходном сигнале синтезатора частот, в него введен блок деления кодов, выходы целой и дробной частей которого подключены соответственно к кодовому входу первого накопительного регистра и к первому кодовому входу второго накопительного регистра, выход переполнения которого соединен с входом переноса первого накопительного регистра, первый кодовый вход блока деления кодов является входом делимого синтезатора частот, второй кодовый вход блока деления кодов объединен с вторым кодовым входом второго накопительного регистра и является входом делителя синтезатора частот, тактовый вход второго накопительного регистра; объединен с тактовым входом бло(са деления кодов и подключен к тактовому входу первого накопительного регистра, а второй вход В-5-триггера соединен с выходом другого из двух генераторов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3913028, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Козлов В.И | |||

| Способ цифрового фазового детектирования | |||

| Радиотехника, 1980, №4, с.25-29 (прототип) | |||

Авторы

Даты

1984-10-07—Публикация

1982-07-05—Подача