ел

со

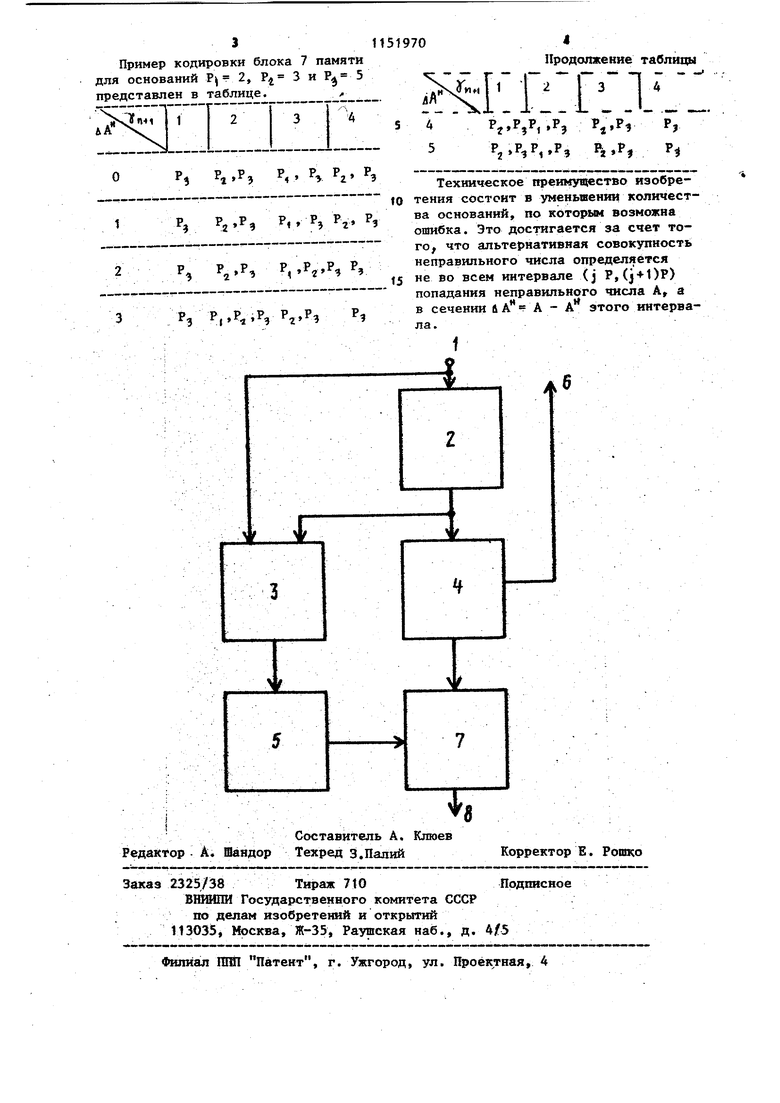

о Изобретение относится к вычислительной технике и может быть исполь зовано для коррекции однократных ошибок в динамике вычислительного процесса в системе остаточных классов (СОК). Известно устройство для обнаружения ошибок в системе остаточньпс классов, содержащее блок нулевизаци блок памяти констант ошибок, дешифратор, переключатель, сумматор и группы элементов И 0J . Недостатками данного устройства являются значительные аппаратурные затраты и большое количество оснований в альтернативной совокупности Наиболее близким по технической сущности к изобретению является уст ройство для определения альтернатив ной совокупности чисел в системе остаточных классов, содержащее блок нулевизации, блок анализа и блок памяти, причем вход операнда устрой cTsa соединен с входом блока нулевизации, выход которого соединен с входом блока анализа, первый и второй выходы которого соединены соответственно с выходом отсутствия ошибки устройства и адресньм входом блока памяти, выход которого является выходом устройства 2 . Недостатком известного устройства является большое количество осно ваний, по которым возможна ошибка в альтернативной совокупности. Для устранения ошибки требуется заменит все оборудование, работающее по данным основаниям, что .требует значительны аппаратурных затрат и сви детельствует о неэффективности контроля. Цель изобретения - повышение коэф фициента использования оборудования Поставленная цель достигается тем, что устройство для определения альтернативной совокупности чисел в системе остаточных классов, содер жащее блок нулевизации, блок памяти и блок анализа, причем вход операнда устройства соединен с входом блока нулевизатдии, выход которого соединен с входом блока анализа, пе вый и второй выходы которого соединены соответственно с первым адресн входом блока памяти и выходом отсутствия ошибки устройства, выход блока памяти явлiяeтcя информационным выходом устройства, содержит вычитатель по модулю и блок преобразования кода системы остаточных классов в позиционный код, причем вход и выход блока нулевизации соединены соответственно с входами уменьшаемого и вычитаемого вычитателя по модулю, выход которого соединен с входом блока преобразования: кода системы остаточных классов в позиционный код, выход которого соединен с вторым адресным входом блока памяти. На чертеже представлена структурная схема устройства для определения альтернативной совокупности чисел в системе остаточных классов. Устройство содержит вход 1 операнда, блок 2 нулевизации, вычитатель 3 по модулю, блок 4 анализа, блок 5 преобразования кода системы остаточных классов в позиционный код, выход 6 отсутствия ошибки, блок 7 памяти, выход 8 альтернативной совокупности. Блок 4 анализа пропускает информацию с входа на первый выход и при равенстве нулю информации на его входе формирует еднничньА сигнал на втором выходе. Устройство для определения альтернативной совокупности чисел в системе остаточных классов работает следуюврда образом. На вход 1 поступает операнд А (а,, Oj,.. ., Ой, ), представленный в системе остаточных классов. Блок 2 нулевизации приводит его к виду А « (0,0, . .,0 J у „) . На вычитателе 3 по модулю выполняется операция ь.А А - А по модулю Р Результат данной операции поступает на блок 5 преобразования кода системы остаточных классов в позиционный код, с выжода которого результат в позиционном коде поступает на второй адресно вкод блока 7 памяти. UrtoK 4 анализа приводит сравне с нулем и при равенстве нулю формирует сигнал на выходе 6 свидетельствук)Ер1й об отсутствии ошибки в числе А. При неравенстве | нутаз, данная величина поступает на первый адресный вход блока 7 памяти, где по адресу, заданному А А и |f выбирается на выход 8 совокупность оснований, по которым возможна ошибка.

31151970

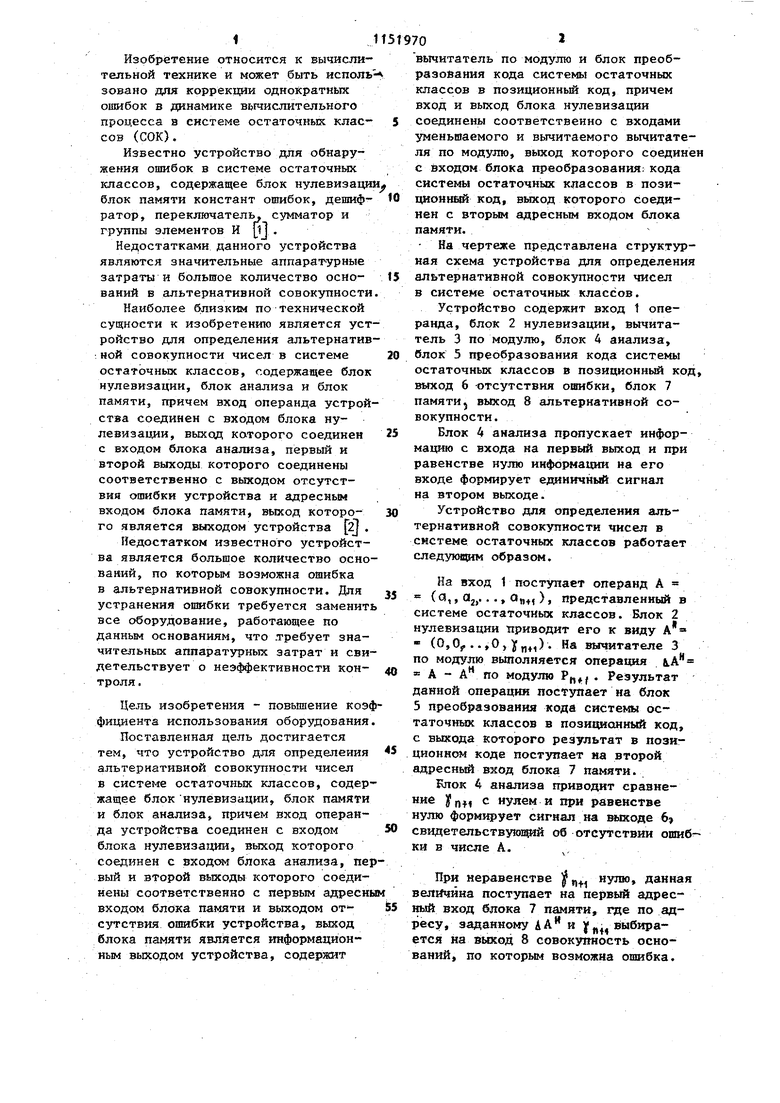

Пример кодировки блока 7 памяти для оснований Р 2, Р 3 и Рл 5 представлен в таблице. ,Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| @ -Ичный сумматор | 1983 |

|

SU1166097A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1979 |

|

SU862143A1 |

| Устройство для обработки информации, представленной в системе остаточных классов | 1990 |

|

SU1743002A1 |

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ ОШИБОК В ИЗБЫТОЧНОМ МОДУЛЯРНОМ КОДЕ | 1991 |

|

RU2015620C1 |

| Устройство для преобразования чисел из кода системы остаточных классов в позиционный код с контролем ошибок | 1991 |

|

SU1797119A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Устройство для сложения многоразрядных @ -ичных чисел | 1983 |

|

SU1163321A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU888124A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ АЛЬТЕРНАТИВНОЙ СОВОКЗТ1НОСТИ ЧИСЕЛ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ, содержащее блок нулевиэации, блок памяти и блок анализа, причем вход операнда устройства соединен с входом блока нулевизации, выход которого соединен с входом блока анализа, первый и второй выходы которого соединены соответственно с первым адресным входом блока памяти и выходом отсутствия ошибки устройства, выход блока памяти является информационным выходом устройства, о тличающееся тем, что, с целью повышения коэффициента испольг зования оборудования, оно содержит вычитатбль по модулю и блок преобразования кода системы остаточных классов в позиционный код, причем вход и выход блока нулевизации соединены соответственно с входами уменьшаемого и вычитаемого вычитателя по модулю, выход которого соединен с входом блока преобразо(Л вания кода системы остаточных классов в позиционный код, выход которого соединен с вторым адрест входом блока памяти.

.P г Р

Техническое преимущество изобретения состоит в уменывении количества оснований, по которым возможна ошибка. Это достигается за счет того , что альтернативная совокупность неправильного числа определяется не во всем интервале (j PjCjfDP) попадания неправильного числа А, а в сечении НА А - А этого интервала.

i

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU888124A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Акушский И.Я., Цдицкий Д.И | |||

| Машинная арифметика в остаточных классах | |||

| М., Советское радио, 1969, с | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

Авторы

Даты

1985-04-23—Публикация

1983-06-28—Подача