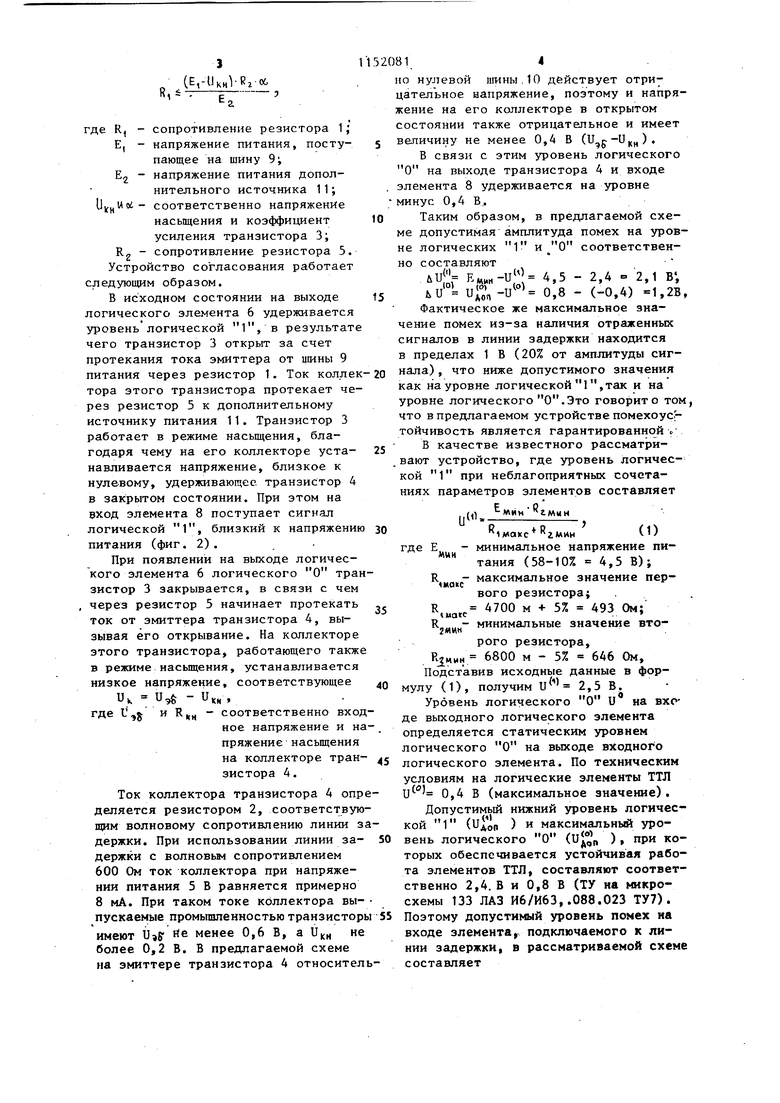

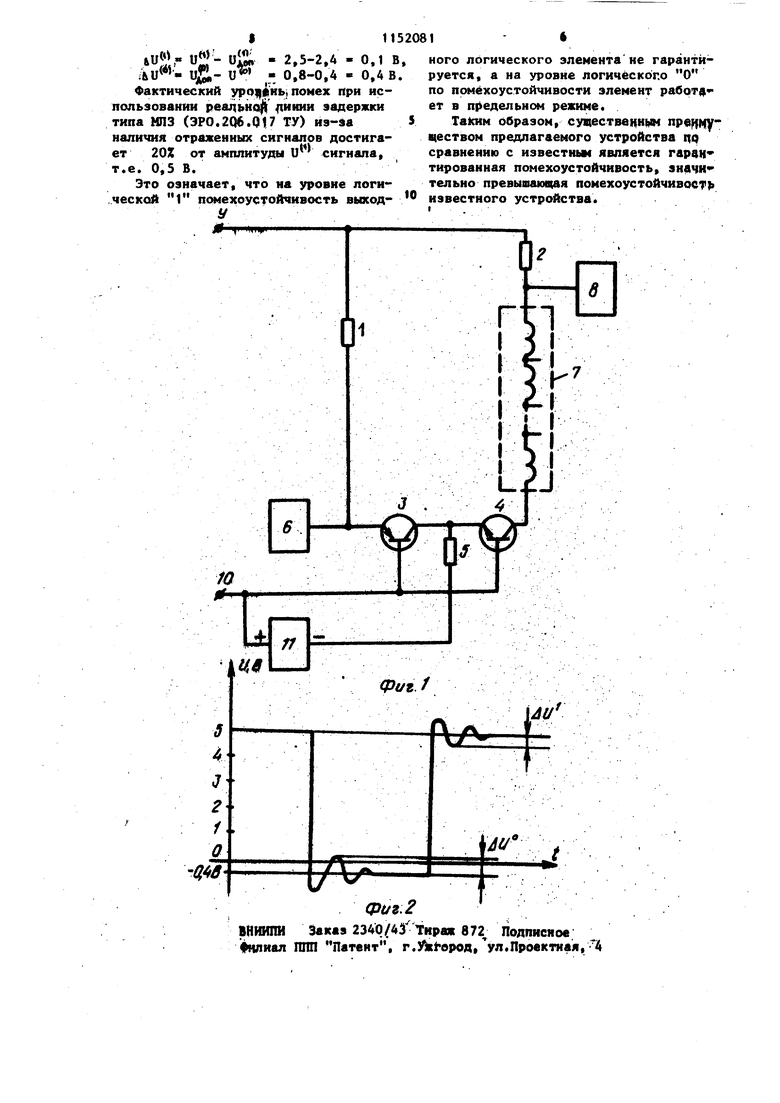

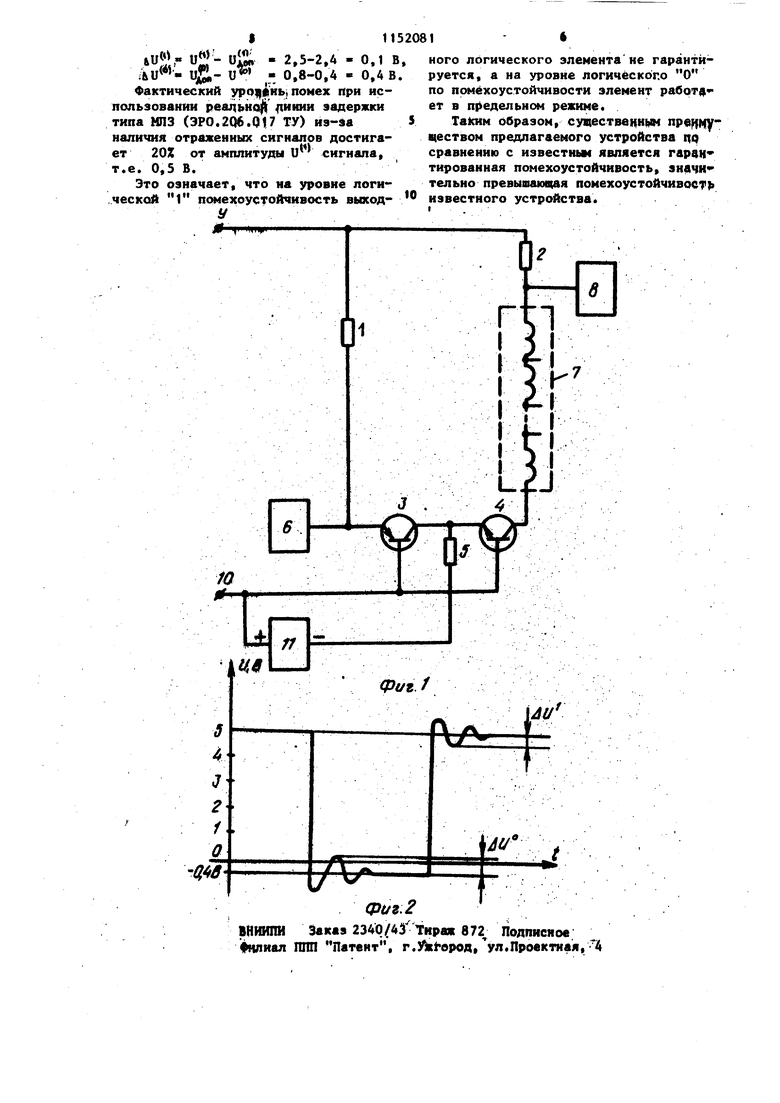

Изобретение относится к автоматике и вычислительной технике и предназначено для реализации логических узлов, обеспечивающих сдвиг сигналов. Известно устройство согласования логических элементов с коаксиальной линией задержки, содержащее входной логический элемент, выход которого через первый резистор подключен к выводу второго резистора, соединенного другим выводом с шиной питания и к входу коаксиальной линии, выход которой подключен к входу выходного логического элемента ij , Недостатком этого устройства является отсутствие согласования по вы .ходу коаксиальной линии. Наиболее близким к изобретению по технической сущности является устройство согласования логических элементов с линуей задержки, содержа щее первый резистор, подключенный ме ду шиной основного источника питания и выходом входного логического элемента, соединенного с входом линии задержки, второй резистор, подключенный од ним выводом к концу линии задержки и к входу выходного логического элемента, а другим - к нулевой шине if Недостатком известного устройства является низкая помехоустойчивость, вызванная неполным согласованием линии задержки, из-за разброса парамет ров линии задержки и резисторов, и н личия отраженных сигналов в линии. Цель изобретения - повышение помехоустойчивости устройства. Поставленная цель достигается тем что в устройство согласования логических элементов с линией задержки, содержащее первый резистор, подключенный между шиной основного источника питания и выходом входного логического элемента, второй резистор подключенный одним выводом к концу линии задержки и к входу выходного логического элемента, и общую шину, введены дополнительный источник питания, два транзистора разного типа проводимости, третий резистор, при этом другой вывод второго резистора подключен к шине основного источника питания, эмиттер первого транзистора соединен с выходом входного логического элемента, коллектор второго тракзистора подключен к входу линии задерж ки,первая шина дополнительного источника питания подключена к третьему резистору, другой вывод которого соединен с коллектором первого транзистора и эмиттером второго транзистора, а вторая шина дополнительного источника питания - к базам обоих транзисторов и общей шине. На фиг. 1 приведена электрическая схема предлагаемого устройства; на фиг. 2 - диаграммы, поясняющие его работу. Устройство согласования логических элементов с линией задержки содержит первый 1 и второй 2 резисторы, первый транзистор 3 (о-п-р типа), коллектор которого соединен с эмиттером второго транзистора А (h-p-n типа) и с одним выводом третьего резистора 5, а эмиттер соединен с выходом входного логического элемента 6 и одним выводом первого резистора 1. Качлектор транзистора А соединен с входом линии 7 задержки, выход которой соединен с входом выходного логического элемента 8 и одним выч водом второго резистора 2, другой вывод Которого соединен с другим выводом первого резистора 1 и с шиной 9 источника питания, базы обоих транзисторов 3 и 4 соединены между собой и подключены к общей шине 10 и второй шине дополнительного источника 11 питания, первая шина которого соединена с другим выводом третьего резистора 5. Дпя обеспечения работоспособности схемы должны выполняться определенные требования к значению резисторов 1 и 5 и напряжению дополнительного источника 11 питания. По величине резистор 5 должен соответствовать волновому сопротивлению линии задержки, что необходимо для ее согласования по входу. Во время передачи сигнала через линию задержки данный резистор подключается к ее началу через открытый транзистор 4, сопротивление которого в режиме насьвцения очень мало. Для обеспечения режима насьш1ения этого транзистора напряжение дополнительного источника питания 11 должно быть больше напряжения питания логических элементов. Резистором 1 задается величина тока эмиттера транзистора 3, работаКяКего в режиме насьпцения. В таком режиме транзистор находится при- выпЬлнении следующего условия: о (MiKHVRz-o6 1 - -с где R, - сопротивление резистора 1 , Е, - напряжение питания, поступающее на шИну 9; Eg - напряжение питания дополнительного источника 11; соответственно напряжение насыщения и коэффициент усиления транзистора 3; Rg - сопротивление резистора 5. Устройство согласования работает следующим образом. В исходном состоянии на выходе логического элемента 6 удерживается уровень логической 1, в результате чего транзистор 3 открыт за счет протекания тока эмиттера от цины 9 питания через резистор 1. Ток коллек тора этого транзистора протекает через резистор 5 к дополнительному источнику питания 11. Транзистор 3 работает в режиме насыщения, благодаря чему на его коллекторе устанавливается напряжение, близкое к нулевому, удерживающее транзистор 4 в закрытом состоянии. При этом на вход элемента 8 поступает сигнал логической 1, близкий к напряжени питания (фиг. 2). При появлении на выходе логического элемента 6 логического О тра зистор 3 закрывается, в связи с чем через резистор 5 начинает протекать ток от эмиттера транзистора 4, вызывая его открывание. На коллекторе этого транзистора, работающего такж в режиме насыщения, устанавливается низкое напряжение, соответствующее UK и,6 - и,,, где L,J и R,, - соответственно вхо ное напряжение и н пряжение насьщения на коллекторе тран зистора 4. Ток коллектора транзистора 4 опр деляется резистором 2, соответствую щим волновому сопротивлению линии з держки. При использовании линии задержки с волновьм сопротивлением 600 Ом ток коллектора при напряжении литания 5 В равняется примерно 8 мА. При таком токе коллектора выпускаемые промышленностью транзистор имеют и Ке менее 0,6 В, а U не более 0,2 В. В предлагаемой схеме на эмиттере транзистора 4 относител но нулевой шины, 10 действует отрицательное напряжение, поэтому и напряжение на его коллекторе в открытом состоянии также отрицательное и имеет величину не менее 0,4 В (). В связи с этим уровень логического О на выходе транзистора 4 и входе элемента 8 удерживается на уровне минус 0,4 В.. Таким образом, в предлагаемой схеме допустимая амплитуда помех на уровне логических 1 и О соответственно составляют &UJJ Е„,н-и;; 4,5 - 2,4 2,1 В , /. Ui7, 0,8 - (-0,4) 1,2В, Фактическое же максимальное значение помех из-за наличия отраженных сигналов в линии задержки находится в пределах 1 В (20% от амплитуды сигнала) , что ниже допустимого значения как на уровне логической 1,так и на уровне логического О.Это говорито том, что в предлагаемом устройстве помехоусГтойчивость является гарантированной В качестве известного рассматривают устройство, где уровень логической 1 при неблагоприятных сочетаниях параметров элементов составляет с . о Айн iMoicc г(ин где Е - минимальное напряжение пи тания (58-10% 4,5 В); мо«с м симальное значение первого резистора; ..atc 00 м + 5% 493 Ом; ,,..,„ минимальные значение второго резистора, 6800 м - 5% 646 Ом, Подставив исходные данные в формулу (1), получим 2,5 В. Уровень логического О U на вхо де выходного логического элемента определяется статическим уровнем логического О на выходе входного логического элемента. По техническим условиям на логические элементы ТТЛ 1) 0,4 В (максимальное значение). Допустимый нижний уровень логической 1 (иДо ) и максимальный уровень логического О ( ) , при которых обеспечивается устойчивая работа элементов ТТЛ, составляют соответственно 2,4. В и 0,8 В (ТУ на микросхемы 133 ЛАЗ И6/И63,.088.023 ТУ7). Поэтому допустимый уровень помех на входе элемента, подключаемого к линии задержки, в рассматриваемой схеме составляет

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь логических уровней | 1978 |

|

SU790327A1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| Устройство согласования | 1983 |

|

SU1138942A1 |

| Датчик состояния вентилей реверсивного тиристорного преобразователя | 1991 |

|

SU1787303A3 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2002 |

|

RU2233022C1 |

| УСТРОЙСТВО СОГЛАСОВАНИЯ НА ОСНОВЕ ОПТОЭЛЕКТРОННОГО КЛЮЧА | 2007 |

|

RU2369007C2 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| Стабилизатор постоянного напряжения с защитой от перенапряжений | 1986 |

|

SU1493991A1 |

| Стабилизированный преобразователь постоянного напряжения | 1989 |

|

SU1700539A1 |

| Программируемая линия задержки | 1982 |

|

SU1019589A1 |

УСТРОЙСТВО СОГЛАСОВАНИЯ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ С ЛИЩ1ЕЙ ЗАДЕга1а I содержащее первый резистор, подклмпцейный между шиной основного источнццка питания и выходон входного логцческогЬ элемента, второй резистор, подключенный ОДНЮ В||1ВбДОМ к концу нии задержки, и к входу выходного логического элемента,, и общую , отличающееся тем, что, с целью повышения помехо- устойл ивости, в него введены дополнительный источник питания, два транзистора разного типа проводимости, третий резистор, при этом дру гой вывод второго резистора подключен к шине основного источника питания, змиттер первого транзистора со единен с выходом входного логического злемента, коллектор второго транзистора подключен к входу линии задёр |(ки, первая шина дополнительного источника питания подключена к третьему резистору, другой вывод которого соединен с ксллект ч ом первого транзистсфа и эмиттером второго транзистора, а вторая шина дополнительного источника питания :К базам обоих, транзисторов и общей шине.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Под ред | |||

| Б.В | |||

| Тарабрина, М., Эчергия, 1981, с | |||

| АППАРАТ ДЛЯ ФОРМОВАНИЯ И УПЛОТНЕНИЯ ТОРФА, ГЛИНЫ И ДРУГИХ ПЛАСТИЧНЫХ МАТЕРИАЛОВ, ВЫПУСКАЕМЫХ ИЗ МУНДШТУКА НЕПРЕРЫВНОЙ ЛЕНТОЙ | 1922 |

|

SU609A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ът | |||

| Прибор для шлифования оптических линз, ограниченных поверхностями параболоидов вращения любых размеров | 1923 |

|

SU664A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-04-23—Публикация

1983-11-24—Подача