в

«п

00

00

о

4i

00

Изобретение относится к импульсной технике и предназначено для использования в логических устройствах ЭСЛ-типа.

Целью изобретения является увеличение надежности работы путем обеспечения соответствия выходных логических уровней стандартным для ЭСЛ- схем с полной компенсацией в случае использования стандартных термоста- билизированных опорных напряжений.

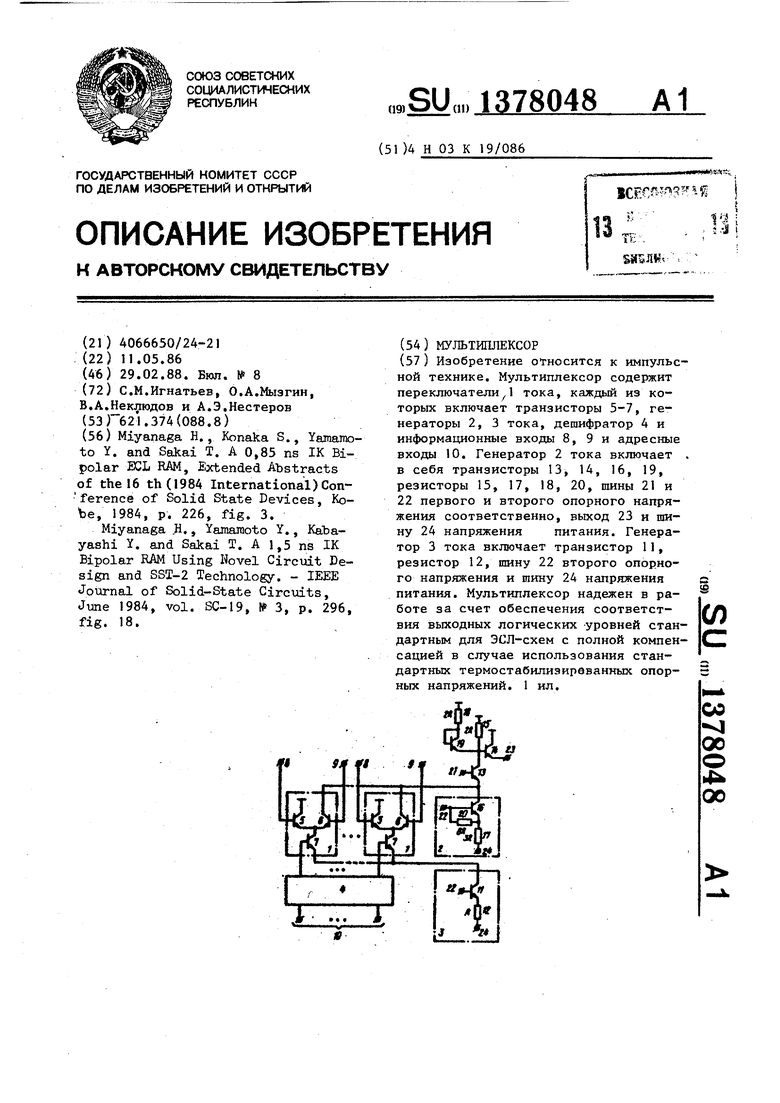

На чертеже изображена принципиальная электрическая схема мультиплексора.

Мультиплексор содержит переключатели тока 1, второй генератор тока 2, первый генератор тока 3 и дешифратор 4, каждый переключатель тока Г состоит из первого, второго и тре- тьего транзисторов 5, 6 и 7 соответственно, эмиттеры первого и второго транзисторов 5 и 6 подключены к коллектору третьего транзистора 7, а коллектор первого транзистора 5 сое- динен с шиной нулевого потенциала, базы первых и вторых транзисторов 5 и 6 переключателей тока 1 являются информационными входами 8 и 9 мультиплексора, базы третьих транзис- торов 7 через дешифратор соединены с адресными входами 10 мультиплексора, первый генератор тока 3 состоит из седьмого транзистора 11 и третьего резистора 12, коллектор транзистора 11 подключен к эмиттерам третьи транзисторов 7 переключателей тока 1, коллектор четвертого транзистора 13 и база пятого транзистора 14 через первый резистор 15 соединены с шиной нулевого потенциала, второй генератор тока 2 вьшолнеи на восьмом транзисторе 16 и четвертом резисторе 17, коллектор транзистора 16 подключен к эмиттеру транзистора 13, первый вывод второго резистора 18 соединен с шиной нулевого потенциала, а второй - с базой и коллектором шестого транзистора 19, эмиттер которого подключен к базе транзистора 14, коллектор транзистора 14 сое- динен с шиной нулевого потенциала, первый и второй вьгеоды пятого резистора 20 подключены соответственно к базе и эмиттеру транзистора 16, база транзистора 13 подключена к шине 21 первого опорного напряжения, а базы транзисторов 11 и 16 подключены к шине 22 второго опорного напряжения, эмиттер транзистора 13 подключен к

коллекторам транзисторов 6 переключателей тока 1, а эмиттер транзистора 14 является выходом 23 мультиплексора, эмиттеры транзисторов 11 и 16 соответственно через резисторы 12 и 17 соединены с шиной 24 напряжения питания.

Мультиплексор работает следующим образом.

Дешифратор 4 предназначен для выборки мультиплексируемых линий. В соответствии с адресом, установленным на адресных входах 10, на одном из выходов дешифратора 4 формируется высокий логический уровень. Коллекторный ток транзистора 11 генератора тока 3 включается в эмиттер транзистора 7 и затем протекает в узел эмиттеров транзисторов 5 и 6 переключателя тока I,соответствующег выбранной линии. Информация на информационные входы 8, 9 мультиплексора поступает в парафазном виде, в выбранном переключателе тока 1 коллекторный ток транзистора 7 протекает в эмиттер того из транзисторов

5и 6, на базе которого более высокий потенциал. Если более высокий потенциал на базе транзистора 5, ток коллектора транзистора 7 протекает

в шину нулевого потенциала, а если потенциал вьш1е на базе транзистора 6, этот ток течет в эмиттере транзитора 13. Высокий логический уровень на выходе 23 мультиплексора формируется в том случае, когда в эмиттере транзистора 13 протекает только ток коллектора транзистора 16, при этом падение напряжения на резисторе 15 минимально, если в эмиттер транзистора 13 включается ток транзистора

6выбранного переключателя тока I, падение напряжения на резисторе 15 максимально и на выходе 23 мультиплексора формируется низкий логический уровень. В соответствии с этим базы транзисторов 5 переключателей тока 1 являются прямыми информационными входами 8, а базы транзисторов 6 являются инверсными информационными входами.

Номинальные сопротивления резистора 12 генератора тока 3, резисторов 15, 17, 18 и 20 формирователя выходных уровней 2 относятся между собой соответственно как 1, 2, 3, 2 и 6.

В стандартных ЭСЛ-устройствах используются два опорных напряжения.

ервое опорное напряжение, стабили- зированное по температуре и относительно нулевого потенциала, предназначено для идентификации входных огических уровней. Номинальное знаение уровня этого опорного напряжения равно полусумме пороговых значений напряжений уровней логического нуля и единицы. Например, пороговые ,« напряжения и уровень первого опорного напряжения соответственно равны 1,465 В,. -1,175 В и -1,32 В.

Второе опорное напряжение предназначено для питания генераторов . тока, уровень этого напряжения стабилизирован относительно напряжения питания, а его номинальное значение равно напряжению питания минус номинальное значение первого опорного напряжения

Ч,,„1.(1)

5

20

Принцип формирования вьпсодных логических уровней в стабилизированных ЭСЛ-устройствах выбран таким образом, что первое опорное напряжение и идеальные значения выходных напряжений логического нуля -UO и логической единицы -и 1, определенные в условиях пренебрежения базовыми токами транзисторов и зависимостью напряжения на открытых -п-переходах от тока, связаны уравнениями:

Ul оп,

ио I и,„1.

Но.2гУ|-У.,п

(4)

«

5 I

,6..2,у,,,16| (5)

,«

.

20

2535

где и 11 и - разности потенциалов между базовыми и эмиттерными выводами транзисторов 11 и 16; (У1 1 , die - коэффициенты передачи

эмиттерного тока в схеме ОБ транзисторов II и 16, в случае интегрального исполнения устройства зти параметры можно считать одинаковыми для всех транзисторов и обозначить о(; г12, г17 и

г20 - сопротивления резисторов 12, 17 и.20 соответственно.

В режиме формирования высокого логического уровня на выходе 2 мультиплексора транзистор 19 закрыт, так как напряжения на резисторе 15, воз- никаинцего за счет протекания в нем тока коллектора транзистора 13, состоящего только из тока коллектора транзистора 16, определенного выражением (5), недо статочно (сопротивление резистора 15 меньше сопротивления резистора 17, напряжение на котором, согласно выражениям (5) и (1) меньше порогового значения Ug 19). Таким образом, высокий выходной логический уровень формируется в соответствии с формулой

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1985 |

|

SU1285589A1 |

| Дешифратор | 1986 |

|

SU1336251A1 |

| Формирователь сигнала для выборки элементов матрицы | 1982 |

|

SU1045364A1 |

| Параметрический источник опорного напряжения для запоминающего устройства | 1989 |

|

SU1647647A1 |

| Дешифратор запоминаюшего устройства | 1979 |

|

SU871330A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

| ИСТОЧНИК ОБРАЗЦОВЫХ НАПРЯЖЕНИЙ | 1993 |

|

RU2076351C1 |

| Триггерный логический элемент И | 2022 |

|

RU2802370C1 |

Б генераторе тока 3 разность потенциалов между базой транзистора 11 и первым выводом резистора 12 складывается из напряжения между базовым и эмиттерным выводами транзистора 11, которое слабо зависит от тока эмиттера и напряжения на резисторе, сопротивление которого определяет ток в этой цепи. Транзистор 16 и резистор 17 формирователя выходных уроней 2 выполняют те же функции, что и компоненты 11, 12 генератора 3 - вырабатывают ток. Подключение резистора 20 к базовому и эмиттерному выводам транзистора 16 предназначено для ответвления части тока резистора 17. Таким образом, коллекторные то- ки транзистора 11 - генератора тока 3 и транзистора Д6 - 1,(16 формирователя выходных уровней 2 описываются следующими выражениями:

Ul

г15

- ;Т7 «(-ип-и.,14,(6)

иди с учетом выражения (1 ) и отношения сопротивлений резисторов 12, 17 и 20, эквивалентного отношению 2, 3 и 6,.

Ul |(ио„1+ Щ,6}+ I . (7)

Соотношения электрических параметров транзисторов 14 и 16 выбраны таким образом, что %Ug-14, и фбр- мула (7/, если пренебречь отклонениями 0 от единицы, приводится в соответствие с формулой (2).

В режиме формирования низкого выходного логического уровня к коллекторному току транзистора 16, проте- кающего в транзисторе 13, прибавляется ток коллектора транзистора 11 генератора тока 3 и сумма этих токов распределяется между резистором 15 и эмиттером транзистора 19. С целью обеспечения соответствия выходного напряжения выражению (3 ) электрические параметры компонентов выбраны таким образом, что ток, протекающий в цепи, состоящей из транзисто- pa 19 и резистора 18, равен удвоенному току коллектора транзистора 16, а ток в резисторе 15 соответственно равен коллекторному току транзистора 11 генератора тока 3 за вычетом коллекторного тока транзистора 16 формирователя выходньпс уровней 2. .Таким образом, для выходного напряжения низкого логического уровня - ио можно привести два уравнения:

(8)

ио -2rl8I,16-U5,19-U6 14

и

иО -rl5(l,ll-IJ6)-UJ4

63

(9)

При учете выражения (l) и выражения для 1ч16 (5), учете отиощения сопротивлений резисторов 17 и 18, равного 3/2, в допущении равенства с/ и предположении равенства напряжений UgjH, Ugjl6 и Ugjl9 формула (8 ) преобразуется следующим образом:

иО - I -(|и.14-и„„1}-2и,,14 (10)

и становится тождественной формуле (З}, Для достижения такого же тождества для формулы (9) необходимо дополнительно допустить равенство напряжений U,l 1 и и учесть от- нощение сопротивления резистора 12 генератора тока 3 и сопротивлений других резисторов

ио -2(-и 14-и„п 1 )-и,Л6- i UJ63

.

(11)

Транзисторы 11, 13, 14, 16, 19 работают в нормальном активном режиме, при этом напряжения между их базовыми и эмиттерными выводами оп- 50 ределяются суммой падений напряжений на эмиттерных р-п-переходах и на сопротивлениях базовых Областей

1Э

V ie+ /T-inC.),

(12)

где г.. - сопротивление базовой обласБ

ти;

I,- - ток базы;

Q , 0

5

0

5 0

5

0

5

tcT - термодинамический потенциал делений на величину заряда электрона;

1Э, 130- соответственно ток эмиттера и тепловой ток эмиттерного р-п-перехода,

Соответствие принятому равенству напряжений Ug транзисторов 14, 16 и 19 и транзистора 11 генератора тока 3 достигается за счет вьшолнения соотношений параметров этих компонентов, определенных на основе конкретных вольт-амперных характеристик, обеспечиваемых выбранным технологическим процессом с учетом конкретных режимов работы компонентов. Однако отношение эмиттерных токов транзисторов 16 и 19 можно считать независимой константой, равной 1/2, и требование равенства двум отношения величин базовых сопротивлений г16 и г19 и равенства 1/2 отношения тепловых токов эмиттерных р-п-переходов 1Э016/1Э019 этих транзисторов очевидно следует из принятой формулы для 1)5(12). Отклонение реальной величины коэффициента V от единицы, наличие тока в базе транзистора 14, которыми пренебрегли при выведении формулы, и изменение Ugjl4 транзистора 14, вызванное различием выходных токов мультиплексора при формировании разных выходных уровней, приводят к отклонению значений уровней логических напряжений на выходе мультиплексора от идеальных, однако при соблюдении определенных требований к параметрам компонентов эти отклонения не будут превышать заданных в ТУ допусков.

Мультиплексор имеет минимальную задержку в тракте распространения сигналов от информационных входов 8, 9 до выхода 23 благодаря минимальной протяженности этого тракта, который состоит из ЭСЛ-переключателя тока на транзисторах 5 и 6, транзистора 13, включенного по схеме ОВ, и эмиттерного повторителя на транзисторе 14. Коллекторный ток транзистора 16 кроме формирования высокого логического уровня на резисторе 15 предназначен для формирования начального падения напряжения на эмиттерном р-п- переходе транзистора 13, что необходимо для уменьшения колебаний напряжения узла коллекторов вторых транэисторов 6 переключателей тока 1, обладающего большой емкостью, с целью ускорения переходного процесса при смене выходного уровня.

Формулаизобретения

Мультиплексор, содержащий переключатели тока, каждый из которых содержит первый и второй транзисторы, эмиттеры которьпс подключены к коллектору третьего транзистора, коллектор первого транзистора соединен с шиной нулевого потенциала, эмиттеры третьих транзисторов переключателей тока через первый генератор тока соединены с шиной напряжения пи- таиия, адресные входы мультиплексора подключены к базам третьих транзисторов переключателей тока, коллектор четвертого транзистора подключен к базе пятого тра1нзистора и через первый резистор соединен с коллектором пятого транзистора и пш- ной нулевого потенциала, экшттер пятого транзистора подключен к выходу мультиплексора, база четвертого транзистора подключена к шине первого опорного напряжения, а эмиттер через второй источник тока подключен к шине напряжения питания и соединен с коллекторами вторых транзисторов.

5

0

5

0

отличающийся тем, что, с целью увеличения надежности работы путем обеспечения соответствия выходных логических напряжений стандартным требованиям для.термостабили- зированных ЭСЛ-устройств в условии использования стандартных опорных напряжений, в него введен шестой транзистор , эмиттер которого подключен к коллектору четвертого транзистора, а коллектор и база через второй резистор соединены с шиной нулевого потенциала, при этом первый и второй генераторы тока выполнены соответственно на седьмом и восьмом Транзисторах, эмиттеры которых соответственно через третий и четвертый резисторы соединены с шиной напряжения питания, базы подключены к шине второго опорного напряжения, база вось мого транзистора через пятый резистор соединена с его эмиттером, а номинальные сопротивления первого, второго, третьего, четвертого и пятого резисторов относятся между собой соответственно как 2, 2, 1, Зиб, сопротивления базовых областей восьмого и шестого транзисторов относятся соответственно как 2 и 1, а отношение теш101вых токов эмиттерных р-п- переходов восьмого и шестого транзисторов равно 1/2,

| Miyanaga Н., Konaka S., Yamamo- to Y | |||

| and Sakai T | |||

| A 0,85 ns IK Bipolar BCL RAM, Extended Abstracts of the 16 th(l984 International)Con- ference of Solid State Devices, Kobe, 1984, p | |||

| Переносное устройство для вырезания круглых отверстий в листах и т.п. работ | 1919 |

|

SU226A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Miyanaga H., Yamamoto Y., КаЪа- yashi Y | |||

| and Saiai T | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| - IEEE Journal of Solid-State Circuits, June 1984, vol | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| ДЖИНО-ПРЯДИЛЬНАЯ МАШИНА | 1920 |

|

SU296A1 |

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1988-02-28—Публикация

1986-05-11—Подача