Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах контроля и диагностирования периферийных устройств. ; Целью изобретения является расширение функциональных возможностей устройства за счет введения при диагностике режима останова синхросерии по заданному сигналу и режима имитации ошибок.

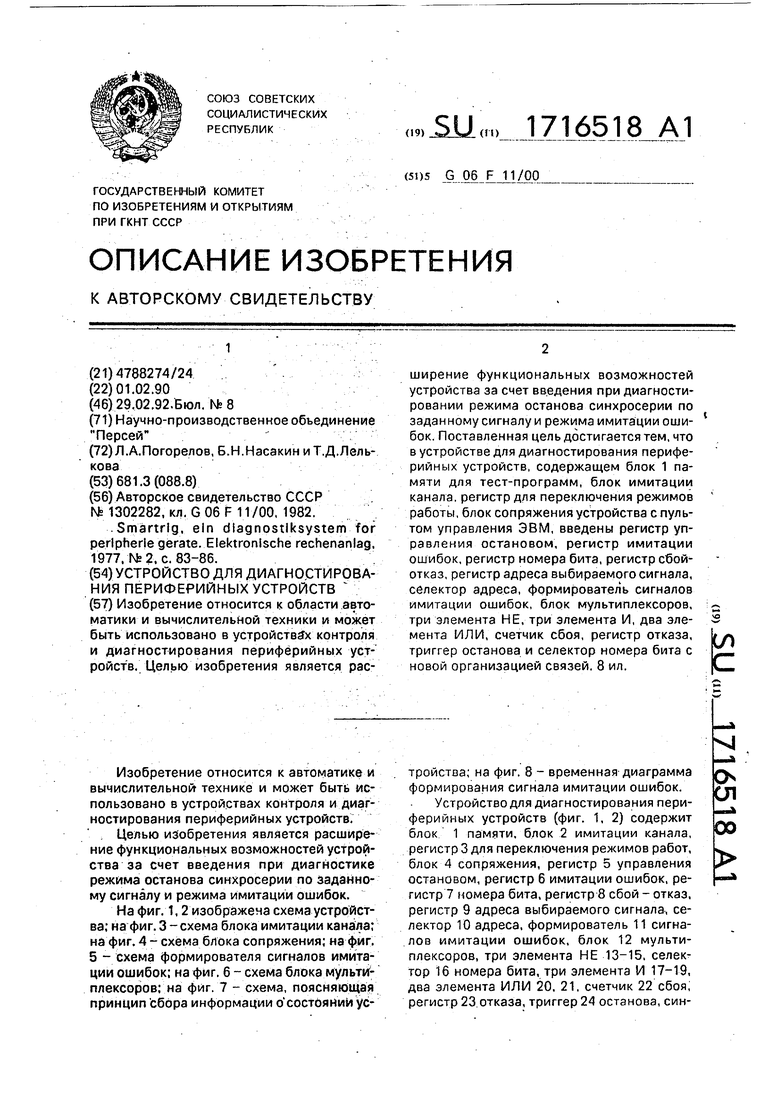

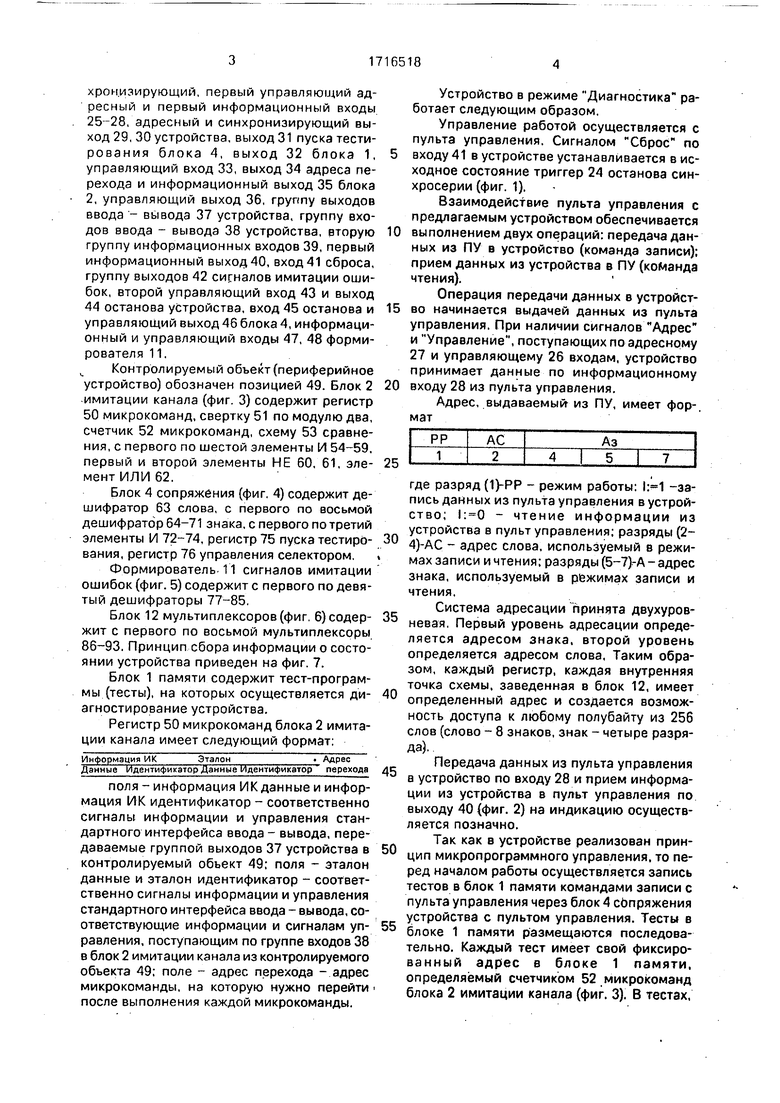

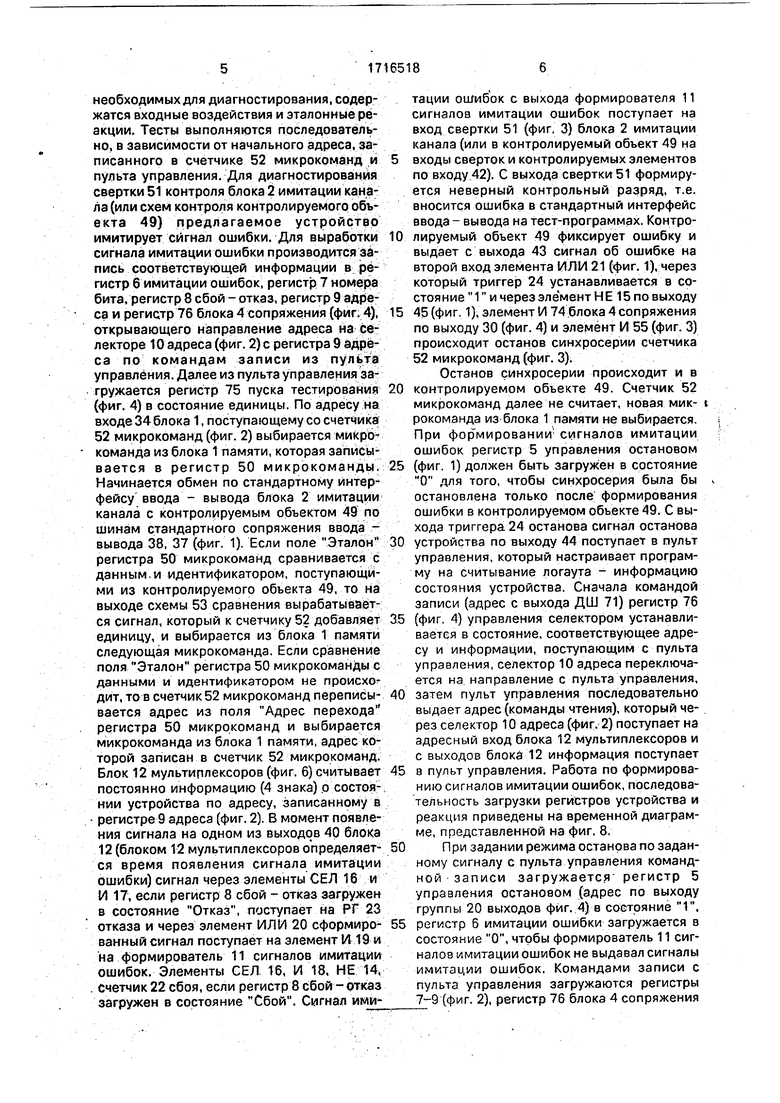

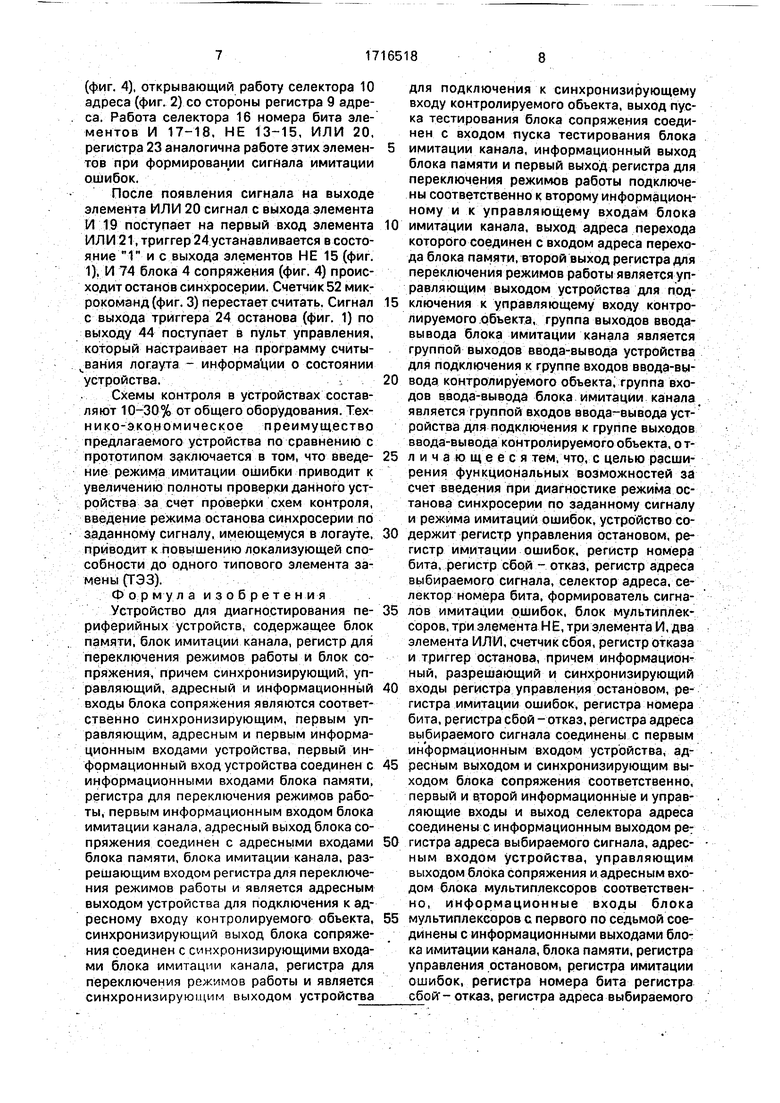

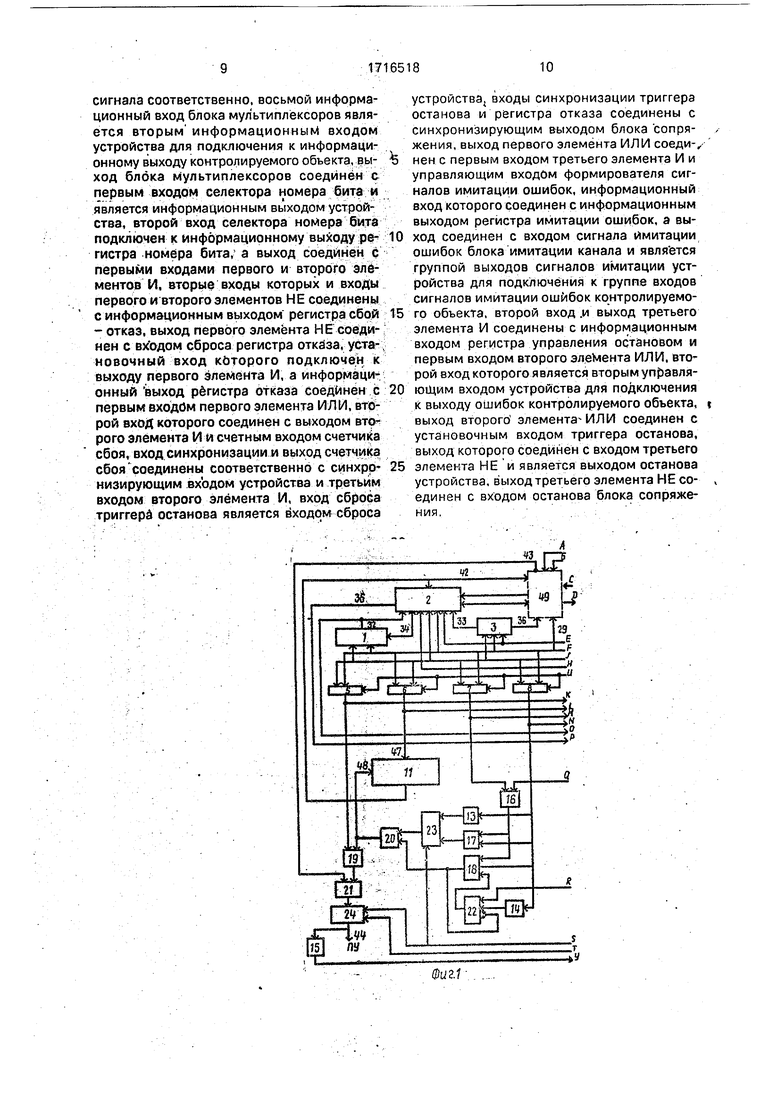

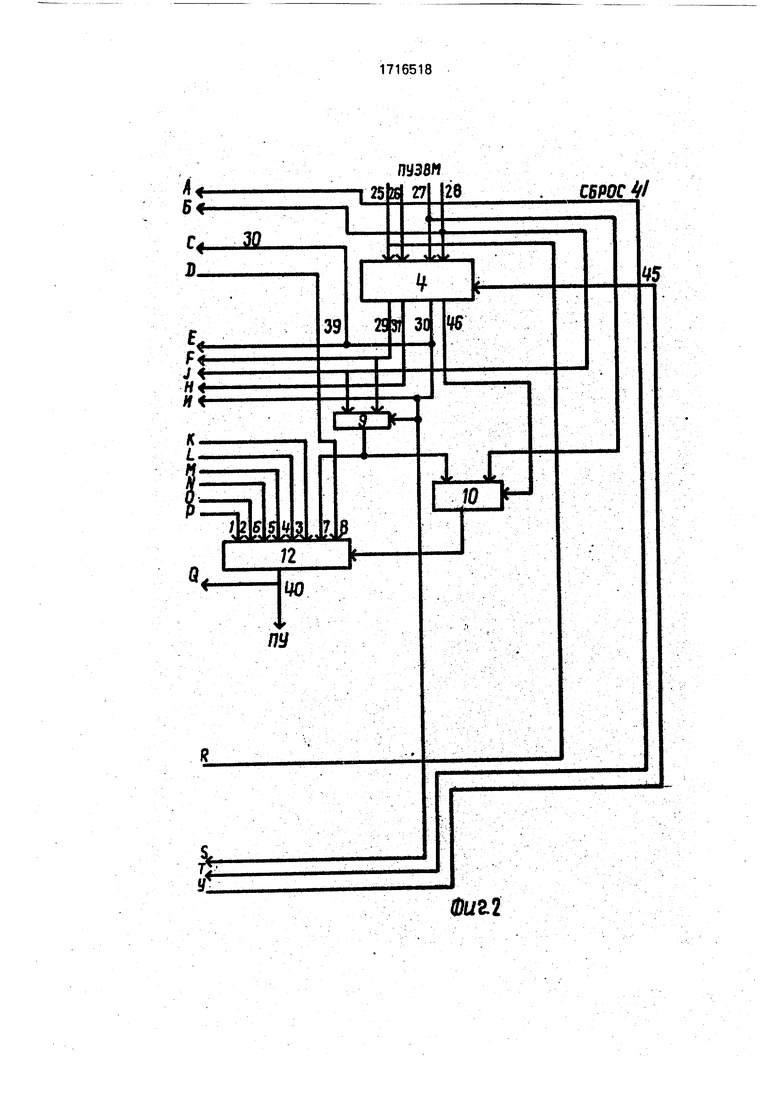

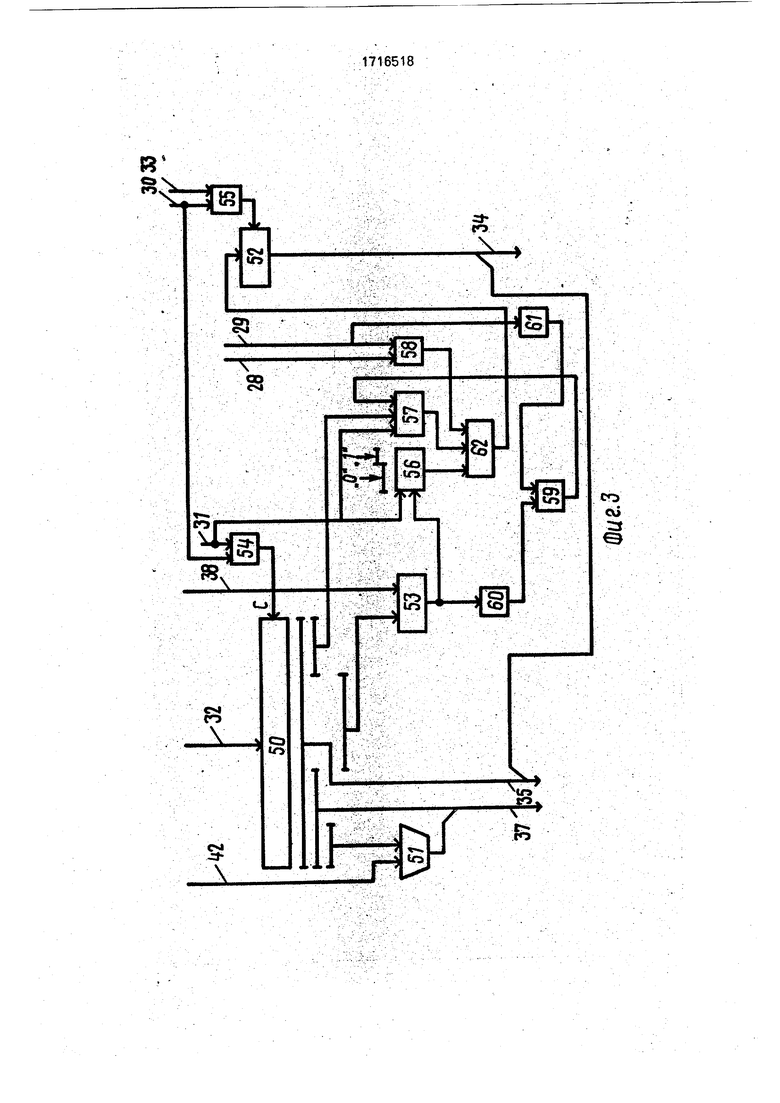

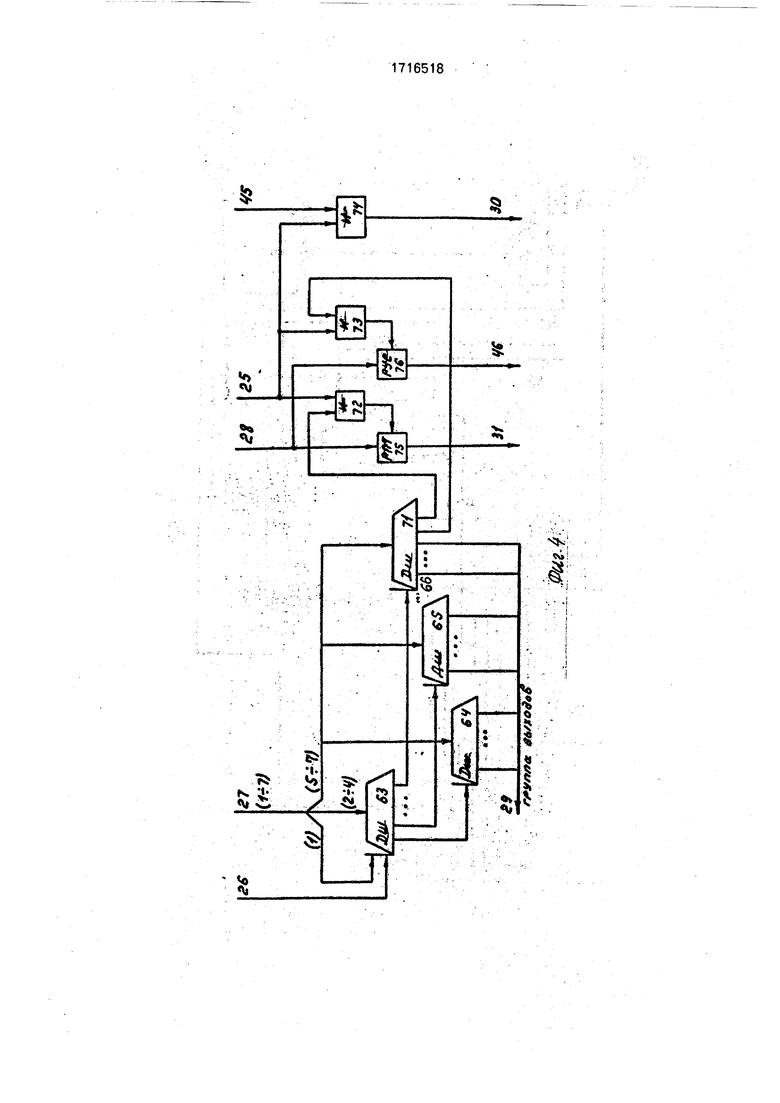

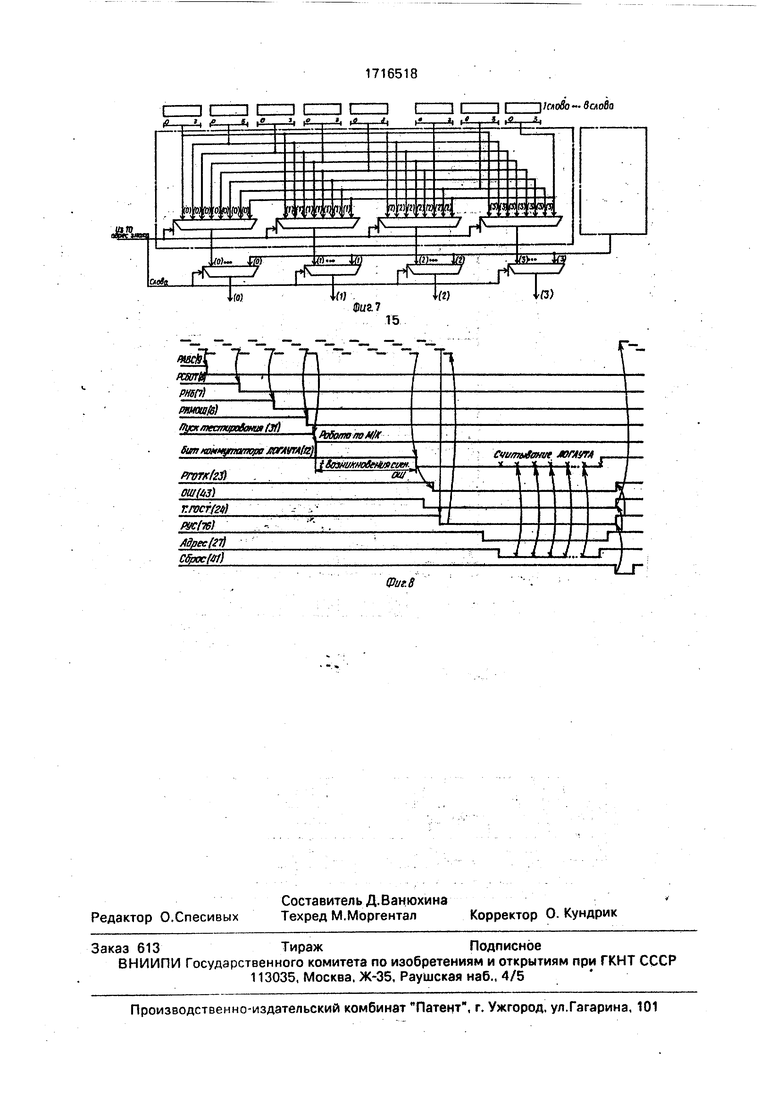

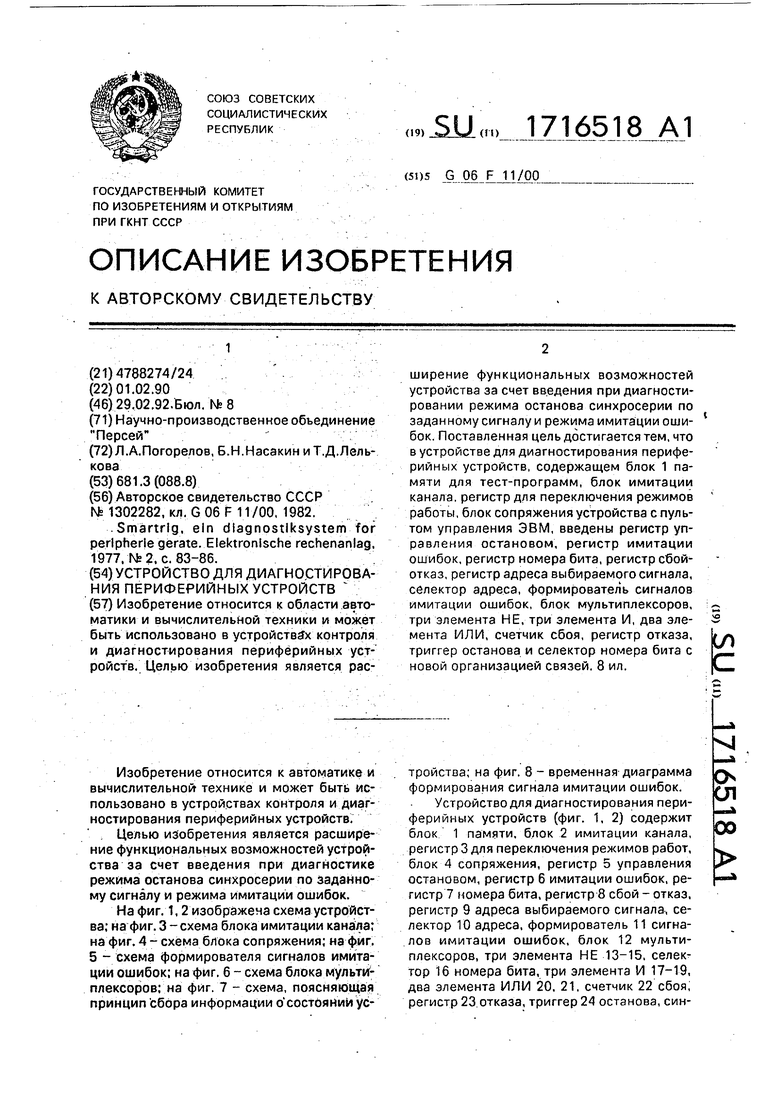

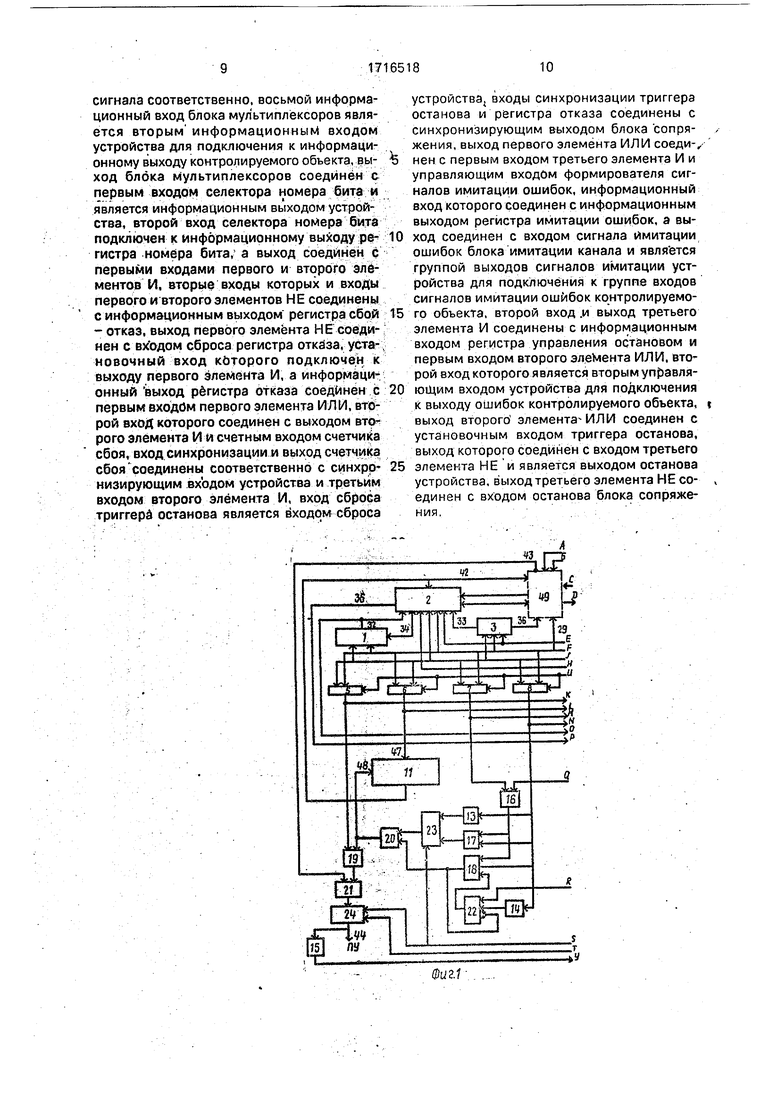

На фиг. 1,2 изображена схема устройства; на фиг. 3 -схема блока имитации канала; на фиг. 4 - схема бяока сопряжения; на фиг. 5 - схема формирователя сигналов имитации ошибок; на фиг. 6 - схема блока мульти1- плексоров; на фиг. 7 - схема, поясняющая принцип сбора информации о состояний устройства; на фиг. 8 - временная диаграмма формирования сигнала имитации ошибок.

Устройство для диагностирования периферийных устройств (фиг. 1, 2) содержит блок 1 памяти, блок 2 имитации канала, регистр 3 для переключения режимов работ, блок 4 сопряжения, регистр 5 управления остановом, регистр 6 имитации ошибок, регистр 7 номера бита, регистр 8 сбой - отказ, регистр 9 адреса выбираемого сигнала, селектор 10 адреса, формирователь 11 сигналов имитации ошибок, блок 12 мультиплексоров, три элемента НЕ 13-15, селектор 16 номера бита, три элемента И 17-19, два элемента ИЛИ 20, 21, счетчик 22 сбоя; регистр 23.отказа, триггер 24 останова, синО

сл

00

хрон.изирующий, первый управляющий адресный и первый информационный входы 25-28, адресный и синхронизирующий выход 29, 30 устройства, выход 31 пуска тестирования блока 4, выход 32 блока 1, управляющий вход 33, выход 34 адреса перехода и информационный выход 35 блока 2, управляющий выход 36, группу выходов ввода - вывода 37 устройства, группу входов ввода - вывода 38 устройства, вторую группу информационных входов 39, первый информационный выход 40, вход 41 сброса, группу выходов 42 сигналов имитации ошибок, второй управляющий вход 43 и выход 44 останова устройства, вход 45 останова и управляющий выход 46 блока 4, информационный и управляющий входы 47, 48 формирователя 11.

Контролируемый объект (периферийное устройство) обозначен позицией 49. Блок 2 имитации канала (фиг. 3) содержит регистр 50 микрокоманд, свертку 51 по модулю два, счетчик 52 микрокоманд, схему 53 сравнения, с первого по шестой элементы И 54-59. первый и второй элементы НЕ 60, 61, эле- мент ИЛИ 62.

Блок 4 сопряжения (фиг. 4) содержит дешифратор 63 слова, с первого по восьмой дешифратор 64-71 знака, с первого по третий элементы И 72-74, регистр 75 пуска тестиро- вания, регистр 76 управления селектором.

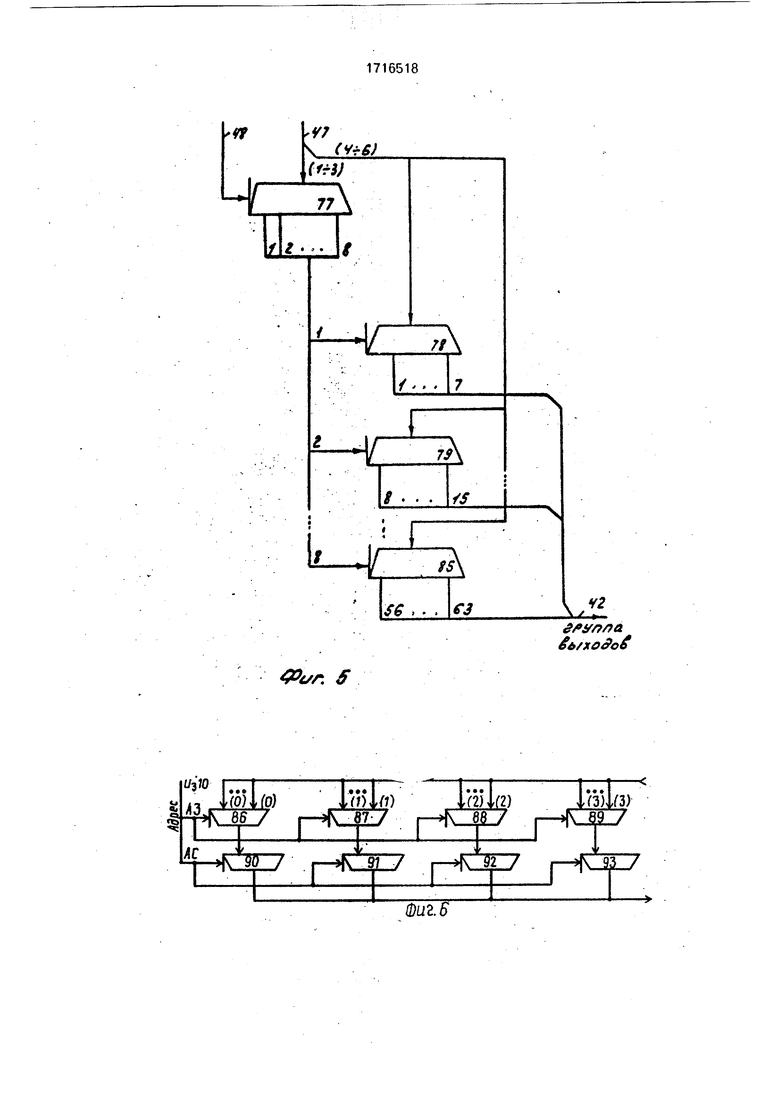

Формирователь-11 сигналов имитации ошибок (фиг. 5) содержит с первого по девятый дешифраторы 77-85.

Блок 12 мультиплексоров (фиг. 6)содер- жит с первого по восьмой мультиплексоры 86-93. Принцип сбора информации о состоянии устройства приведен на фиг. 7.

Блок 1 памяти содержит тест-программы (тесты), на которых осуществляется ди- агностирование устройства.

Регистр 50 микрокоманд блока 2 имитации канала имеет следующий формат:

Информация ИКЭталон.Адрес

Данные Идентификатор Данные Идентификатор перехода

поля - информация ИК данные и информация ИК идентификатор - соответственно сигналы информации и управления стандартного интерфейса ввода - вывода, передаваемые группой выходов 37 устройства в контролируемый объект 49; поля - эталон данные и эталон идентификатор - соответственно сигналы информации и управления стандартного интерфейса ввода - вывода, соответствующие информации и сигналам уп- равления, поступающим по группе входов 38 в блок 2 имитации канала из контролируемого объекта 49; поле - адрес перехода - адрес микрокоманды, на которую нужно перейти после выполнения каждой микрокоманды.

Устройство в режиме Диагностика работает следующим образом.

Управление работой осуществляется с пульта управления. Сигналом Сброс по входу 41 в устройстве устанавливается в исходное состояние триггер 24 останова син- хросерии (фиг. 1).

Взаимодействие пульта управления с предлагаемым устройством обеспечивается выполнением двух операций: передача данных из ПУ в устройство (команда записи); прием данных из устройства в ПУ (команда чтения).

Операция передачи данных в устройство начинается выдачей данных из пульта управления. При наличии сигналов Адрес и Управление, поступающих по адресному 27 и управляющему 26 входам, устройство принимает данные по информационному входу 28 из пульта управления.

Адрес, выдаваемый из ПУ, имеет фор-, мат

где разряд (1)-РР - режим работы: -запись данных из пульта управления в устройство; - чтение информации из устройства в пульт управления; разряды (2- 4)-АС - адрес слова, используемый в режимах записи и чтения; разряды (5-7}-А - адрес знака, используемый в режимах записи и чтения,

Система адресации принята двухуровневая, Первый уровень адресации определяется адресом знака, второй уровень определяется адресом слова, Таким образом, каждый регистр, каждая внутренняя точка схемы, заведенная в блок 12, имеет определенный адрес и создается возможность доступа к любому полубайту из 256 слов (слово - 8 знаков, знак - четыре разряда).

Передача данных из пульта управления в устройство по входу 28 и прием информации из устройства в пульт управления невыходу 40 (фиг. 2) на индикацию осуществляется позначно.

Так как в устройстве реализован принцип микропрограммного управления, то перед началом работы осуществляется запись тестов в блок 1 памяти командами записи с пульта управления через блок 4 сопряжения устройства с пультом управления. Тесты в блоке 1 памяти размещаются последовательно. Каждый тест имеет свой фиксированный адрес в блоке 1 памяти, определяемый счетчиком 52 микрокоманд блока 2 имитации канала (фиг. 3). В тестах,

необходимых для диагностирования, содер жатся входные воздействия и эталонные реакции. Тесты выполняются последовательно, в зависимости от начального адреса, записанного в счетчике 52 микрокоманд и пульта управления. Для диагностирования свертки 51 контроля блока 2 имитации канала (или схем контроля контролируемого объ- екта 49) предлагаемое устройство имитирует сигнал ошибки. Для выработки сигнала имитации ошибки производится запись соответствующей информации в регистр б имитации ошибок, регистр 7 номера бита, регистр 8 сбой - отказ, регистр 9 адреса и регистр 76 блока 4 сопряжения (фиг, 4), открывающего направление адреса на селекторе 10 адреса (фиг. 2) с регистра 9 адреса по командам записи из пульта управления. Далее из пульта управления загружается регистр 75 пуска тестирования (фиг. 4) в состояние единицы. По адресу на входе 34 блока 1, поступающему со счетчика 52 микрокоманд (фиг. 2) выбирается микро- команда из блока 1 памяти, которая записывается в регистр 50 микрокоманды. Начинается обмен по стандартному интерфейсу ввода - вывода блока 2 имитации канала с контролируемым объектом 49 по шинам стандартного сопряжения вводаi .- вывода 38, 37 (фиг. 1). Если поле Эталон регистра 50 микрокоманд сравнивается с данным.и идентификатором, поступающими из контролируемого объекта 49, то на выходе схемы 53 сравнения вырабатывается сигнал, который к счетчику 52 добавляет единицу, и выбирается из блока 1 памяти следующая микрокоманда. Если сравнение поля Эталон регистра 50 микрокоманды с данными и идентификатором не происхо дит, то в счетчик 52 микрокоманд переписывается адрес из поля Адрес перехода регистра 50 микрокоманд и выбирается микрокоманда из блока 1 памяти, адрес которой записан в счетчик 52 микрокоманд. Блок 12 мультиплексоров (фиг. 6) считывает постоянно информацию (4 знака) о состоянии устройства по адресу, записанному в регистре 9 адреса (фиг. 2). В момент появления сигнала на одном из выходов 40 блока 12 (блоком 12 мультиплексоров определяется время появления сигнала имитации ошибки) сигнал через элементы СЕЛ 16 и И 17, если регистр 8 сбой - отказ загружен в состояние Отказ, поступает на РГ 23 отказа и через элемент ИЛИ 20 сформированный сигнал поступает на элемент W19 и на формирователь 11 сигналов имитации ошибок. Элементы СЕЛ. 16, И 18, НЕ 14, счетчик 22 сбоя, если регистр 8 сбой - отказ загружен в состояние Сбой. Сигнал ими

тации ошибок с выхода формирователя 11 сигналов имитации ошибок поступает на вход свертки 51 (фиг, 3) блока 2 имитации канала (или в контролируемый объект 49 на входы сверток и контролируемых элементов по входу 42). С выхода свертки 51 формируется неверный контрольный разряд, т.е. вносится ошибка в стандартный интерфейс ввода - вывода на тест-программах. Контро0 лируемый объект 49 фиксирует ошибку и выдает с выхода 43 сигнал об ошибке на второй вход элемента ИЛИ 21 (фиг. 1), через который триггер 24 устанавливается в состояние 1 и через элемент НЕ15 по выходу

5 45 (фиг, 1), элемент И 74,блока 4 сопряжения по выходу 30 (фиг. 4) и элемент И 55 (фиг. 3) происходит останов синхросерии счетчика 52 микрокоманд (фиг. 3).

Останов синхросерии происходит и в

0 контролируемом объекте 49. Счетчик 52 микрокоманд далее не считает, новая мик- t рокоманда из блока 1 памяти не выбирается. При формирований сигналов имитации ошибок регистр 5 управления остановом

5 (фиг. 1) должен быть загружен в состояние О для того, чтобы синхросерия была бы . остановлена только после формирования ошибки в контролируемом объекте 49. С выхода триггера 24 останова сигнал останова

0 устройства по выходу 44 поступает в пульт управления, который настраивает программу на считывание логаута - информацию состояния устройства. Сначала командой записи (адрес с выхода ДШ 71) регистр 76

5 (фиг. 4) управления селектором устанавливается в состояние, соответствующее адресу и информации, поступающим с пульта управления, селектор 10 адреса переключается на направление с пульта управления,

0 затем пульт управления последовательно выдает адрес (команды чтения), который через селектор 10 адреса (фиг. 2) поступает на адресный вход блока 12 мультиплексоров и с выходов блока 12 информация поступает

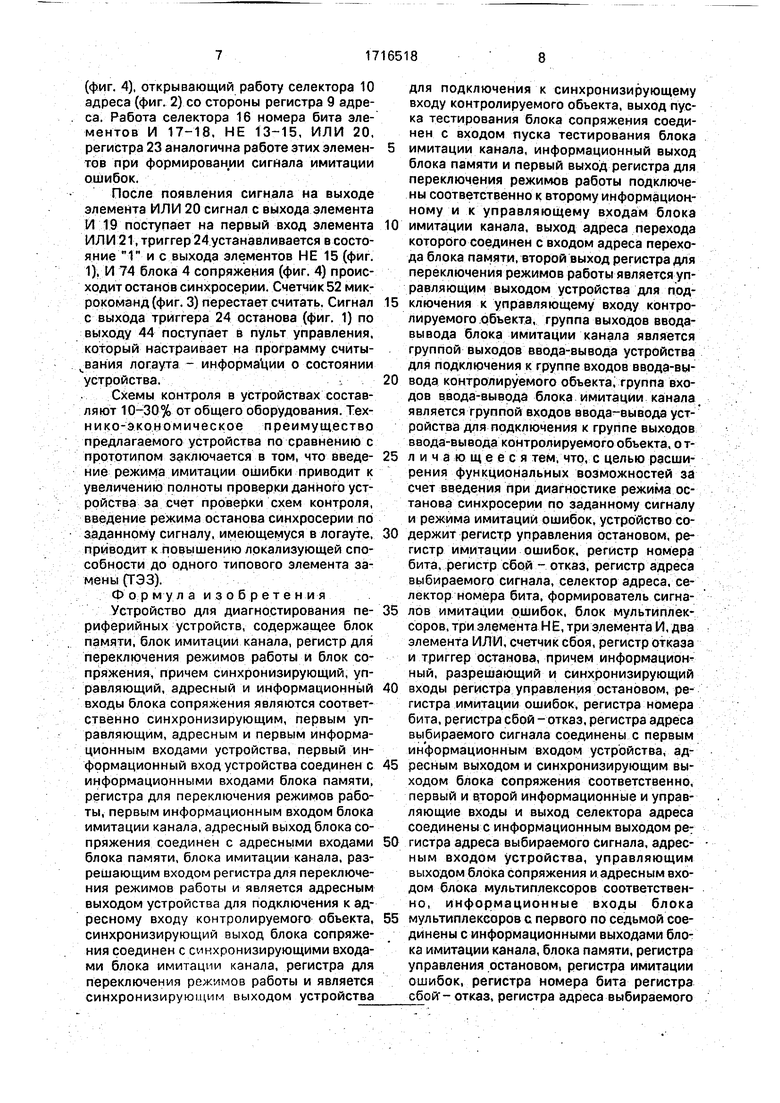

5 в пульт управления. Работа по формированию сигналов имитации ошибок, последовательность загрузки регистров устройства и реакция приведены на временной диаграмме, представленной на фиг. 8.

0 При задании режима останова по заданному сигналу с пульта управления командной записи загружается регистр 5 управления остановом (адрес по выходу группы 20 выходов фиг. 4) в состояние 1,

5 регистр 6 имитации ошибки загружается в состояние О, чтобы формирователь 11 сигналов имитации ошибок не выдавал сигналы имитации ошибок. Командами записи с пульта управления загружаются регистры 7-9 (фиг. 2), регистр 76 блока 4 сопряжения

(фиг. 4), открывающий работу селектора 10 адреса (фиг. 2) со стороны регистра 9 адреса. Работа селектора 16 номера бита элементов И 17-18, НЕ 13-15, ИЛИ 20, регистра 23 аналогична работе этих элементов при формировании сигнала имитации ошибок.

После появления сигнала на выходе элемента ИЛИ 20 сигнал с выхода элемента И 19 поступает на первый вход элемента ИЛИ 21, триггер 24устанавливается в состояние 1 и с выхода элементов НЕ 15 (фиг. 1), И 74 блока 4 сопряжения (фиг. 4) происходит останов синхросерии. Счетчик 52 микрокоманд (фиг. 3) перестает считать. Сигнал с выхода триггера 24 останова (фиг. 1} по выходу 44 поступает в пульт управления, который настраивает на программу считы- вания логаута - информации о состоянии устройства.:

Схемы контроля в устройствах составляют 10-30% от общего оборудования. Технико-экономическое преимущество предлагаемого устройства по сравнению с прототипом заключается в том, что введение режима имитации ошибки приводит к увеличению полноты проверки данного устройства за счет проверки схем контроля, введение режима останова синхросерии по заданному сигналу, имеющемуся в логауте, приводит к повышению локализующей способности до одного типового элемента замены (ТЭЗ).

Ф о р м у л а и з о б р ет е н и я

Устройство для диагностирования периферийных устройств, содержащее блок памяти, блок имитации канала, регистр для переключения режимов работы и блок сопряжения, причем синхронизирующий, управляющий, адресный и информационный входы блока сопряжения являются соответственно синхронизирующим, первым управляющим, адресным и первым информационным входами устройства, первый информационный вход устройства соединен с информационными входами блока памяти, регистра для переключения режимов работы, первым информационным входом блока имитации канала, адресный выход блока сопряжения соединен с адресными входами блока памяти, блока имитации канала, разрешающим входом регистра для переключения режимов работы и является адресным выходом устройства для подключения к адресному входу контролируемого объекта, синхронизирующий выход блока сопряжения соединен с синхронизирующими входами блока имитации канала, регистра для переключения режимов работы и является синхронизирующим выходом устройства

для подключения к синхронизирующему входу контролируемого объекта, выход пуска тестирования блока сопряжения соединен с входом пуска тестирования блока

имитации канала, информационный выход блока памяти и первый выход регистра для переключения режимов работы подключены соответственно к второму информационному и к управляющему входам блока

0 имитации канала, выход адреса перехода которого соединен с входом адреса перехода блока памяти, второй выход регистра для переключения режимов работы является управляющим выходом устройства для под5 ключения к управляющему входу контролируемого /объекта, группа выходов ввода- вывода блока имитации канала является группой выходов ввода-вывода устройства для подключения к группе входов ввода-вы0 вода контролируемого объекта, группа входов ввода-вывода блока имитации канала является группой входов ввода-вывода устройства для подключения к группе выходов ввода-вывода контролируемого объекта, о т5 л и ч а ю щ е ее я тем, чтр, с целью расширения функциональных возможностей за счет введения при диагностике режима останова синхросерии по заданному сигналу и режима имитаций ошибок, устройство со0 держит регистр управления остановом, регистр имитации ошибок, регистр номера бита, регистр сбой - отказ, регистр адреса выбираемого сигнала, селектор адреса, селектор номера бита, формирователь сигна5 лов имитации ошибок, блок мультиплексоров, три элемента НЕ, три элемента И, два элемента ИЛИ, счетчик сбоя, регистр отказа и триггер останова, причем информацион ный, разрешающий и синхронизирующий

0 входы регистра управления остановом, регистра имитации ошибок, регистра номера бита, регистра сбой - отказ, регистра адреса выбираемого сигнала соединены с первым информационным входом устройства, ад5 ресным выходом и синхронизирующим выходом блока сопряжения соответственно, первый и второй информационные и управляющие входы и выход селектора адреса соединены с информационным выходом ре:

0 гистра адреса выбираемого сигнала, адресным входом устройства, управляющим выходом блока сопряжения и адресным входом блока мультиплексоров соответственно, информационные входы блока

5 мультиплексоров с первого по седьмой соединены с информационными выходами блока имитации канала, блока памяти, регистра управления остановом, регистра имитации ошибок, регистра номера бита регистра отказ, регистра адреса выбираемого

сигнала соответственно, восьмой информационный вход блока мультиплексоров является вторым информационным входом устройства для подключения к информационному выходу контролируемого объекта, вы- ход блока мультиплексоров соединён с первым входом селектора номера бита и является информационным выходом устройства, второй вход селектора номера бита подключен к информационному выходу ре- гистра номера бита, а выход соединен с первыми входами первого и второго элементов И, вторые входы которых и входы первого и второго элементов НЕ соединены с информационным выходом регистра сбой - отказ, выход первого элемента НЕ соединен с вх одом сброса регистра откёза, установочный вход которого подключен к выходу первого элемента И, а информационный выход регистра отказа соединён с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом рого элемента И и счетным входом счетчика сбоя, вход синхронизации и выход счетчика сбоя соединены соответственно с синхрр- низирующим .входом устройства и третьим входом второго элемента И, вход сброса триггера останова является входом сброса

устройства{ входы синхронизации триггера останова и регистра отказа соединены с синхронизирующим выходом блока сопряжения, выход первого элемента ИЛИ соединен с первым входом третьего элемента И и управляющим входом формирователя сигналов имитации ошибок, информационный вход которого соединен с информационным выходом регистра имитации ошибок, а выход соединен с входом сигнала имитации ошибок блока имитации канала и является группой выходов сигналов имитации устройства для подключения к группе входов сигналов имитации ошибок контролируемого объекта, второй вход .и выход третьего элемента И соединены с информационным входом регистра управления остановом и первым входом второго элемента ИЛИ, второй вход которого является вторым управляющим входом устройства для подключения к выходу ошибок контролируемого объекта, выход второго1 элемента- ИЛИ соединен с установочным входом триггера останова, выход которого соединен с входом третьего элемента НЕ и является выходом останова устройства, выход третьего элемента НЕ соединен с входом останова блока сопряжения.:

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1636845A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU970475A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах контроля и диагностирования периферийных устройств. Целью изобретения является расширение функциональных возможностей устройства за счет введения при диагностировании режима останова синхросерии по заданному сигналу и режима имитации ошибок. Поставленная цель достигается тем. что в устройстве для диагностирования периферийных устройств, содержащем блок 1 памяти для тест-программ, блок имитации канала, регистр для переключения режимов работы, блок сопряжения устройства с пультом управления ЭВМ, введены регистр управления остановом, регистр имитации ошибок, регистр номера бита, регистр сбой- отказ, регистр адреса выбираемого сигнала, селектор адреса, формирователь сигналов имитации ошибок, блок мультиплексоров, три элемента НЕ, три элемента И, два элемента ИЛИ, счетчик сбоя, регистр отказа, триггер останова и селектор номера бита с новой организацией связей. 8 ил. :Ё

Фиг2

Ј

-Ь .0ii

rN

iw BJ a a w

H

f| t. (Ц

±rЈ

% $ WiL .. J I3: ™

Јj

м- m

M- Ш

GuAt

f)

ДОД7/

|/мо8о -ваоЙо

±rЈ

Јj

) J/5 1

ry

Фиг 7

W)

15

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Smartrlg | |||

| ein dlagnostiksystenv for perlpherie gerate | |||

| Elektronische rechenanlag, 1977 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| c | |||

| Пуговица | 0 |

|

SU83A1 |

Авторы

Даты

1992-02-28—Публикация

1990-02-01—Подача