первьй выход которого соединен с второй выходной шиной устройства, а второй выход соединен с

вторым входом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения запаздывающих функций | 1984 |

|

SU1168973A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1561075A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182546A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| Функциональный генератор | 1983 |

|

SU1141427A1 |

| Гибридное вычислительное устройство | 1983 |

|

SU1113819A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

ФОРМИРОВАТЕЛЬ СЛОЖНЫХ СИГНА Ш)В, содержащий первый элемент И, первьй счетчик импульсов, запоминающий блок, цифроаналоговый преобразователь, причем первый вход первого элемента И соединен с первой входной шиной устройства, выход первого счетчика импульсов соединен с входом запоминающего блока, выход цифроаналогового преобразователя соединен с первой .выходной шиной устройства, отлич ающий с я тем, что, с целью снижения аппаратурных затрат путем экономии, уменьшения, объема памяти, в него введены второй и третий счетчики импульсов, цифровой элемент сравнения, демультиплексор, первый и второй формирователи импульсов, второй, третий, четвертый и пятый элементы И, элемент ИЛИ, причем выход первого элемента И через первый формирователь импульсов соединен с первым входом первого счетчика импульсов, первьй выход запоминающего блока соединен с первым входом второго элемента И, второй выход соединен с первым входом третьего элемента И, второй вход которого соединен с вторым входом второго элемента И,с первыми входами четвертого и пятого элементов И и с первой входной шиной устройства, выход второго элемента И соединен с первым входом второго счет чика импульсов, второй вход которого соединен с выходом третьего элемента И, а выход четвертого элемента И соединен с первым входом третьего счетчика импульсов, второй вход которого соединен с вторым входом первого счетчика импульсов, выходом элемента i ИЛИ и третьим входом второго счетчика импулБсов, выход которого соединен (Л с входом цифроаналогового преобразос вателя, при этом второй вход пятого элемента И соединен с третьим выходом запоминающего блока, четвертый выход которого соединен с первым входом цифрового элемента сравнения, первый выход которого соединен с третьим ел входом пятого элемента И, выход кооэ торого через ВТОРОЙ формирователь имОд пульсов соединен с первым входом ф демультиплексора, а второй вход цифрового элемента сравнения соединен с выходом третьего счетчика импульсов, третий вход которого соединен с выходом первого формирователя импульсов, при этом второй вход первого элемента И соединен с первым выходом цифрового элемента сравнения, второй выход которого соединен с вторым входом четвертого элемента И, а первый вход элемента ИЛИ .соединен с второй входной шиной устройства, третья входная шина соединена с вторым входом демультиплексора.

I

Изобретение относится к импульсной технике и может найти применение в аналого-цифровых системах и устройствах автоматики.

Известен формирователь сложного сигнала, содержащий генератор тактовых импульсов, Счетчики импульсов, запоминающий сумматор, ЦАП и блок управления ClJ.

Недостатком известного устройства является сложность, связанная с большим объемом памяти запоминающего блока,

Наиболее близким к предлагаемому является формирователь сложных сигналов, содержащий элемент И, счетчик импульсов, запоминающий блок, цифроаналоГовый преобразователь, причем первый вход элемента И соединен с первой входной шиной устройства, выход цифроаналогового преобразователя соединен с выходной шиной устройства, выход счетчика соединен с входом запоминающего блока, выход запоминающего блока соединен с входом цифроаналогового преобразователя вторая входная шина устройства соединена с вторым входом элемента И, выход которого соединен с входом счетчика импульсов L2J.

Недостатком известного устройства является его сложность, обусловленная большой информационной емкостью запоминаищего блока, т.е. большим объемом памяти.

Цель изобретения - снижение аппаратурньпс затрат путем экономии, уменьшение объема памяти.

Поставленная цель достигается тем, что в формирователь сложных сигналов, содержащий первый элемент И, первый счетчик импульсов, запоминающий блок, цифроаналоговый преобразователь, причем первый вход первого элемента И соединен с первой входной шиной устройства, выход первого счетчика импульсов соединен с входом запоминающего блока, выход

цифроаналогового преобразователя соединен с первой выходной шиной устройства, дополнительно введены второй и третий счетчики импульсов, цифровой элемент сравнения, демультиплексор, первый и второй формирователи импульсов, второй, третий, четвертый и пятый элементы И, элемент ИЛИ, причем выход первого элемента И через первый формирователь импульсов соединен с первым входом первого счетчика импульсов, первый выход запоминающего блока соединен с первым входом второго элемента И, второй выход соединен с первым входом третьего элемента И, второй вход которого соединен с вторым входом второго злемента И, с первьми входами четвертого и пятого элементов И и с первой входной шиной устройства, выход второго элемента И соединен с первым входом второго счетчика импульсов, второй вход которого соединен с выходом третьего элемента И, а выход четвертого элемента И соединен с первым входом третьего счетчика импульсов, второй вход которого соединен с вторым входом первого счетчика импульсов, выходом элемента ИЛИ и третьим входом второго счетчика импульсов, выход которого соединен с входом цифроаналогового преобразователя, при этом второй вход пятого элемента И соединен с третьим выходом запоминающего блока, четвертый выход которого соединен с первым входом цифрового элемента сравнения, первый выход которого соединен с третьим входом пятого элемента И, выход которого через второй формирователь импульсов соединен с первым входом демультиплексора, а второй вход цифрового элемента сравнения соединен с выходом третьего счетчика импульсов, третий вход которого соед.нен с выходом первого формирователя импульсов, при этом второй вход первого элемента И соединен с первым

3

выходом цифрового элемента сравнения второй вьрсод которого соединен с вторьм вгодом четвертого элемента И а первьш вход элемента ИЛИ соединен с второй входной шиной устройства, третья входная шина соединена с вторым входом демультиплексора, первый выход которого соединен с второй выходной шиной устройства, а второй выход соединен с вторым входом элемента ИЛИ.

В запоминающем блоке хранятся значения приращений функций, а не Ьначения самой функции, что сокращает число разрядов запоминающего блока и, следовательно, уменьшает его информационную емкость.

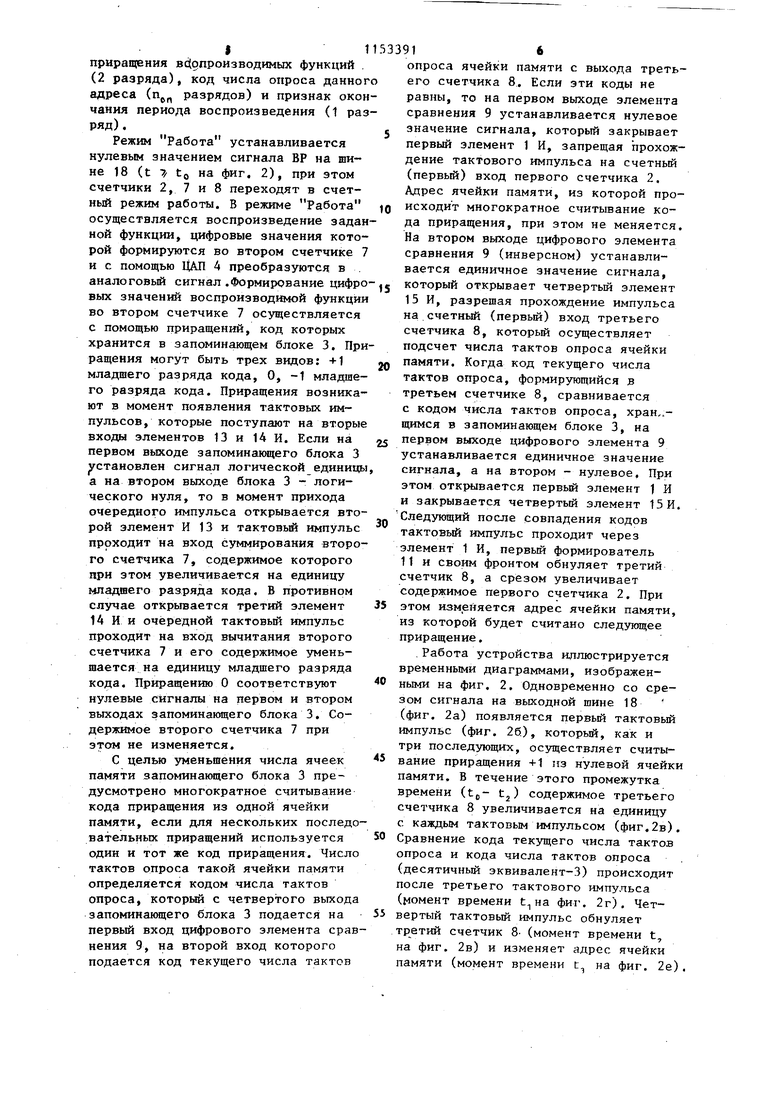

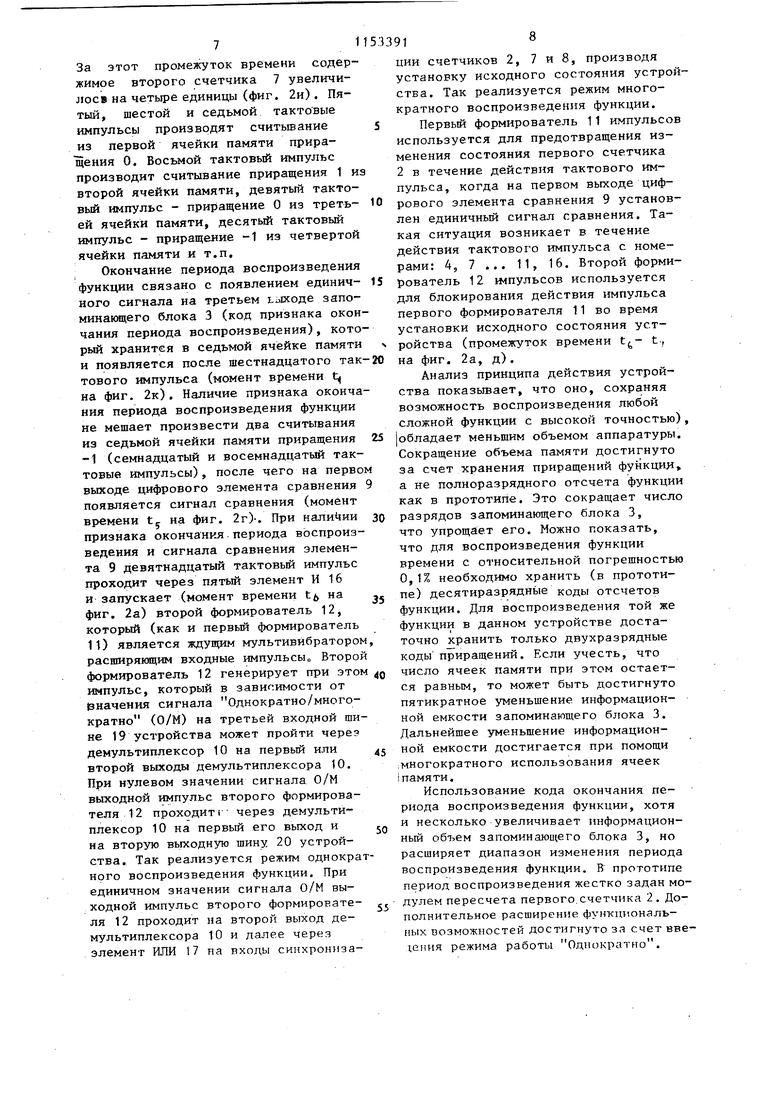

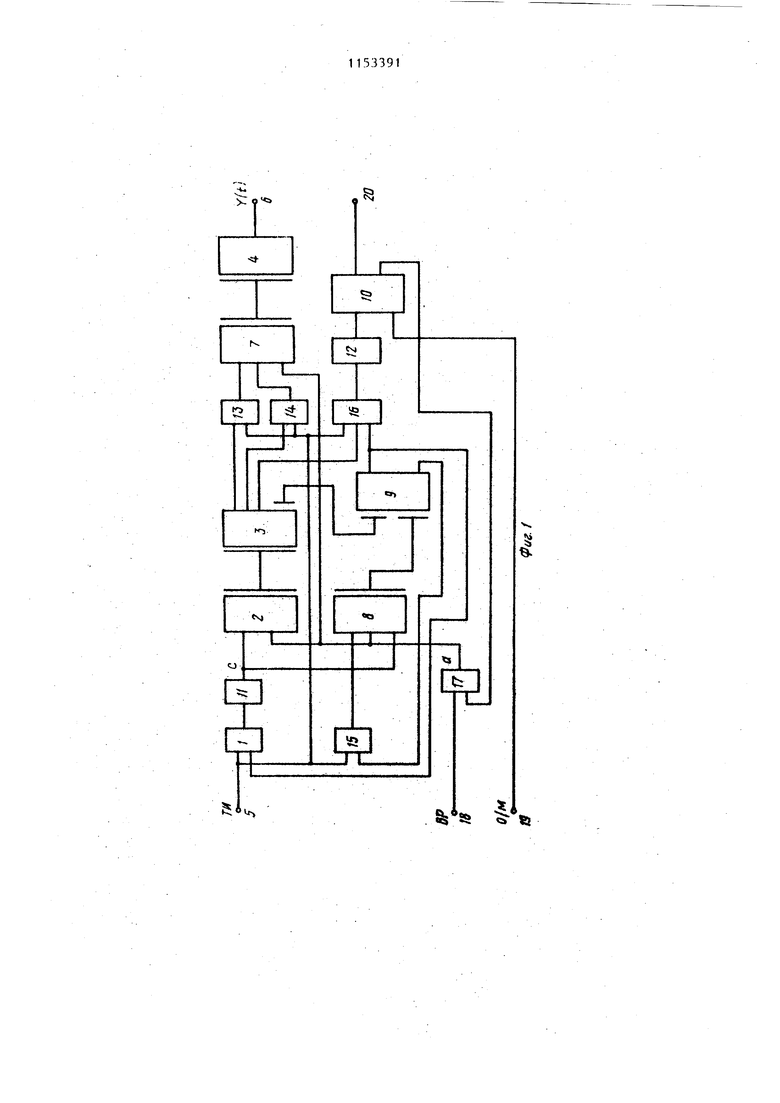

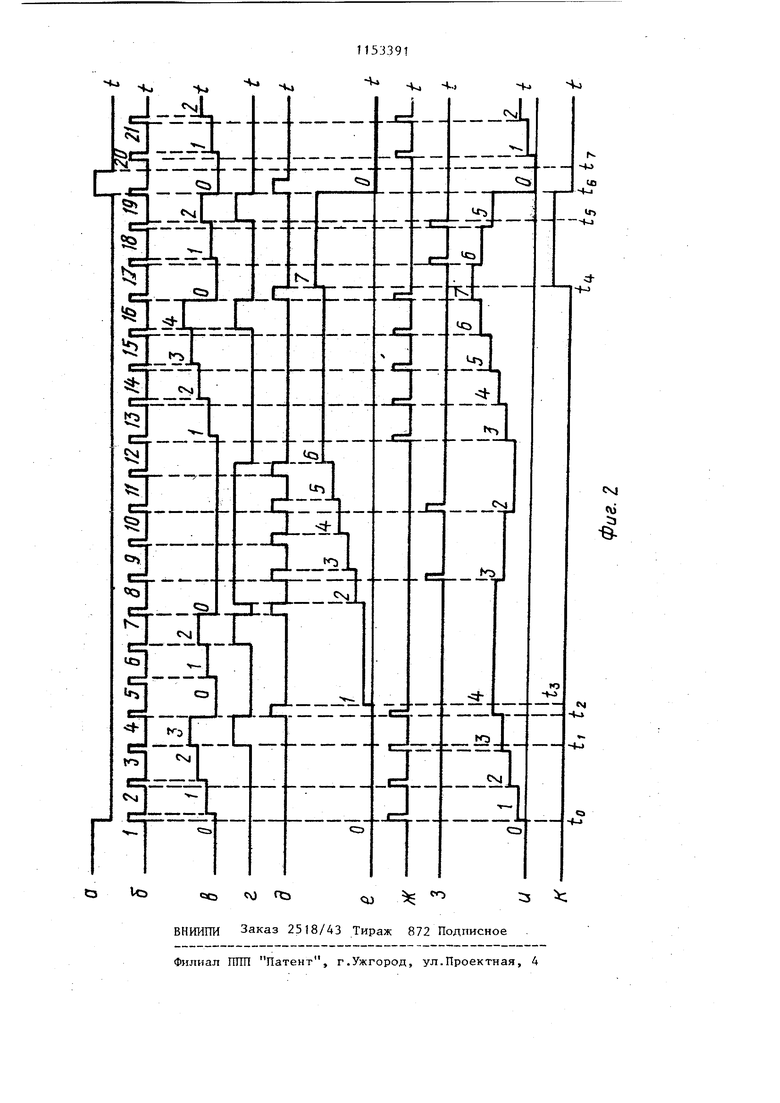

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 временные диаграммы, описывакядие его работу.

Формирователь сложных сигналов, содержит первый элемент 1 И, первый счетчик 2 импульсов, запоминающий блок 3, цифроаналоговый преобразователь (ЦАП) 4, причем первый вход первого элемента 1 И соединен с первой входной шиной 5 устройства, выход первого счетчика 2 соединен с входом запоминающего блока 3, выход ЦАП 4 соединен с первой выходной шиной 6 устройства, второй и третий счетчики 7 и 8 импульсов, цифровой элемент сравнения 9, демультиплексор 10, первый и второй формирователи 11 и 12 импульсов, второй, третий, четвертый и пятый элементы 13-16 И, элемент 17 ИЛИ, причем выход элемента 1 И через первый формирователь 11 сигнала соединен с первым входом первого счетчика 2, первый выход запоминающего блока 3 соединен с первым входом второго элемента 13 И, второй выход запоминающего блока 3 соединен с первым входом третьего элемента 14 И, второй вход которого соединен с вторым входом второго элемента 13 И и с первой входной шиной 5 устройства, выход второго элемента 13 И соединен с первым входом второго счетчика 7, второй вход которого соединен с выходом третьего элемента И 14, выход четвертого элемента 15 И соединен с первым входом третьего счетчика 8, второй вход которого соединен с вто:рым входом первого счетчика 2, уэыходом элемента ИЛИ 17 и третьим входом втоV33914

рого счетчика 7, выход которого соединен с входом 11АП 4, первьш вход пятого элемента 16 И соединен с пер.вой входной шиной 5 устройства, второй вход пятого элемента 16 И соединен с третьим выходом запоминающего блока 3, четвертый выход которого соединен с первым входом цифрового элемента сравнения 9, первый выход которого соединен с третьим входом

пятого элемента 16 И, вьпсод которого через второй формирователь 12 импульсов соединен с первым входом демуль- типлексора 10, второй вход элемента сравнения 9 соединен с выходом третьего счетчика 8, третий вход которого соединен с выходом первого формирователя 11 импульсов, первьй ч вход четвертого элемента 15 И соединен с первой входной шиной 5 устройства, второй вход первого элемента 1 И соединен с первым выходом цифрового элемента сравнения 9, второй выход которого соединен с вторым входом четвертого элемента 15 И, первый вход элемента 17 ИЛИ соединен с второй входной шиной 18 устройства, третья входная шина 19 соединена с вторым входом демультиплексора 10, первый выход которого соединен с второй выходной шиной 20 устройства, второй выход демультиплексора 10 соединен с вторым входом элемента 17 ИЛИ.

Первые входы счетчиков 2, 7 и 8 являются счетными (входами сложения), вторые входы первого счетчика 2 и третьего счетчика 8 являются входами синхронизации, второй вход второго счетчика 7 является входом вычитания, а третий вход является входом синхронизации, третий вход третьего счетчика В является входом обнуления. При этом единичное значение сигнала на входах синхронизации счетчиков 2, 7 и 8 разрешает занесение информации с установочных входов этих счетчиков (не показаны).

На установочный вход второго счетчика 7 подается код начального значе-

ния воспроизводимой функции (на фиг.2 это значение принято нулевьм, t tjj). Установочный вход третьего счетчика 8 соединен с общей шиной устройства, поэтому при единичном сигнале на входе синхронизации этот счетчик обнуляется (фиг. 2).

-В запоминающий блок 3 предварительно заносится по каждому адресу: код S приращения вс(дпроизводимых функций (2 разряда), код числа опроса данно адреса (п разрядов) и признак око чания периода воспроизведения (1 ра ряд). Режим Работа устанавливается нулевым значением сигнала ВР на шине 18 (t 7/ to на фиг. 2), при этом счетчики 2, 7 и 8 переходят в счетный режим работы. В режиме Работа осуществляется воспроизведение зада ной функции, цифровые значения кото рой формируются во втором счетчике и с помощью ЦАП 4 преобразуются в аналоговый сигнал .Формирование цифр вых значений воспроизводимой функци во втором счетчике 7 осуществляется с помощью приращений, код которых хранится в запоминающем блоке 3. Пр ращения могут быть трех видов: +1 младшего разряда кода, О, -1 младше го разряда кода. Приращения возника ют в момент появления тактовьк импульсов, которые поступают на вторы входы элементов 13 и 14 И. Если на первом выходе запоминающего блока 3 гстановлен сигнал логической единиц а на втором выходе блока 3 - логического нуля, то в момент прихода очередного импульса открывается вто рой элемент И 13 и тактовьй импульс проходит на вход суммирования второ го счетчика 7, содержимое которого при этом увеличивается на единицу младшего разряда кода. В противном случае открьгаается третий элемент 14 И и очередной тактовый импульс проходит на вход вычитания второго счетчика 7 и его содержимое уменьшается на единицу младшего разряда кода. Приращению О соответствуют нулевые сигналы на первом и втором выходах запоминающего блока 3. Содержимое второго счетчика 7 при этом не изменяется, С целью уменьшения числа ячеек памяти запоминающего блока 3 предусмотрено многократное считывание кода приращения из одной ячейки памяти, если для нескольких последо вательных приращений используется один и тот же код приращения. Число тактов опроса такой ячейки памяти определяется кодом числа тактов опроса, который с четвертого выхода запоминающего блока 3 подается на первый вход цифрового элемента срав нения 9, на второй вход которого подается код текущего числа тактов 16 опроса ячейки памяти с выхода третьего счетчика 8. Если эти коды не равны, то на первом выходе элемента сравнения 9 устанавливается нулевое значение сигнала, который закрывает первый элемент 1 И, запрещая прохождение тактового импульса на счетный (первьй) вход первого счетчика 2. Адрес ячейки памяти, из которой происходит многократное считывание кода приращения, при этом не меняется. На втором выходе цифрового элемента сравнения 9 (инверсном) устанавливается единичное значение сигнала, который открывает четвертый элемент 15 И, разрешая прохождение импульса на счетный (первый) вход третьего счетчика 8, который осуществляет подсчет числа тактов опроса ячейки памяти. Когда код текущего числа тактов опроса, формирующийся в третьем счетчике 8, сравнивается с кодом числа тактов опроса, хран,.щимся в запоминающем блоке 3, на первом выходе цифрового элемента 9 устанавливается единичное значение сигнала, а на втором - нулевое. При этом открывается первьй элемент 1 И и закрывается четвертый элемент 15 И. Следующий после совпадения кодов тактовый импульс проходит через элемент 1 И, первый формирователь 11 и своим фронтом обнуляет третий счетчик 8, а срезом увеличивает содержимое первого счетчика 2. При этом изменяется адрес ячейки памяти, из которой будет считано следующее приращение. .Работа устройства иллюстрируется временными диаграммами, изображенными на фиг. 2. Одновременно со срезом сигнала на выходной шине 18 (фиг. 2а) появляется первый тактовый импульс (фиг. 26), которьй, как и три последующих, осуществляет считывание приращения +1 из нулевой ячейки памяти. В течение этого промежутка времени (tp- tj) содержимое третьего счетчика 8 увеличивается на единицу с каждьм тактовым импульсом (фиг.2в). Сравнение кода текущего числа тактов опроса и кода числа тактов опроса (десятичный эквивалент-3) происходит после третьего тактового импульса (момент времени t на фит . 2г) . Четвертый тактовый импульс обнуляет третий счетчик 8- (момент времени t, на фиг. 2в) и изменяет адрес ячейки памяти (момент времени с на фиг. 2е). За этот промежуток времени содер жимое второго счетчика 7 увеличилосв на четыре единицы (фиг. 2и) . Пятый, шестой и седьмой тактовые импульсы производят считьшание из первой ячейки памяти приращения 0. Восьмой тактовый импульс производит считывание приращения 1 второй ячейки памяти, девятый тактовый импульс - приращение О из третьей ячейки памяти, десятый тактовый импульс - приращение -1 из четвертой ячейки памяти и т.п. Окончание периода воспроизведения функции связано с появлением единичного сигнала на третьем ь лходе запоминающего блока 3 (код признака окон чания периода воспроизведения), кото рый хранится в седьмой ячейке памяти и появляется после шестнадцатого так тового импульса (момент времени Ц на фиг. 2к). Наличие признака оконча ния периода воспроизведения функции не мешает произвести два считывания из седьмой ячейки памяти приращения -1 (семнадцатый и восемнадцатый тактовые импульсы), после чего на перво выходе цифрового элемента сравнения появляется сигнал сравнения (момент времени t на фиг. 2г)-. При признака окончания периода воспроизведения и сигнала сравнения элемента 9 девятнадцатый тактовый импульс проходит через пятый элемент И 16 и запускает (момент времени t на фиг. 2а) второй формирователь 12, который (как и первый формирователь 11) является ждущим мультивибратором расширяющим входные импульсы Второй формирователь 12 генерирует при этом импульс, который в зависимости от значения сигнала Однократно/многократно (0/М) на третьей входной тине 19 устройства может пройти через демультиплексор 10 на первый или второй выходы демультиплексора 10. При нулевом значении сигнала 0/М выходной импульс второго формирователя 12 проходит г через демультиплексор 10 на первый его выход и на вторую выходную шину 20 устройства. Так реализуется режим однократ ного воспроизведения функции. При единичном значении сигнала 0/М выходной импульс второго формирователя 12 проходит на второй выход демультиплексора 10 и далее через элемент ИЛИ 17 на входы синхрониза918ции счетчиков 2, 7 и 8, производя установку исходного состояния устройства. Так реализуется режим многократного воспроизведения функции. Первый формирователь 11 импульсов используется для предотвращения изменения состояния первого счетчика 2 в течение действия тактового импульса, когда на первом выходе цифрового элемента сравнения 9 установлен единичный сигнал сравнения. Такая ситуация возникает в течение действия тактового импульса с номерами: 4, 7 ... 11, 16. Второй формирователь 12 импульсов используется для блокирования действия импульса первого формирователя 11 во время установки исходного состояния устройства (промежуток времени t, на фиг. 2а, д). Анализ принципа действия устройства показывает, что оно, сохраняя возможность воспроизведения любой сложной функции с высокой точностью), обладает меньшим объемом аппаратуры. Сокращение объема памяти достигнуто за счет хранения приращений функция, а не полноразрядного отсчета функции как в прототипе. Это сокращает число разрядов запоминающего блока 3, что упрощает его. Можно показать, что для воспроизведения функции времени с относительной погрешностью О, 1% необходимо хранить (в прототипе) десятиразрядные коды отсчетов функции. Для воспроизведения той же функции в данном устройстве достаточно зсранить только двухразрядные кодыприращений. Если учесть, что число ячеек памяти при этом остается равным, то может быть достигнуто пятикратное уменьшение информационной емкости запоминающего блока 3. Дальнейшее уменьшение информационной емкости достигается при помощи многократного использования ячеек памяти. Использование кода окончания периода воспроизведения функции, хотя и несколько увеличивает информационный объем запоминающего блока 3, но расширяет диапазон изменения периода воспроизведения функции. В прототипе период воспроизведения жестко задан модулем пересчета первого.счетчика 2. Дополнительное расширение функциональных возможностей достигнуто за счет введения режима работы Однократно.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Генератор ступенчатого напряжения | 1978 |

|

SU729824A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Использование ЗУПВ и ЦАП в генераторе сложных сигналов | |||

| - Электроника, 1978, № t, с | |||

| Спускная труба при плотине | 0 |

|

SU77A1 |

Авторы

Даты

1985-04-30—Публикация

1983-11-09—Подача