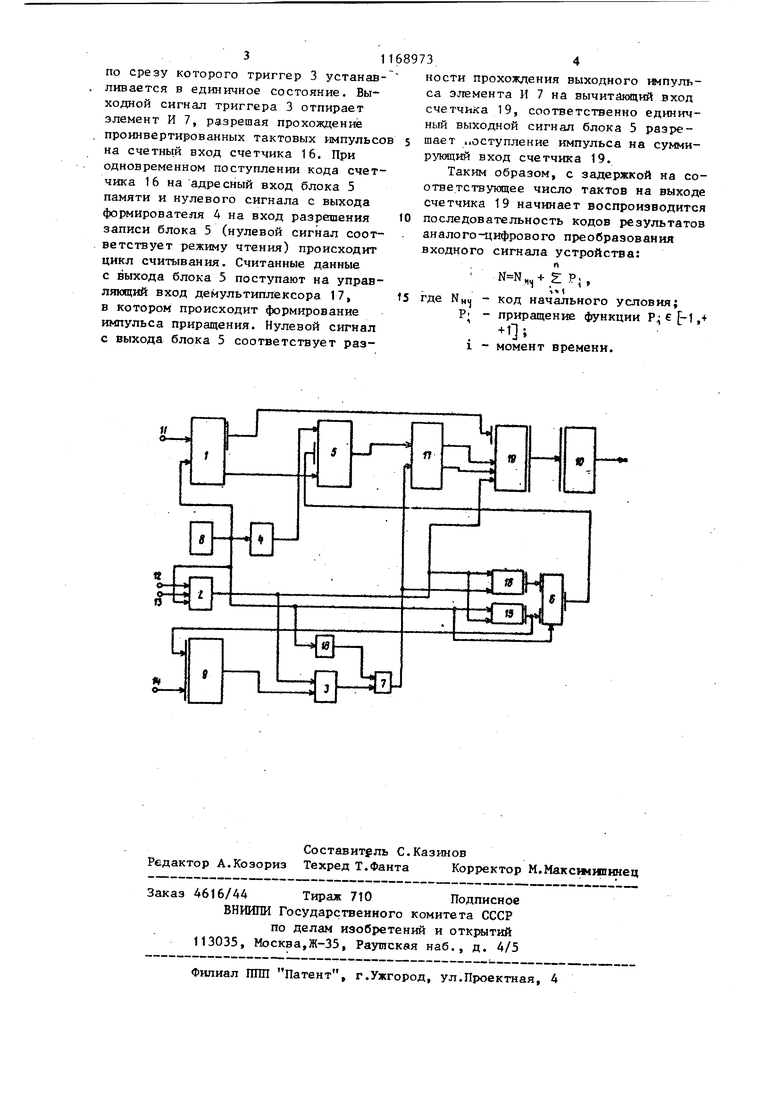

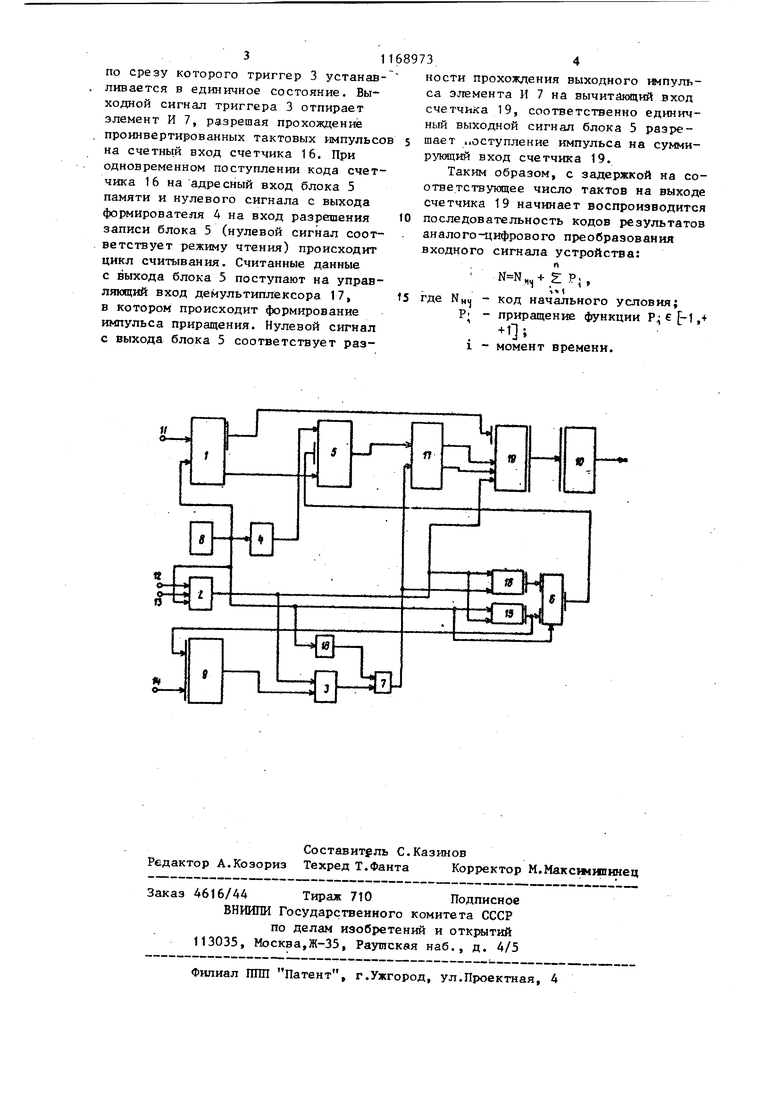

Изобретение относится к автоматик и вычислительной технике и может най ти применение, в частности, в- гибридных вычислительных устройствах и системах при воспроизведении функций с регулируемым временем запазда.вания. Цель изобретения - упрощение устройства путем уменьшения информационной емкости блока оперативной памяти. На чертеже изображена блок-схема устройства для воспроизведения запаздашающих функций. Устройство содержит следящий аналого-цифровой преобразователь 1 (счетного типа), первый 2 и второй 3 триггеры, формирователь 4 импульсов, блок 5 оперативной памяти, мультиплексор 6, элемент И 7, генератор 8, тактовых импульсов, блок 9 сравнения кодов, выходной -цифроаналоговый преобразователь 10, вход 11 устройства, первую 12 и вторую 13 шины задания режимов работы, шину 14 задания кода времени запаздывания, первый 15 и второй 16 счетчики, демультиплексор 17, элемент. НЕ 18 и третий счетчик 19.. Формирователь 4 импульсов выполне на элементе задержки и элементе И, выход которого соединен с выходом формирователя, первый вход подключен к выходу элемента задержки, а второй вход - к входу формирователя и входу элемента задержки. Демульти.тлексор 1 7 содержит элемент НЕ и два элемента И, подключенные первыми входами к информационному входу демультиплек сора, а выходами - соответственно к первому и второму выходам демульти плексора, а второй вход первого элемента И-соединен через элемент НЕ с управляющим входом демультиплексора и вторым входом второго элемента И. Устройство функционирует в двух режимах: Подготовка (триггер 2 обнулен импульсом. Стоп с шины 13 устройства) и Воспроизведение (триггер 2 установлен в единичное состояние, импульсом Старт с шины 1 устройства). Кроме того, переключени триггера 2 в соответствующее состояние происходит по срезу выходного им пульса генератора 8, поступающего на синхронизирукщий вход Триггера 2, В режиме Подготовка нулевой сиг-, нал с выхода триггера 2 обнуления поступает в триггер 3 и счетчики 15 и 16, а также на вход управления установкой кода счетчика 19, разрешая запись выходного параллельного кода результата преобразования аналого-цифрового преобразователя 1 в счетчик 19. Выходной код счетчика 19 с помощью преобразователя 10 преобразуется в ана юговый сигнал, поступающий на выход устройства. При этом сигнал на выходе устройства с точностью до единицы младщего разряда преобразователей 1 и 10 равен аналоговому сигналу, поступающему на вход 11 устройства. В режиме Воспроизведение сигнал . с шины 12 устанавливает триггер 2 в единичное состояние. Единичный сигнал с выхода триггера 2 запрещает режим записи кода аналого-цифрового преобразователя 1 в счетчик 19. Таким образом, последний код из последовательности параллельных кодов, записанных в счетчик 19, является кодом начального условия, который с выхода счетчика 19 поступает на вход преобразователя 10, формирующего напряжение начального условия. По фронту каждого выходного импульса генератора 8 происходит формирование сигнала знака приращения на соответствующем выходе аналого-цифрового преобразователя 1 (в случае положительного приращения формирователя - единичный сигнал, а в случае отрицательного приращения - нулевой сигнал). Счетчик 15 по фрон.ту импульса генератора 8 устанавливает очередной адрес ячейки записи, который поступает на адресный вход блока 6 оперативной памяти через мультиплексор 6. При поступлении задержанного единичного сигнала с выхода формирователя 4 происходит цикл записи в ячейку блока 5 оперативной памяти. Указанный цикл записи повторяется периодически с приходом последующих тактовых импульсов. Считывание информации из блока 5 происходит также последовательно, начиная с первой ячейки памяти, но с задержкой на число тактов, определяемое цифровым кодом, поступающим на шину 1 4 устройства. При равенстве кодов на входах блока 9 сравнения на его выходе формируется импульс сравнения.

по срезу которого триггер 3 устанавливается в единичное состояние. Выходной сигнал триггера 3 отпирает элемент И 7, разрешая прохождение проинвертированных тактовых импульсо на счетный вход счетчика 16. При одновременном поступлении кода счетчика 16 на адресный вход блока 5 памяти и нулевого сигнала с выхода формирователя 4 на вход разрешения записи блока 5 (нулевой сигнал соответствует режиму чтения) происходит цикл считывания. Считанные данные с выхода блока 5 поступают на управляющий вход демультиплгаксора 17, в котором происходит формирование импульса приращения. Нулевой сигнал с выхода блока 5 соответствует разности прохождения выходного импульса элемента И 7 на вычитающий вход счетчика 19, соответственно единичный выходной сигнал блока 5 раэрешает ..оступление импульса на суммирукщий вход счетчика 19.

Таким образом, с задержкой на соответствуклцее число тактов на выходе счетчика 19 начинает воспроизводится

последовательность кодов результатов аналого-цифрового преобразования входного сигнала устройства:

,4-2 Р,

1 1 где NMIJ - код начального условия;

Р - приращение функции Р с -1,+

1 - момент времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сложных сигналов | 1983 |

|

SU1153391A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1561075A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Устройство для многоканальной записи аналоговых процессов | 1985 |

|

SU1304070A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182546A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1249546A1 |

УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ЗАПАЗДЫВАЮЩИХ ФУНКЦИЙ, содержащее следящий аналого-цифровой преобразователь, информационный вход которого является входом устройства, а синхронизирующий вход подключен к выходу генератора тактовых импульсов, выходной цифроаналоговый преобразователь и первый триггер, соединенный первым и вторым установочными входами с первой и второй шинами задания режимов работы устройства соответственно, а выходом - с входами обнуления первого и второго счетчиков и первым установочным входом второго триггера, подключенного выходом к первому входу элемента И, соединенного выходом со счетным входом второго счетчика, подключенного кодовым выходом к первому информационному входу мультиплексора, соединенного вторым информационным входом с кодовым выходом первого счетчика и с первьм входом блока сравнения кодов, а выходом с адресным входом блока оперативной памяти, подключенного входом разрешения записи к выходу формирователя импульсов, причем второй вход блока сравнения кодов соединен с шиной задания кода времени запаздывания устройства, отличающееся тем, что, с целью упрсядения устройст. ва путем уменьшения информационной емкости блока.оперативной памяти, устройство содержит демультиплексор, элемент НЕ и третий счетчик, подключенный выходом к входу выходного цифроаналогового преобразователя, установочным входом - к выходу парал лельного кода результата преобразования следящего аналого-цифрового преобразователя, входом управления (Л установкой кода - к выходу первого триггера, а суммирующим и вычитающим входами - к первому и второму выходам демультиплексора соответственно, соединённого информационным входом с выходом элемента И, а управляющим входом - с выходом блока оперативной Од памяти, подключенного информационным 00 входом к выходу знака единичного приращения следящего аналого-цифровоф Nj го преобразователя, причем выход генератора тактовых импульсов соединен ее с входом формирователя импульсов, синхронизирующим входом первого триггера, счетньм входом первого счетчика, управляющим аходом мультиплексора и входом элемента НЕ, выход которого подключен к второму.входу элемента И, а выход блока сравнения кодов соединен с вторым установочным входом второго триггера.

| Смолов В.Б | |||

| Аналоговые вычислительные машины | |||

| М., Высшая школау 1972, с | |||

| Электромагнитный счетчик электрических замыканий | 1921 |

|

SU372A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-23—Публикация

1984-02-20—Подача