ветственно к выходу управления обменом регистра м1.кроопераций, третьему выходу блока приемопередатчиков, выходу второго элемента И и выходу мультиплексора старшего разряда числа, первый, второй, третий и четвертый информационные входы и первый и второй адресные входы которого соединены соответственно с входом знака группы входов логических условий устройства, выходом триггера знака, третьим выходом блока приемопередатчиков, шиной нулевого потенциала устройства, первым и вторым адресными выходами регистра микроопераций первый и второй входы второго элемента И подключены соответственно

к четвертому выходу блока приемопередатчиков и выходу управления вьщачей мпади1его разряда результата регистра микроопераций, первый и второй входы и вькод сумматора по модулю два соединены соответственно со входом знака группы логических условий устройства, выходом триггера знака и выходом знака устройства, второй вход и выход первого элемента И подключены соответственно к выходу разрешения записи знака регистра микроопераций и синхровхо; у триггера знака, информационный вход которого соединен с входом знака группы входов логических условий устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

УСТРОЙСТВО УПРАВЛЕНИЯ МИКРОПРОЦЕССОРОМ, содержащее блок памяти микрокоманд, регистр адреса, регистр микроопераций, мультиплексор логических условий, ко ммутатор, триггер пуска, генератор тактовых импульсов и первый элемент И, причем выход регистра адреса соединен с адресным входом блока памяти микрокоманд, выход логических условий и выход микроопераций которого подключены соответственно ic адресному ёходу мультиплексора логических условий и информационному входу регистра микроопераций, вход установки, вход сброса и выход триггера пуска соединены соответственно с входом пуска устройства, .выходом конца работы регистра микроопераций и входом генератора тактовых импульсов, первый и второй выходы которого подключены к синхровходам соответственно регистра адреса и регистра микроопераций, первый вход первого элемента И соединен с вторым выходом генератора тактовых импульсов, первый и второй информационные входы и выход мультиплексора логических условий подключены соответственно к выходу модифицируемого разряда группы адресньк выходов блока памяти микрокоманд, группе входов логических условий устройства и входу модифицируемого разряда первой группы информационных входов коммутатора, входы немодифицируемых разрядов первой группы информационных входов, информационные входы второй- группы и. управляющий вход коммутатора соединены соответственно с выходами немодифицируемых разрядов группы адресных -выходов .блока памяти микрокоманд, входом кода операции (Л устройства и выходом конца команды регистра микроопераций, группа выс: ходов которого является группой выхог дов микроопераций устройства, о тличающееся тем, что, с целью повьпиения быстродействие/, оно содержит блок приемопередатчиков, мультиплексор старшего разряда числа, сд триггер знака, сумматор по модулю О5 два, второй элемент И и элемент О И-НЕ, первый и второй входы и выход .которого подключены соответственно tsD к входу переполнения группы входов логических условий устройства, выходу сумматора по модулю два и первому информационному входу блока приемопередатчиков, первый, второй, третий и четвертый выходы которого соединены соответственно с первым, вторым, .третьим и четвертым выходами руппы входов-выходов устройства, управляющий вход, второй, третий и четвертый информационные входы блока приемопередатчиков подключены ссот

Изобретение относится к вычислительной технике и может быть использовано при построении управляющих устройств для операционных устройств ЭВМ и вычислительных систем, реали-зованных на основе микропроцессорных секций.

Цель изобретения - повышение быстродействия устройства и снижение объема блока памяти микрокоманд путем обеспечения непосредственного обмена информацией между внешними входами-выходами микропроцессоров.

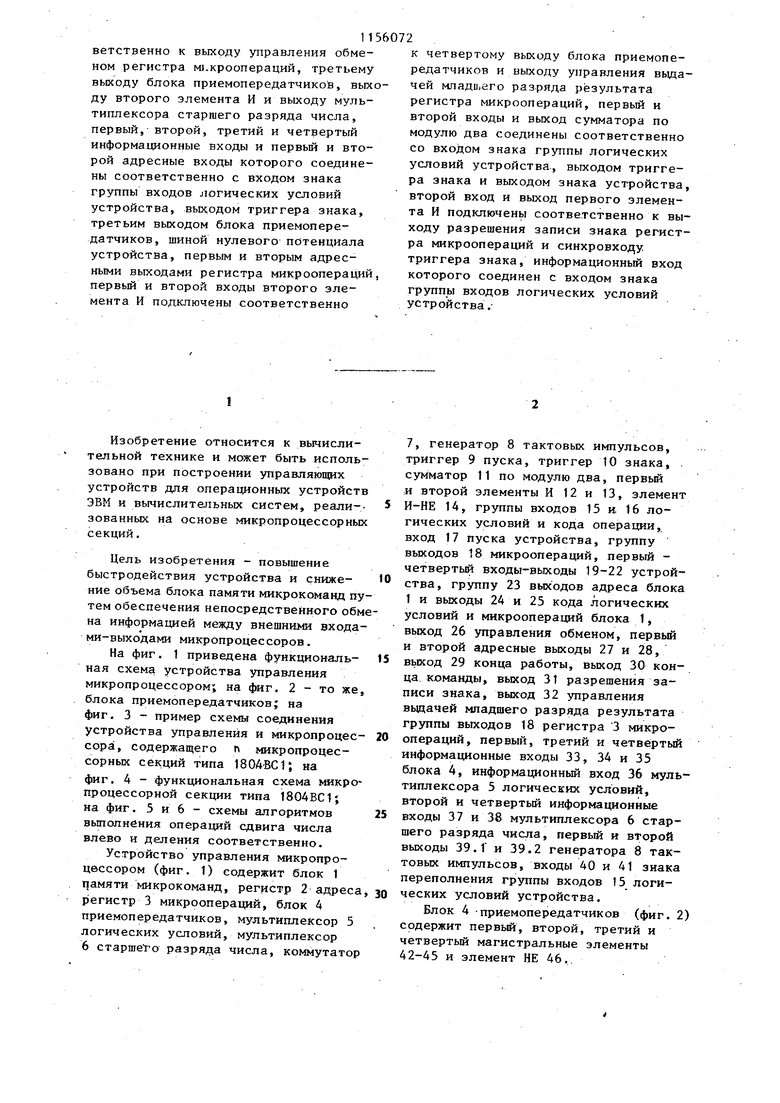

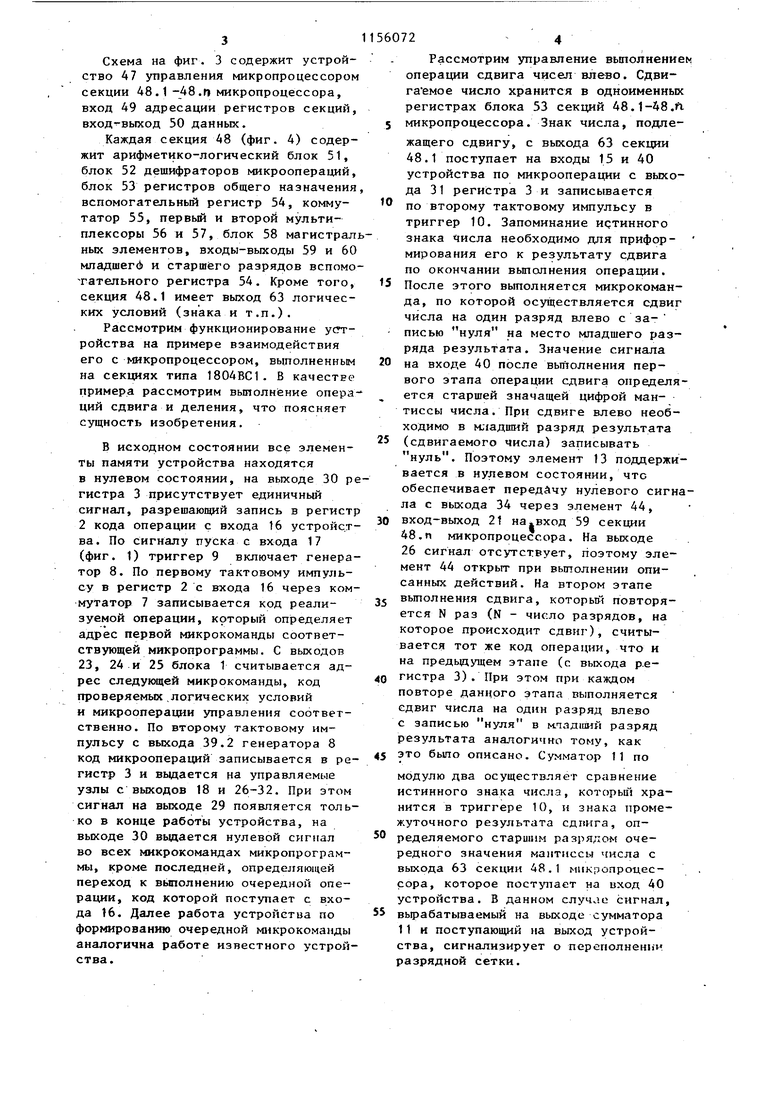

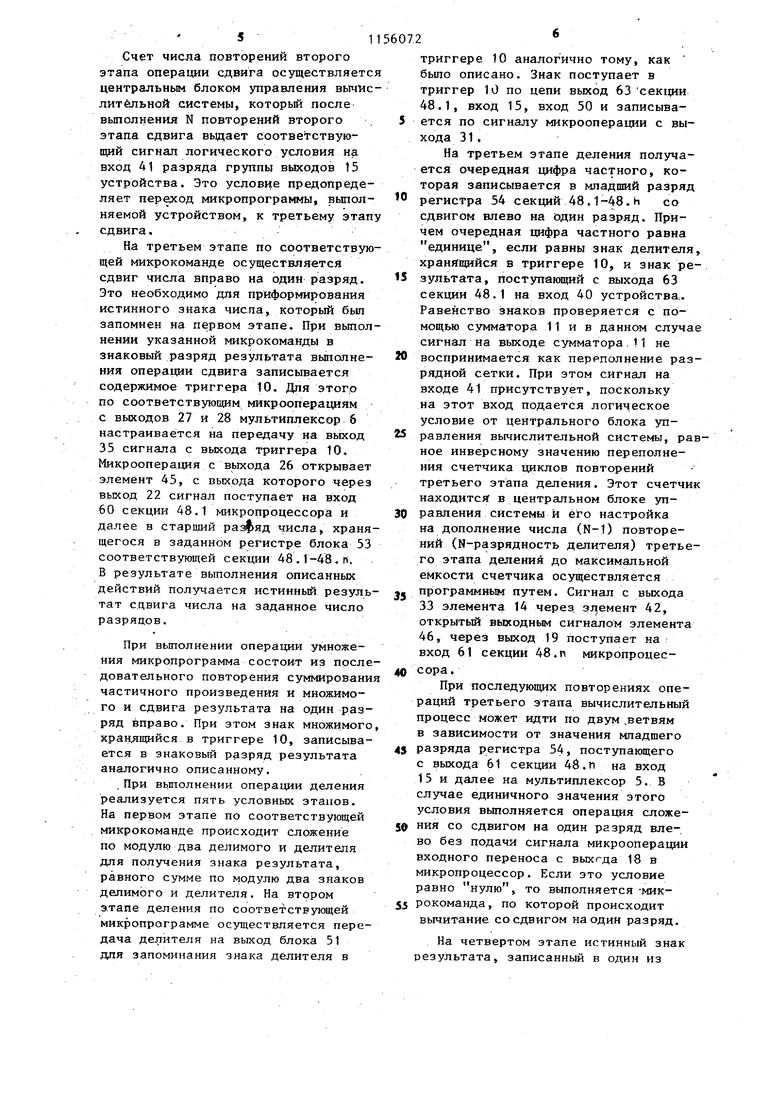

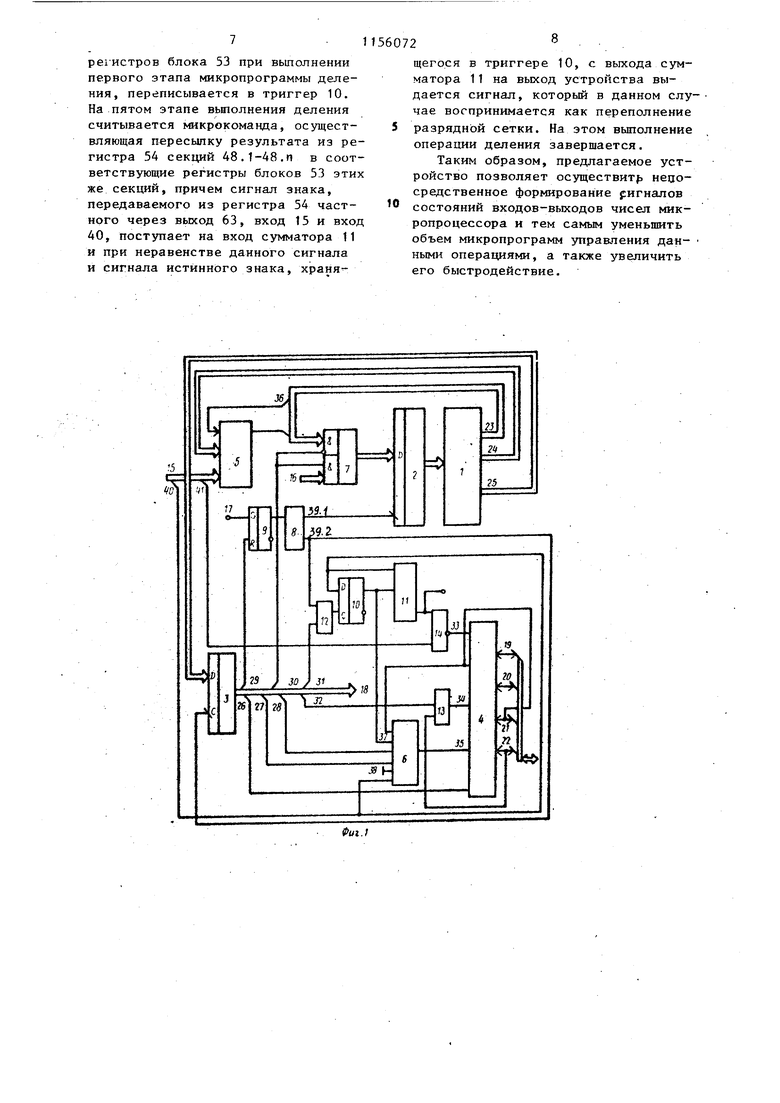

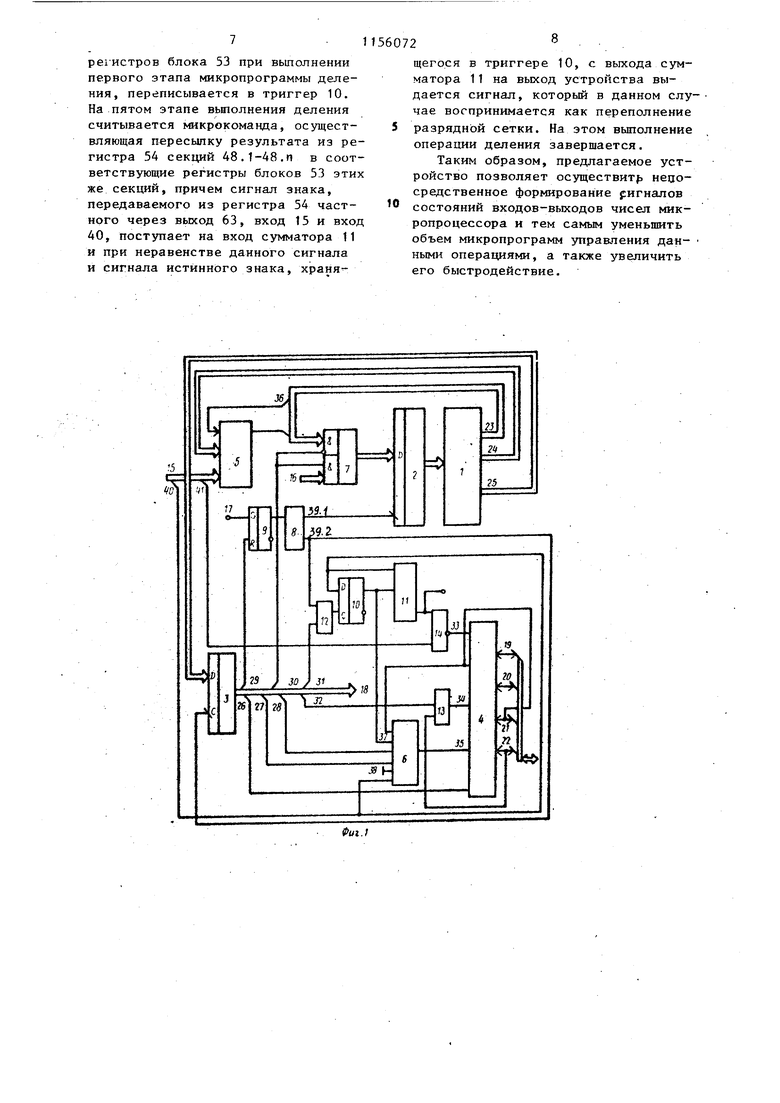

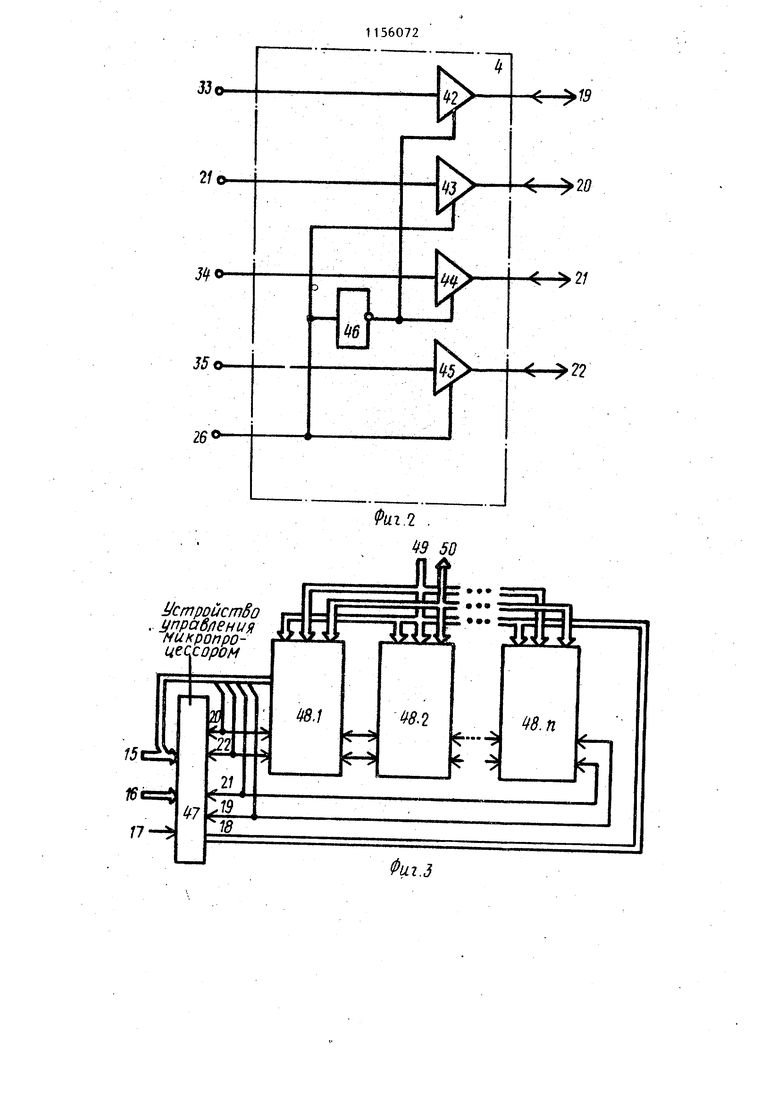

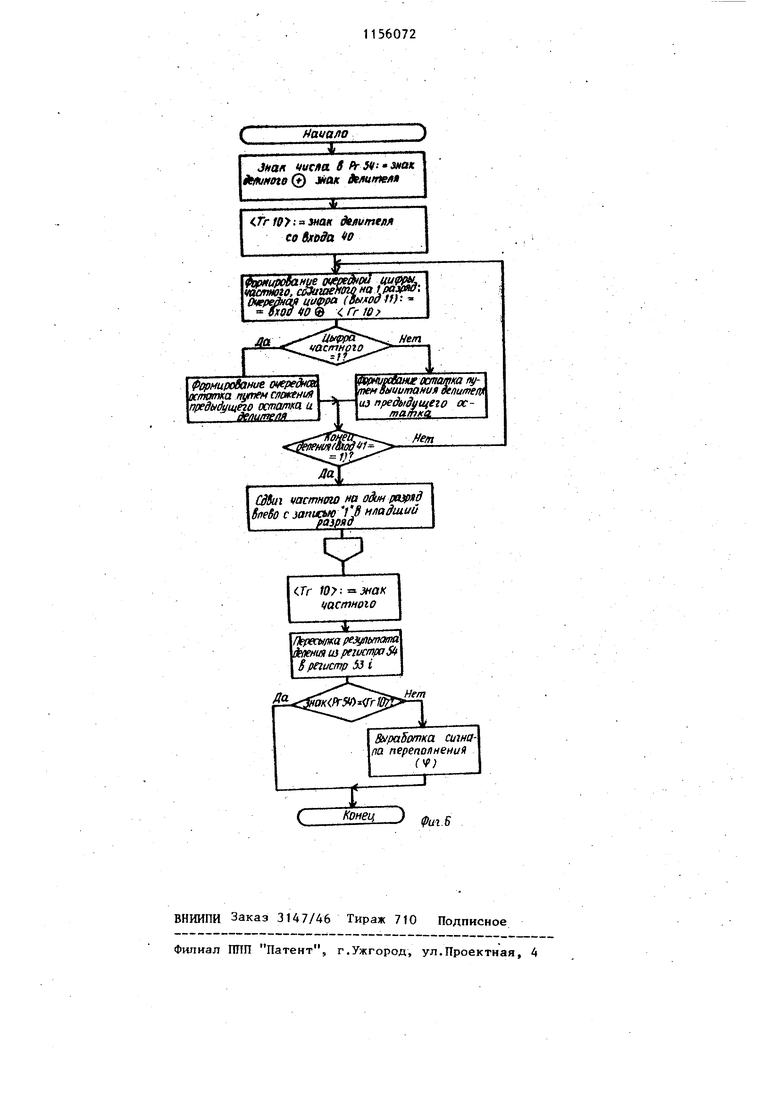

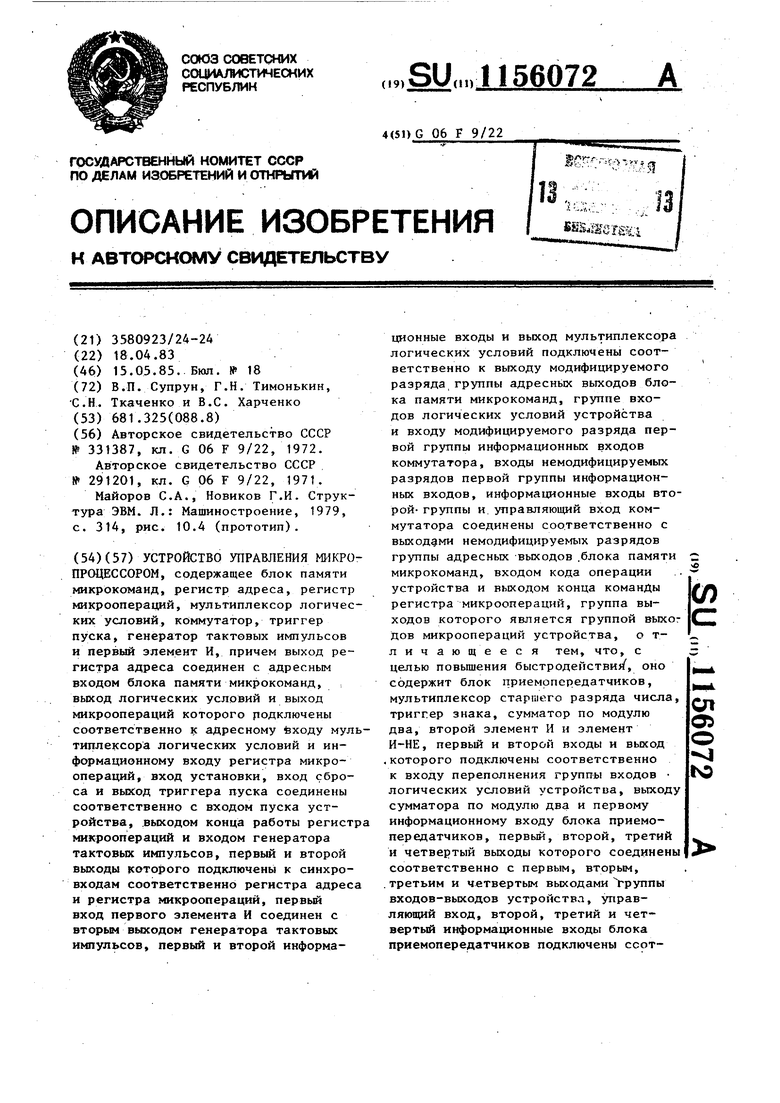

На фиг. 1 приведена функциоиальная схема устройства управления микропроцессором; на фаг. 2 - то же, блока приемопередатчиков; на фиг. 3 - пример схемы соединения устройства управления и микрОпроцессора, содержащего п микропроцессорных секций типа 180АВС1; на фиг. А - функциональная схема микропроцессорной секции типа 1804ВС1; на фиг. 5 и 6 - схемы алгоритмов вьтопнбния операций сдвига числа влево и деления соответственно.

Устройство управления микропроцессором (фиг. 1) содержит блок 1 памяти микрокоманд, регистр 2 адреса регистр 3 микроопераций, блок 4 приемопередатчиков, мультиплексор 5 логических условий, мультиплексор 6 старшего разряда числа, коммутатор

7, генератор 8 тактовых импульсов, триггер 9 пуска, триггер 10 знака, . сумматор 11 по модулю два, первьй :И второй элементы И 12 и 13, элемент И-НЕ 14, группы входов 15 и 16 логических условий и кода операции, вход 17 пуска устройства, группу выходов 18 микроопераций, первый четвертый входы-выходы 19-22 устройства, группу 23 выходов адреса блока 1 и выходы 24 и 25 кода логических условий и микроопераций блока 1, выход 26 управления обменом, первый и второй адресные выходы 27 и 28, вькод 29 конца работы, выход 30 конца команды, выход 31 разрешения записи знака, выход 32 управления вьдачей младшего разряда результата группы выходов 18 регистра 3 микроопераций, первый, третий и четвёртый информационные входы 33, 34 и 35 блока 4, информационный вход 36 мультиплексора 5 логических условий, второй и четвертый информационные входы 37 и 38 мультиплексора 6 старшего разряда числа, первый и второй выходы 39.1 и 39.2 генератора 8 тактовых импульсов, входы 40 и 41 знака переполнения группы входов 15 логических условий устройства.

Блок 4 -приемопередатчиков (фиг. 2 содержит первый, второй, третий и четвертый магистральные элементы 42-45 и элемент НЕ 46..

Схема на фиг. 3 содержит устройство 47 управления микропроцессором секции 48.1-48 .г микропроцессора, вход 49 адресации регистров секций, вход выход 50 данных.

Каждая секция 48 (фиг. 4) содержит арифметико-логический блок 51, блок 52 дешифраторов микроопераций, блок 53 регистров общего назначения вспомогательный регистр 54, коммутатор 55, первый и второй мультиплексоры 56 и 57, блок 58 магистралных элементов, входы-выходы 59 и 60 младшег 1) и старшего разрядов вспомотательного регистра 54. Кроме того, секция 48.1 имеет выход 63 логических условий (знака и т.п.).

Рассмотрим функционирование устройства на примере взаимодействия его с микропроцессором, выполненным на секциях типа 1804ВС1. В качестве примера рассмотрим выполнение операций сдвига и деления, что поясняет сущность изобретения.

В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии, на выходе 30 регистра 3 присутствует единичный сигнал, разрешающий запись в регистр 2 кода операции с входа 16 устройства. По сигналу пуска с входа 17 (фиг. 1) триггер 9 включает генератор 8. По первому тактовому импульсу в регистр 2 с входа 16 через коммутатор 7 записывается код реализуемой операции, который определяет адрес первой микрокоманды соответствующей микропрограммы. С выходов 23, 24 и 25 блока 1 считывается адрес следующей микрокоманды, код проверяемых.логических условий и микрооперации управления соответственно. По второму тактовому импульсу с выхода 39.2 генератора 8 код микроопераций записывается в регистр 3 и выдается на управляемые узлы Свыходов 18 и 26-32. При этом сигнал на выходе 29 появляется только в конце работы устройства, на выходе 30 вьдается нулевой сигнал во всех микрокомандах микропрограммы, кроме последней, oпpeдeJГяюiцeй переход к вьтолнению очередной операции, код которой поступает с входа 16. Далее работа устройства по формированию очередной микрокоманды аналогична работе известного устройства.

Рассмотрим управление выполнением операции сдвига чисел влево. Сдвигаемое число хранится в одноименных регистрах блока 53 секций 48.1-48.Л микропроцессора. Знак числа, подлежащего сдвигу, с выхода 63 секции 48.1 поступает на входы 15 и 40 устройства по микрооперации с выхода 31 регистра 3 и записывается

по второму тактовому импульсу в триггер 10. Запоминание иртинного знака числа необходимо для приформирования его к результату сдвига по окончании выполнения операции.

После этого выполняется микрокоманда, по которой осуществляется сдвиг числа на один разряд влево с записью нуля на место младшего разряда результата. Значение сигнала

на входе 40 после выполнения первого зтапа операции сдвига определяется старшей значащей цифрой мантиссы числа. При сдвиге влево необходимо в младший разряд результата

(сдвигаемого числа) записывать

нуль. Поэтому элемент 13 поддерживается в нулевом состоянии, что обеспечивает передачу нулевого сигнала с выхода 34 через элемент 44,

вход-выход 21 на.вход 59 секции 48.п микропроцессора. На выходе 26 сигнал отсутствует, поэтому элемент 44 открыт при выполнении описанных действий. На втором этапе

выполнения сдвига, который повторяется N раз (N - число разрядов, на которое происходит сдвиг), считывается тот же код операции, что и на предыдущем этапе (с выхода р.егистра 3). При этом при каждом

повторе данного этапа выполняется сдвиг числа на один разряд влево с записью нуля в млад1шй разряд результата аналогично тому, как

это бьио описано. Сумматор 11 по

модулю два осуществляет сравнение истинного знака числа, которьй хранится в триггере 10, н знака промежуточного результата сдпига, определяемого старшим разрядом очередного значения мантиссы числа с выхода 63 секции 48.1 микропроцессора, которое поступает на иход 40 устройства. В данном случае сигнал,

вырабатываемый на выходе сумматора 11 и поступающий на выход устройства, сигнализирует о переполнении разрядной сетки.

Счет числа повторений второго этапа операции сдвига осуществляетс центральным блоком управления вычислительной системы, который после выполнения N повторений второго этапа сдвига вьщает соответствующий сигнал логического условия на вход А1 разряда группы выходов 15 устройства. Это условие предопределяет переход микропрограммы, вьшолняемой устройством, к третьему этап сдвига.

На третьем этапе по соответствующей микрокоманде осуществляется сдвиг числа вправо на один разряд. Это необходимо для приформирования истинного знака числа, который был запомнен на первом этапе. При выполнении указанной микрокоманды в знаковый разряд результата выполнения операции сдвига записывается содержимое триггера 10. Дпя этого по соответствующим микрооперациям с выходов 27 и 28 мультиплексор 6 настраивается на передачу на выход 35 сигнала с выхода триггера 10. Микрооперация с выхода 26 открывает элемент 45, с выхода которого через вькод 22 сигнал поступает на вход 60 секции 48.1 микропроцессора и далее в старший разряд числа, хранящегося в заданном регистре блока 53 соответствующей секции 48 .1-48. tv. В результате выполнения описанных действий получается истинный результат сдвига числа на заданное число разрядов.

При выполнении операции умножения микропрограмма состоит из последовательного повторения сум1мировани частичного произведения и множимого и сдвига результата на один разряд вправо. При этом знак множимого хранящийся в триггере 10, записывается в знаковый разряд результата аналогично описанному.

При вьшолнении операции деления реализуется пять условных этапов. На первом этапе по соответствующей микрокоманде происходит сложение по модулю два делимого и делителя для получения знака результата, равного сумме по модулю два знаков делимого и делителя. На втором этапе деления по соответствз тощей микропрограмме осуществляется передача делителя на выход блока 51 для запоминания знака делителя в

триггере 10 аналогично тому, как быпо описано. Знак поступает в триггер 10 по цепи выход 63 секции 48.1, вход 15, вход 50 и записывается по сигналу микрооперации с выхода 31.

На третьем этапе деления получается очередная цифра частного, которая записывается в младший разряд регистра 54 секций 48.1-48.h со сдвигом влево на один разряд. Причем очередная цифра частного равна единице, если равны знак делителя, хранйпщйся в триггере 10, и знак результата, поступающий с выхода 63 секции 48.1 на вход 40 устройства,. Равенство знаков проверяется с помощью сумматора 11 и в данном случае сигнал на выходе сумматора.11 не

0 воспринимается как переполнение разрядной сетки. При этом сигнал на входе 41 присутствует, поскольку на этот вход подается логическое условие от центрального блока уп5равления вычислительной системы, равное инверсному значению переполнения счетчика Циклов повторений третьего этапа деления. Этот счетчик находится в центральном блоке управления системы и его настройка

0 на дополнение числа (N-1) повторений (N-разрядность делителя) третьего этапа деления до максимальной емкости счетчика осуществляется программным путем. Сигнал с выхода

5 33 элемента 14 через элемент 42, открытьй выходным сигналом элемента 46, через выход 19 поступает на вход 61 секции 48.г микропроцессора .

0

При последующих повторениях операций третьего этапа вычислительный процесс может идти по двум .ветвям в зависимости от значения младшего разряда регистра 54, поступающего

5 с выхода 61 секции 48.п на вход 15 и далее на мультиплексор 5. В случае единичного значения этого условия выполняется операция сложения со сдвигом на один разряд вле0во без подачи сигнала микрооперации входного переноса с вькгда 18 в микропроцессор. Если это условие равно нулю, то выполняется -мик5 рокоманда, по которой происходит вычитание со сдвигом на один разряд.

На четвертом этапе истинный знак результата, записанный в один из 7 регистров блока 53 при вьтолнении первого этапа микропрограммы деления, переписывается в триггер 10. На пятом этапе выполнения деления считывается микрокоманда, осуществляющая пересыпку результата из регистра 54 секций 48.1-48.л в соответствующие регистры блоков 5.3 этих же секций, причем сигнал знака, передаваемого из регистра 54 частного через выход 63, вход 15 и вход 40, поступает на вход сумматора 11 и при неравенстве данного сигнала и сигнала истинного знака, храня 2 щегося в триггере 10, с выхода сумматора 11 на выход устропства выдается сигнал, который в данном случае воспринимается как переполнение разрядной сетки. На этом выполнение операции деления завершается. Таким образом, предлагаемое устройство позволяет осуществит непосредственное формирование ригналов состояний входов-выходов чисел микропроцессора и тем самым уменьшить объем микропрогра м згправления данными операциями, а также увеличить его быстродействие.

J-J oJ5o.

fe

Устройство г-,

управления jr

ч минропро- -Ski:

Е

цестором

i

хл

,;

2/

.79.

«7

(5«г.2 .

sa

-(9.2

е- Фиг.З

С

CffSui операнда, на один разряд 8пеёо дл запомина-ния знака циспа В Тг W

СдВиг операнда 5леВо на один разряд ; Анализ признака Вш.и Тг W + Вход о

СдВиг результата SnpaSo

на один разряд у

Ст. разряд.. Гг ;о

С

KoHei4 Фи1.5

В младший разряд

записывается L ну/}ь

Нет

С

Начало

SnuK числа 8 Рг54мак Л /ifineQ JHOK Йеяитем

лиа(г диитем со вх&да 0

i

(Миг частною но один рауяд

StieSo с записьюf8 нюдший разряд

9

Гг частного

Пересыпка результата хаения из регистра Sf S регистр Л (

Да

Hen

ipfiUf&iHUf вааатка путем вуиитания eenumeiy(

из npe iSuuffio XmaihMa

Нет

Нет

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 0 |

|

SU331387A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| МИКРОПРОГРАЛ\АШОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 0 |

|

SU291201A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Майоров С.А., Новиков Г.И | |||

| Структура ЭВМ | |||

| Л.: Машиностроение, 1979, с | |||

| Мяльно-трепальный станок | 1921 |

|

SU314A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1985-05-15—Публикация

1983-04-18—Подача