Изобретение относится к вычислительной технике и может быть использовано при построении цифровых .систем обработки данных и цифровых управляющих систем на основе микроЭВМ.

Цель изобретения - повышение быстродействия устройства при считывании информации из блоков памяти группы.

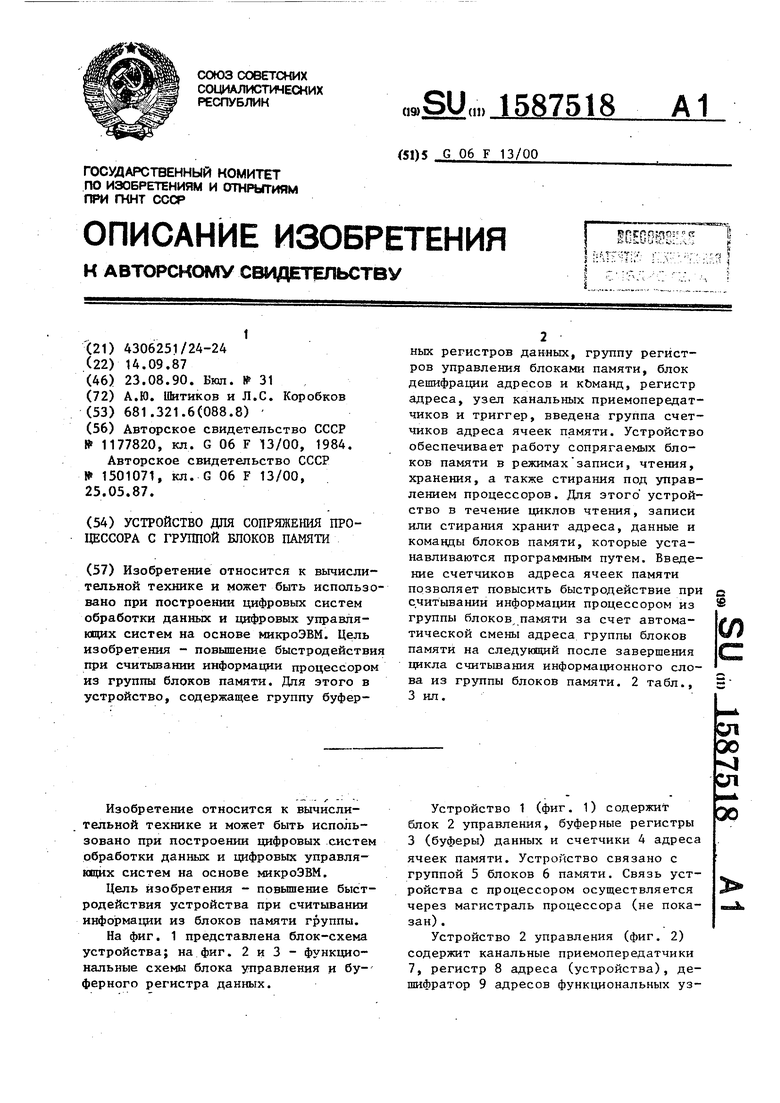

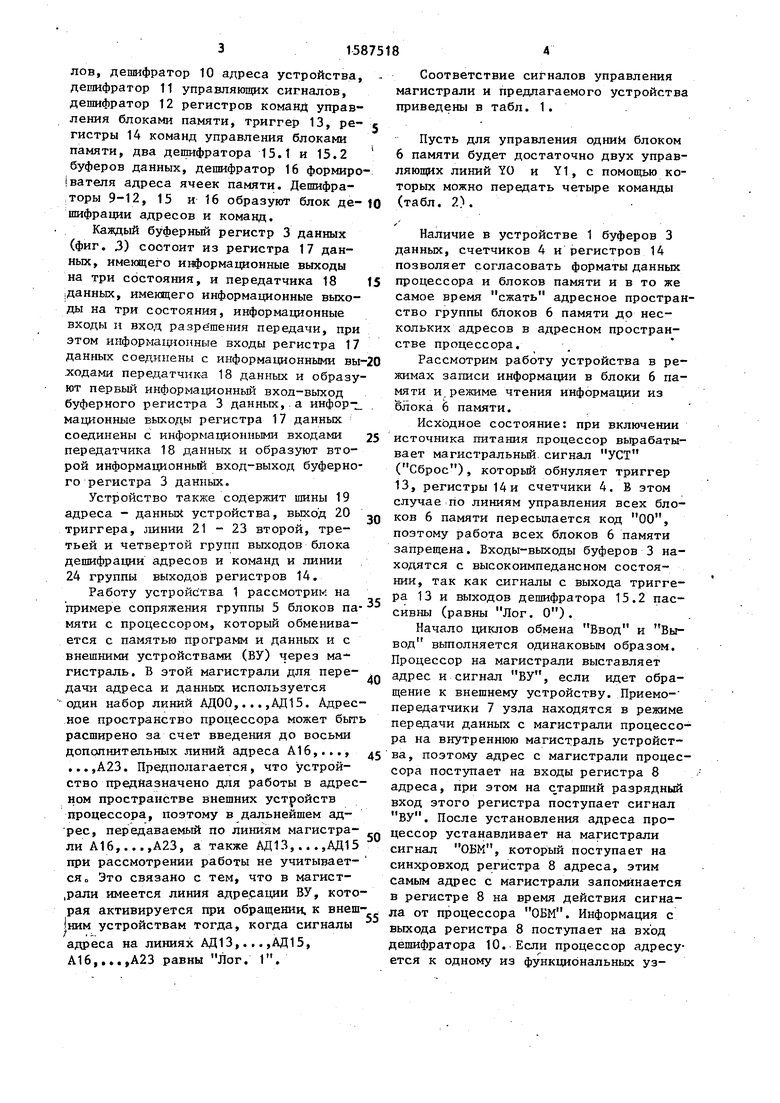

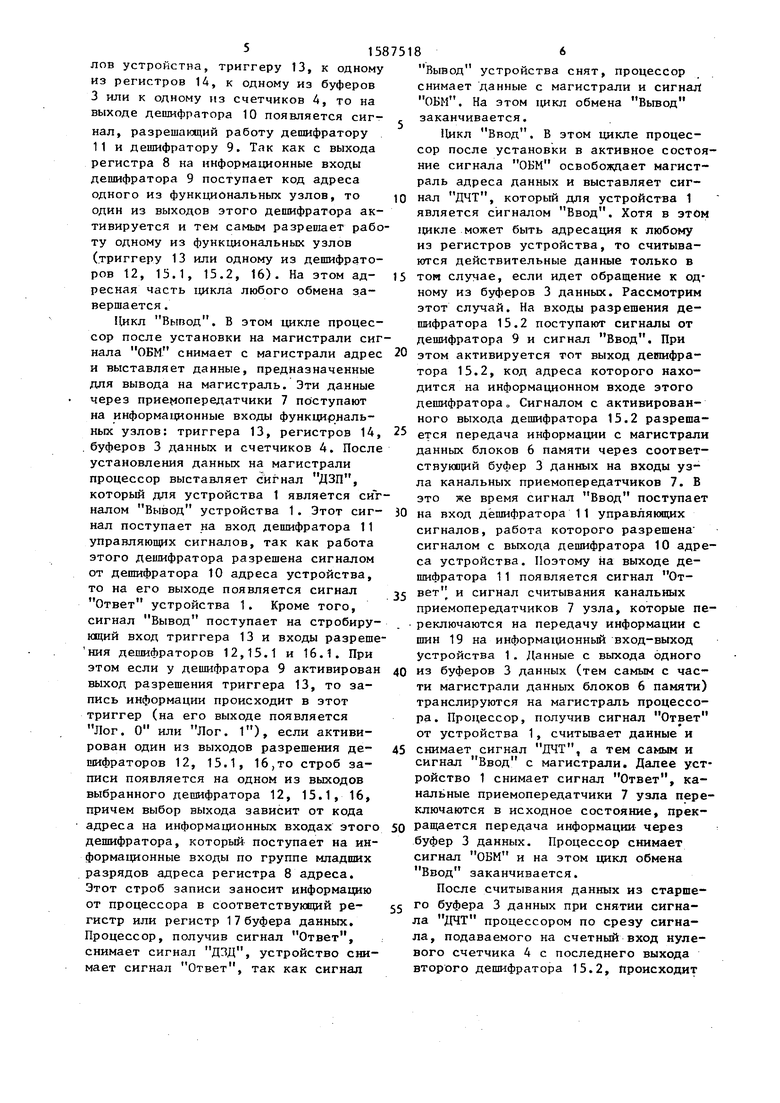

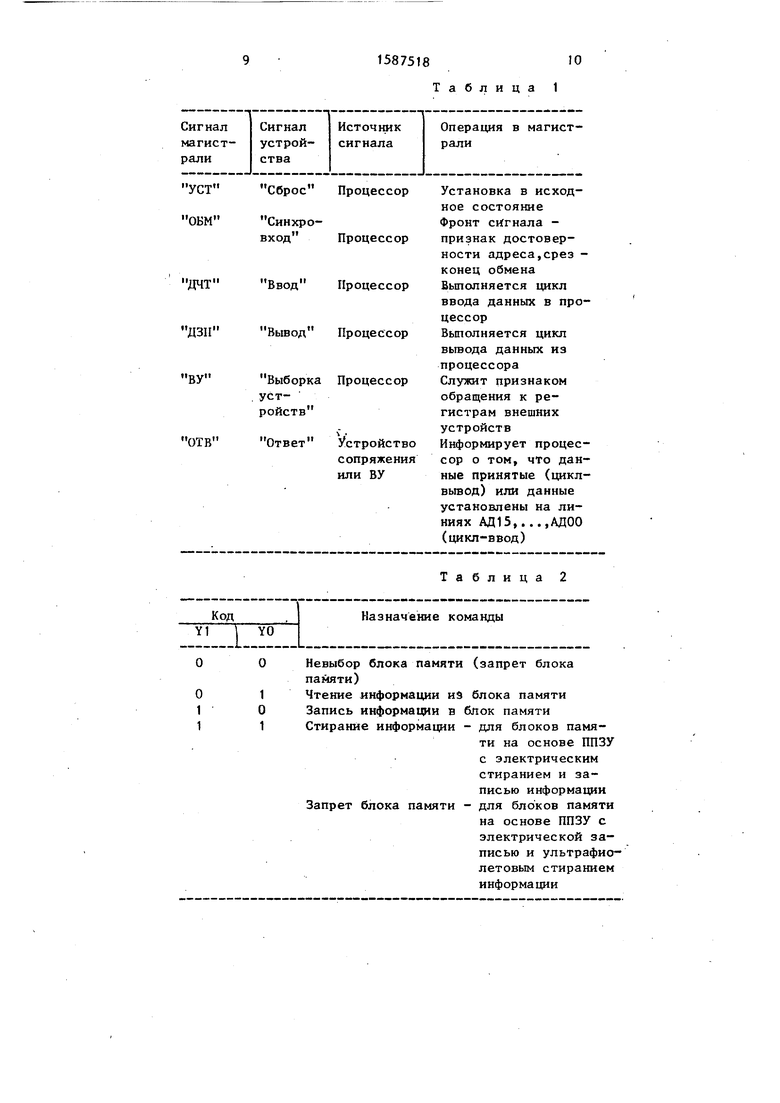

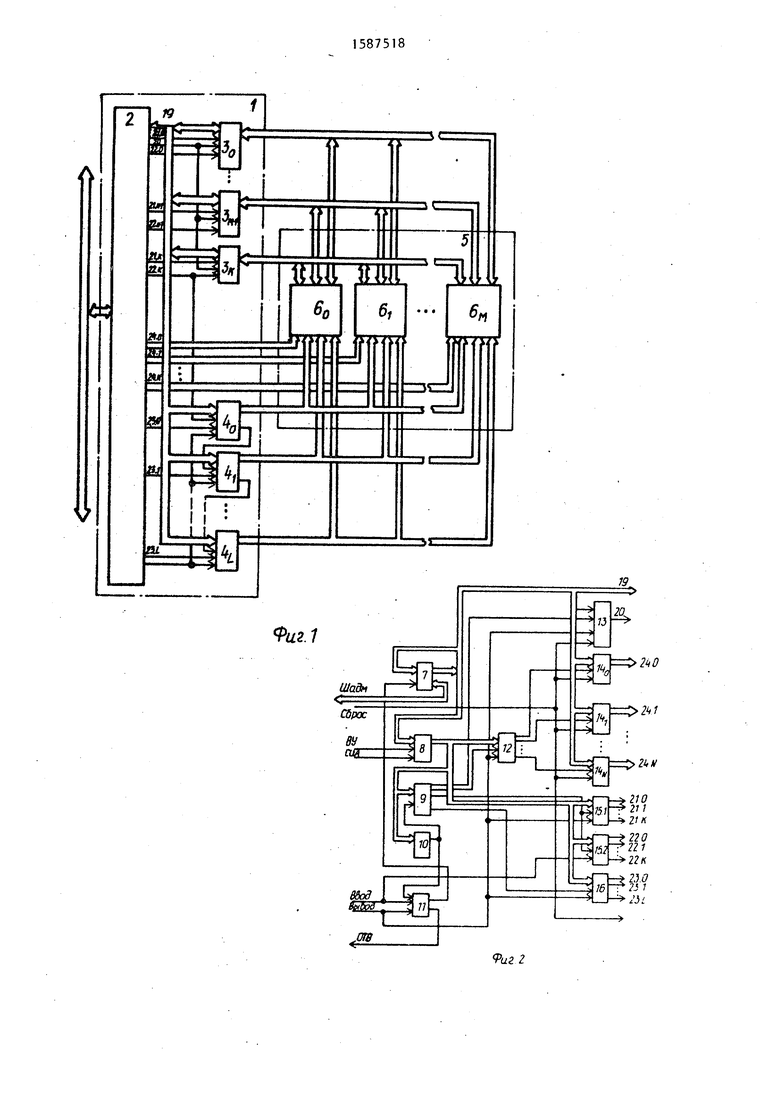

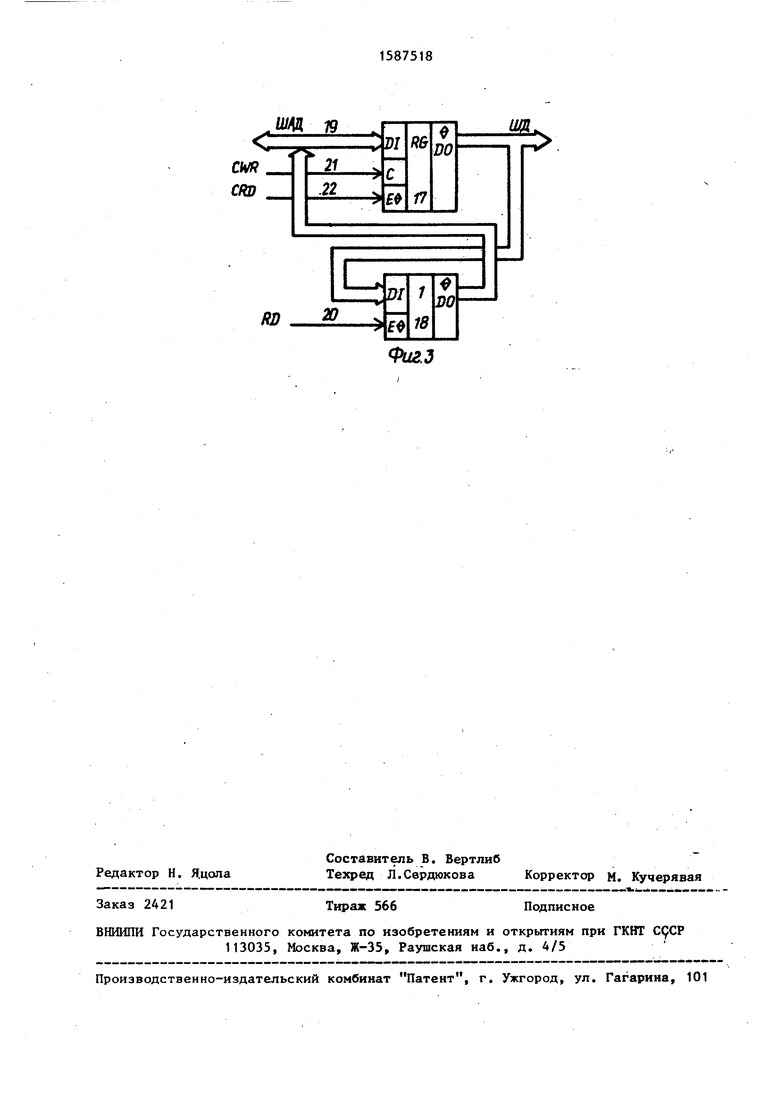

На фиг. 1 представлена блок-схема устройства; на фиг. 2 и 3 - функциональные схемы блока управления и бу- ферного регистра данных.

Устройство 1 (фиг. 1) содержит блок 2 управления, буферные регистры 3 (буферы) данных и счетчики 4 адреса ячеек памяти. Устройство связано с группой 5 блоков 6 памяти. Связь устройства с процессором осуществляется через магистраль процессора (не показан) .

Устройство 2 управления (фиг. 2) содержит канальные приемопередатчики 7, регистр 8 адреса (устройства), дешифратор 9 адресов функтщональных узСП

эо У1

30

лов, дешифратор 10 адреса устройства, дешифратор 11 управляющих сигналов, дешифратор 12 регистров команд управления блоками памяти, триггер 13, ре- гистры 14 команд управления блоками памяти, два дешифратора 15.1 и 15.2 буферов данных, дешифратор 16 формиро вателя адреса ячеек памяти. Дешифра- :Торы 9-12, 15 и 16 образуют блок де- шифрации адресов и команд.

Каждый буферный регистр 3 данных (фиг. 3) состоит из регистра 17 данных, имеющего информационные выходы на три состояния, и передатчика 18 I данных, имекщего информационные выходы на три состояния, информационные входы н вход разрешения передачи, при этом информационные входы регистра 17 данных соединены с информационными выходами передатчика 18 данных и образуют первый информационный вход-выход буферного регистра 3 данных,.а инфор- мационные выходы регистра 17 данных соединены с информационными входами передатчика 18 данных и образуют второй информационный вход-выход буферного регистра 3 данных.

Устройство также содержит шины 19 адреса - данных устройства, вько д 20 триггера, линии 21 - 23 второй, третьей и четвертой групп выходов блока дешифрации адресов и команд и линии 24 группы выходов регистров 14.

Работу устройства 1 рассмотрим на примере сопряжения группы 5 блоков памяти с процессором, который обменивается с памятью программ и данных и с внешними устройствами (ВУ) через магистраль. В этой магистрали для пере-

дачи адреса и данных используется

ОДИН набор линий АДОО,...,АД15. Адресное пространство процессора может быть расширено за счет введения до восьми дополнительных линий адреса А16,..., ,..,А23. Предполагается, что устройство предйазначено для работы в адресном пространстве внешних устройств процессора, поэтому в дальнейшем адрес, передаваемый по линиям магистра- ли А16,...,А23, а также АД13,...,АД15 при рассмотрении работы не учитывает- сЯо Это связано с тем, что в магист- ,рали имеется линия адресации ВУ, которая активируется при обращении, к внешним устройствам тогда, когда сигналы адреса на линиях АД13,...,АД15, А16,...,А23 равны Лог. 1.

- е

5 0 5

0

-

5

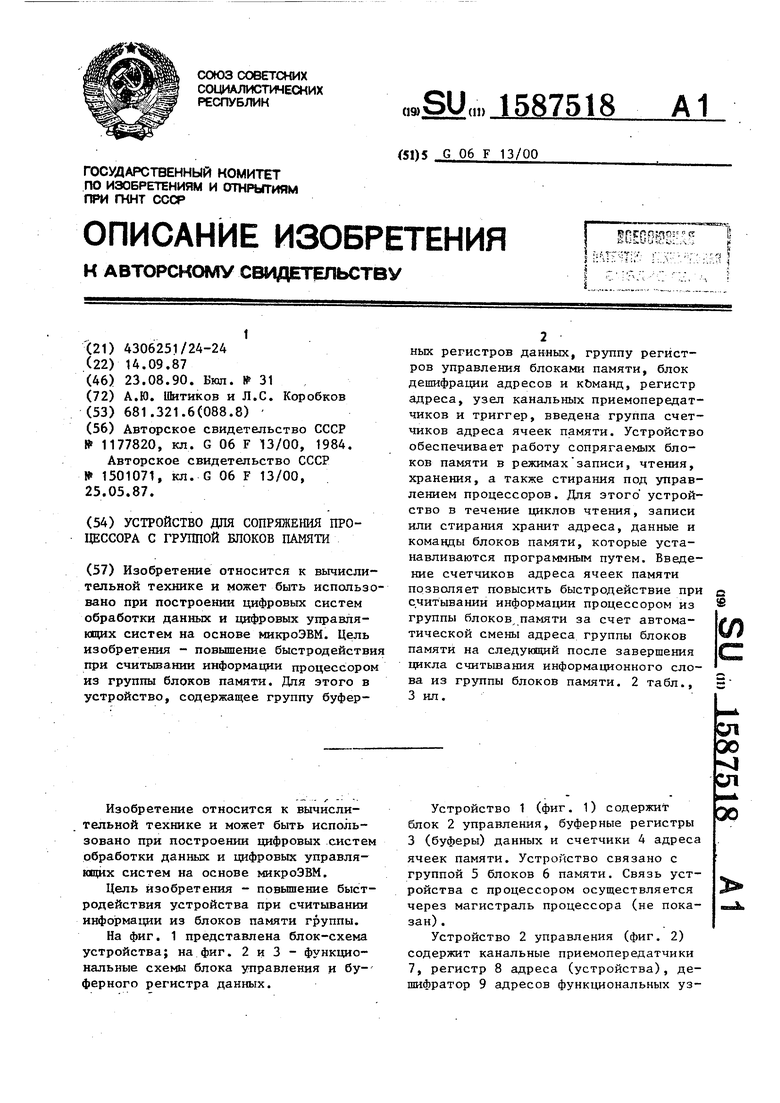

Соответствие сигналов управления магистрали и предлагаемого устройства приведены в табл. 1.

Пусть для управления одний блоком 6 памяти будет достаточно двух управляющих линий YO и Y1, с помощью которых можно передать четыре команды (табл. 2).

f .

Наличие в устройстве 1 буферов 3 данных, счетчиков 4 и регистров 14 позволяет согласовать форматы данных процессора и блоков памяти и в то же самое время сжать адресное пространство группы блоков 6 памяти до нескольких адресов в адресном пространстве процессора.

Рассмотрим работу устройства в режимах записи информации в блоки 6 памяти и,режиме чтения информации из Блока 6 памяти.

Исходное состояние: при включении источника питания процессор вырабатывает магистральный, сигнал УСТ (Сброс), который обнуляет триггер 13, регистры 14 и счетчики 4. Б этом случае по линиям управления всех блоков 6 памяти пересылается код 00, поэтому работа всех блоков 6 памяти запрещена. Входы-выходы буферов 3 находятся с высокоимпедансном состоянии, так как сигналы с выхода триггера 13 и выходов дешифратора 15.2 пассивны (равны Лог. О).

Начало циклов обмена Ввод и Вывод выполняется одинаковым образом. Процессор на магистрали выставляет адрес и сигнал ВУ, если идет обращение к внешнему устройству. Приемо- передатчики 7 узла находятся в режиме передачи данных с магистрали процессора на внутреннюю магистраль устройства, поэтому адрес с магистрали процессора поступает на входы регистра 8 адреса, при этом на старший разрядный вход этого регистра поступает сигнал ВУ. После установления адреса процессор устанавливает на магистрали сигнал ОБК, который поступает на синхровход регистра 8 адреса, этим самым адрес с магистрали запоминается в регистре 8 на время действия сигнала от процессора ОБМ. Информация с выхода регистра 8 поступает на вход дешифратора 10. Если процессор адресуется к одному из функциональных узлов устронстна, триггеру 13, к одному из регистров 14, к одному из буферов 3 или к одному из счетчиков 4, то на выходе дешифратора 10 появляется сигнал, разрешающий работу дешифратору 11 и дешифратору 9. Так как с выхода регистра 8 на информационные входы дешифратора 9 поступает код адреса одного из функциональных узлов, то один из выходов этого депифратора активируется и тем самым разрепиет работу одному из функциональных узлов (триггеру 13 или одному из дешифраторов 12, 15.1, 15.2, 16). На этом адресная часть 1щкла любого обмена завершается .

Цикл Вывод. В этом цикле процессор после установки на магистрали сигнала ОБМ снимает с магистрали адрес и выставляет данные, предназначенные для вывода на магистраль. Эти данные через приемопередатчики 7 поступают на информационные входы функцирналь- ных узлов: триггера 13, регистров 14, . буферов 3 данных и счетчиков 4. После установления данных на магистрали процессор выставляет сигнал ДЗП, который для устройства 1 является си г налом Вывод устройства 1. Этот сигнал поступает на вход дешифратора 11 управляющих сигналов, так как работа этого дешифратора разрешена сигналом от дешифратора 10 адреса устройства, то на его выходе появляется сигнал Ответ устройства 1. Кроме того, сигнал Вывод поступает на стробиру- ющий вход триггера 13 и входы разреше ния дешифраторов 12,15.1 и 16.1. При этом если у дешифратора 9 активирован выход разрешения триггера 13, то запись информации происходит в этот триггер (на его выходе появляется Лог. О или Лог. 1), если активирован один из выходов разрешения дешифраторов 12, 15.1, 16,то строб записи появляется на одном из выходов выбранного дешифратора 12, 15.1,16, причем выбор выхода зависит от кода адреса на информационньк входах этого дешифратора, который поступает на информационные входы по группе младших разрядов адреса регистра 8 адреса. Этот строб записи заносит информацию от процессора в соответствукщий регистр или регистр 1 7 буфера данных. Процессор, получив сигнал Ответ, снимает сигнал ДЗД, устройство снимает сигнал Ответ, так как сигнал

5

Вывод устройства снят, процессор снимает данные с магистрали и сигнал ОБМ. На этом luiKn обмена Вывод заканчивается.

Цикл Ввод. В этом цикле процессор после установки в активное состояние сигнала ОБМ освобоящает магистраль адреса данных и выставляет сиг0 нал ДЧТ, который для устройства 1 является сигналом Ввод. Хотя в этом цикле может быть адресация к любому из регистров устройства, то считываются действительные данные только в

5 том случае, если идет обращение к одному из буферов 3 данных. Рассмотрим этот случай. На входы разрешения дешифратора 15.2 поступают сигналы от дешифратора 9 и сигнал Ввод. При

0 этом активируется тот выход дешифратора 15.2, код адреса которого находится на информационном входе этого дешифратора о Сигналом с активированного выхода дешифратора 15.2 разрешается передача информации с магистрали данных блоков 6 памяти через соответ- ствукишй буфер 3 данных на входы узла канальных приемопередатчиков 7. В это же время сигнал Ввод поступает

0 на вход дешифратора 11 управляющих сигналов, работа которого разрешена сигналом с выхода дешифратора 10 адреса устройства. Поэтому на выходе дешифратора 11 появляется сигнал 0т5 ват и сигнал считывания канальных

приемопередатчиков 7 узла, которые пе- реключаются на передачу информации с шин 19 на информационный вход-выход устройства 1. Данные с выхода одного

0 из буферов 3 данных (тем самым с части магистрали данных блоков 6 памяти) транслируются на магистраль процессора. Процессор, получив сигнал Ответ от устройства 1, считывает данные и

5 снимает сигнал ДЧТ, а тем самым и сигнал Ввод с магистрали. Далее устройство 1 снимает сигнал Ответ, канальные приемопередатчики 7 узла переключаются в исходное состояние, прек0 ращается передача информации через буфер 3 данных. Процессор снимает сигнал ОБМ и на этом цикл обмена Ввод заканчивается.

После считывания данных из старшего буфера 3 данных при снятии сигна5

ла ДЧТ процессором по срезу сигнала, подаваемого на счетный вход нулевого счетчика 4 с последнего выхода второго дешифратора 15.2, Происходит

изменение адреса в магистрали адреса группы 5 блоков памяти на единицу, при этом выбранный для считывания блок 6 памяти автоматически подготав- ливается для считывания следующего информационного слова, снимая необходимость в программной предустановке адреса на магистрали адреса блоков 6 памяти перед считыванием очередного информационного слова. Это также обеспечивает возможность проверки., считыванием после каждого цикла запи си.

Формула изобретения

Устройство для сопряжения процессора с группой блоков памяти, содержащее узел канальных приемоперёдатчи- ков, первый вход-выход которого является входом-выходом устройства для подключения к адресно-информадаонным воинам магистрали процессора,, регистр Адреса, триггер и группу регистров ко манд управле шя,информационные входы которых подключены к второму входу-выходу узла канальных приемопередатчикой и первым информационным входам-выходам буферных регистров данных группы, вторые информационные входы-выходы которых образуют магистраль данных устройства для подключения к информационным входам-выходам блоков памяти группы, и блок дешифрации адресов и команд, информацйонньй вход которого подключен к выходу регистра адреса, а нхровход и информационный вход стар aiei- o разряда которого являются соот- ветствукшщми входами устройства для подключения к шинам синхронизации активного устройства и выбора внешнего устройства магистрали процессора, первый выход и первый,второй входы синхронизации блока дешифрации адре- сов и команд являются соответствующими выходом и входами устройства для подключения к шинам ответа, синхронизации ввода и вывода магистрали проп цессора, синхровход триггера соединен с входом устройства для подключения

к шине синхронизации вывода магистрали процессора, а вход сброса является входом устройства для подключения к шине сброса магистрали процессора и соединен с входами сброса регистров команд управления группы, синхровходы которык соединены с первой группой выходов блока дешифрации адресов и команд, вторая и третья группы выходов, второй и третий выходы которого соединены соответственно с входами записи данных, входами разрешения передачи данных буферных регистров дан- Hbix группы, входом считьгоание узла канальных приемопередатчиков и входом записи триггера, выходом подключенного к входам разрешения чтения буферных регистров данных группы, выходц регистров команд управления группы образуют группу выходов устройства для подключения к входам задания режима соответствующих блоков памяти группы, отличающееся тем, что, с целью повышения быстродействия устройства при считьшании информации из блоков памяти группы, в него введена группа счетчиков адреса ячеек памяти, причем второй вход-выход узла канальных приемопередатчиков соединен с ин- формахщонными входами счетчиков адреса ячеек памяти группы, входы записи которых подключены к четвертой группе выходов блока дешифрации адресов и команд, а выходы образуют выходную магистраль адреса устройства для подключения к адресным входам блоков памяти группы, выход переноса каждого счетчика адреса ячеек памяти группы, кроме последнего, соединен со счетным входом последунмцего счетчика адреса ячеек памяти группы, счетный вход младшего счетчика адреса ячеек памяти группы соединен с выходом старшего разряда третьей группы выходов блока дешифрахщи адресов и команд, входы сброса счетчиков адреса ячеек памяти .группы соединены с входом устройства для подключения к шине сброса магистрали процессора,

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1501071A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Управляющая вычислительная система | 1986 |

|

SU1451711A1 |

| Устройство индикации состояния ЭВМ | 1989 |

|

SU1667067A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| УСТРОЙСТВО ЛЕКАРСТВЕННОГО УЧЕТА | 1994 |

|

RU2111534C1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых систем обработки данных и цифровых управляющих систем на основе микроЭВМ. Цель изобретения - повышение быстродействия при считывании информации процессором из группы блоков памяти. Для этого в устройство, содержащее группу буферных регистров данных, группу регистров управления блоками памяти, блок дешифрации адресов и команд, регистр адреса, узел канальных приемопередатчиков и триггер, введена группа счетчиков адреса ячеек памяти. Устройство обеспечивает работу сопрягаемых блоков памяти в режимах записи, чтения, хранения, а также стирания под управлением процессоров. Для этого устройство в течение циклов чтения, записи или стирания хранит адреса, данные и команды блоков памяти, которые устанавливаются прогрыммным путем. Введение счетчиков адреса ячеек памяти позволяет повысить быстродействие при считывании информации процессором из группы блоков памяти за счет автоматической смены адреса группы блоков памяти на следующий после завершения цикла считывания информационного слова из группы блоков памяти. 2 табл., 3 ил.

Сброс Процессор

Синхровход Процессор

Ввод Процессор

Вывод Процессор

Выборка Процессор устройств

Ответ Устройство сопряжения или ВУ

О Невыбор блока памяти (запрет блока памяти)

1 Чтение информации ид блока памяти

О Запись информации в блок памяти

1 Стирание информации - для блоков памяти на основе ППЗУ с электрическим стиранием и записью информации

Запрет блока памяти - для блоков памяти

на основе ППЗУ с электрической записью и ультрафиолетовым стиранием информации

Установка в исходное состояние Фронт сигнала - признак достоверности адреса,срез - конец обмена Вьшолняется цикл ввода данных в процессор

Выполняется цикл вывода данных из процессора Служит признаком обращения к регистрам внешних устройств

Информирует процессор о том, что данные принятые (цикл- вывод) или данные установлены на линиях АД15,....АДОО (цикл-ввод)

Таблица 2

Ck

RD

20

Редактор Н. Ядола

Составитель В. Вертлиб

Техред Л.Сердюкова Корректор м. Кучерявая

Заказ 2421

Тираж 566

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ 113035, Москва, Ж-35, Раушская наб., д. 4/5

Щ.

f

18

Риг.5

Подписное

| Авторское свидетельство СССР 1177820, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1501071A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1987-09-14—Подача