.1

входами блока памяти и адресными В:ходами ко &1утатора и блока памяти текущих адресов, подключены к информационным выходам счетчика номеров каналов управляющий вход блока регистров соединен с выходом второго элемента И, вторым входом подкдаченного к операционному выходу блока памяти, а выход блока регистрой является вь1ходом устройства.

2, Устройство по П.1, о т л ич а ю щ ё е с я тем, что блок управления формированием адреса содержит элементы ИЛИ, третий элемент И,

60366

а также элементы РАВНОЗНАЧНОСТЬ и ЗАПРЕТ, первые и вторые входы которых соединены соответственно меаду собой и подключены к первому и второму входам блока, причем первьй вход третьего элемента И соединен с третьим входом элемента ЗАПРЕТ и четвертьм входом блока, второй вход - с выходом элемента РАВНОЗЙАЧНОСТЬ, а выход - с первым выходом блока, третий вход и второй выход которого подключены соответственно к первому входу и выходу элемента ИЛИ, вторым входом соединенного с выходом элемента ЗАПРЕТ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления намоточным оборудованием | 1984 |

|

SU1273879A2 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1423982A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для обмена данными | 1981 |

|

SU1012235A1 |

| Параллельный логический мультиконтроллер | 2016 |

|

RU2634199C1 |

| Устройство для программного управления намоточным станком | 1985 |

|

SU1259216A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

1. УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ НАМОТОЧНЬМ ОБОРУДОВАНИЕМ, содержащее компаратор, памяти, .счетчик адреса и блок управления формированием адреса причём первые информационные выходы блока памяти Соединены с первыми входами компаратора, выход которого соединен с первым входом блока управления формированием адреса, второй вход которого соединен с опера1и1оиным выходом блока памяти, а первый и второй выходы блока управления формированием адреса подключены соответственно к счетному и управляющему входам счетчика адреса, евонн; выходом соединённого с первьм .адресным входом блока памяти,, о т, и ч; а ю щ е ё с я тем, что, с целью повьииения быстродействия устройства, оно содержит коммутатор, икформационньй вход которого является входом устройства, а выход подключен к второму входу компаратора, блок регистров, блок элемен-. тов ИЛИ, первый и второй элементы И, блок памяти текущих адресов, блок запуска, генератор импульсов, счетчик номеров каналов и синхронизатор, вход которого соединен с выходом генератора импульсов, а с пер. по шестой выходы синхронизатора подключены соответственно к соединенным меящу собой первому входу первого элемента И и третьему входу блока управления формированием адреса, управляющему входу блока памяти, первому входу второго элемента И, четвертому входу блока управления формированием адреса, (Л первому управляющему входу блока памяти текущих адресов и к счетному входу счетчика номеров каналов, выход переноса которого соединен с входом блока запуска, первым выходом подключенного к соединенным между собой входам сброса синхроО5 низатора и счетчика номеров канао со лов, а вторым выходом - к второму входу первого элемента И, выходСУ которого подключен к второму упо равляюн1ему входу блока памяти текущих адресов, информационные входы которого соединены с выходом счетчика адреса, информационным входом подключенного через блок элементов ИЛИ к выходам блока памяти текущих адресов и соеди 1ённым между собой вторым информационным выходом блока памяти и информационным входом- блока регистров, причем адресные входы блока регистров, объединенные с вторыми адресными

- : , 1

Изобретение относится к автоматике и вычислительной технике, и предназначено для использования в системах программного управления агрегатами для производства намоточ ных изделий.

Известно устройство для программного управления намоточным оборудованием, содержащее последователно включенные генератор импульсов, элемент ЗАПРЕТ, счетчик.адреса и блок памяти, первый выход которого подключен к одному входу компаратора, второй вход которого является входом устройства, а выход компаратора соединен с вторым входом злемейта ЗАПРЕТ, причем второй выход блока памяти является выходом устройства С

Устройство обеспечивает цикловое программное управление намоточным оборудованием, но не позволяет практически параллельно выполнять несколько программ,т.е. не обеспечивает асинхронный реясим работы отдельных групп механизмов станка.

. . . -,. , .

Наиболее близким к предлагаемому

изобретению является устройство для программного управления намоточными станками, содержащее компаратор,бло памяти, счетчик адреса и блок формирования адресар причем первый информационный выход блока памяти соединен с одним входом компаратора, выход которого соединен с первы

сходом блока формирования адреса, второй вход которого соединен с операционным выходом блока памяти, а два выхода блЬка формирования адреса подключены соответственно к счетному и управляющему входам счетчика адреса, своим выходом соединенного с первьм адресным входом блЬка паМяти.

Устройство обеспечивает логичес кое управлени е циклом работы одной группы механизмов намоточного станка и изменение цикла работы програмMHbiM путем С2 .

Недостатком известного устройства является низкое быстродействие, так как не Обеспечивается перемещение рабочих органов каждой иэ групп механизмов оборудования по самостоятельной программе, не зависящей. от состояний механизмов других групп.

Целью изобретения является повышение быстро;цействия устройства

Указанная цель достигается тем, что устройство для программного управления намоточньм оборудованием, содержащее компаратор, блок памяти, счетчик адреса и блок управления формированием адреса,причем первые информационные выходы блока памяти соединены с первьми входами компаратора, выход которого соединен с первым входом блока управления формированием адреса, второй вход которого соединен с операционным выходом блока памяти, а первьА и второй выходы блока управления ормированием адреса подключены сортдетственно к счетному и управляющему входам счётчика адреса,сво- 5 им выходом соединенного с первьи адресным входом блрка памяти, со-г держит коммутатор, информационный вход которого является ВЖУДОМ устррйства а выход подключен к вто- . 10 рому входу компаратора, блок регистров, блок элементов ИЛИ, первый и второй элементы И, блок памяти гёкутт адресов, блок запуска, ref нератор импульсов, счетчик номеров 15 каналов и синхронизатор, вход которого соединен с выходом генератора импульсов, а с первого по щес- той выходы синхронизатора подключены соответственно к соединеннь&{ 20 меяду собой первому входу первого элемента К и третьему входу блока управления формированием адреса, управляющему ВХОДУ блока памяти,первому входу второго эл емента и, чет- 25

вертому входу блока управления фор|«€рованйем адреса, первому управгляюцему входу блока памяти текущих «щресов и к. счетному входу счетчика номеров каналов выход переноса ко- ЗО торого соединен с входом блока запуска , первым выхрдом подключенного к соединенным между собой входам

сброса синхронизатсора и счетчика номеров каналов, а вторым выходом - 35 к второму входу первого элемента И, выход кртррого подк;1ючен к второму управляющему вхрду блока памяти текущих адресов, информационные входы соединены с выходом счетчи- 40 ка адреса, информацирнным входом пРД|сАюченного через блок элементов ИДИ к выходам блока памяти текуих адресов и соединенным между соIktft вторым информационным выходам 4S блР1са памяти и инфррмацион ным входам вшккарвгист-ров, причем адресные вхРТЦ).блока регистров, объединенные с вторыми адресньми входами блока памяти и адресными входами комму- 50 татора и блока памяти текущих адресов , подключены к информационным выходам счетчика номеров каналов, управлющий вход блока регистров соедийе« с выходом второго элемента И,вторым,;5 входом подключенного к операционному выхрду блока памяти,а вьвсод блока регисPPQ является выходом устррйтева. .

Кроме того, блок управления формированием адреса содержит элементы ИЖ, третий элемент И,а также элементы РАВНОЗНАЧНОСТЬ и ЗАПРЕТ, первые и вторые входы которых соединены соответственно меаду собой и подключены к первому и второму эходам блока, причем первый вход третьего элемён1;а И соединен с третьим входом элемента ЗАПРЕТ и четвертым вхрдом блока, вторрЙ вход - с выходрм элемента РАВНОЗНАЧНСЮТЬ, а быход - с первым выходом блока, третий вход и вторрй BbjkoA которого : подключены соответствейнр к первому входу и выходу элемента ШШ, ; втррам входом соединеннргб с выходо элемента ЗАПРЕТ.

Введение в устройство генератрра импульсов, синхррнйзато1 а, блрка памяти текущих адресов блока рёгистррв, элементов И,ИЛИ, счетчика H(tepoB Каналов и блока запуска, с сортветств укэдими связями Рбеспечивает управление перемещением рабочих органов каядой из групп механизмов оборудования по самостоятельной программе, не зависящей от сРстояния механизмов других груп

Выполнение блРка управления формированием адреса с помсэдыо элементов РАВНОЗНАЧНОСТЬ, ЗАПРЕТj И и ИШ с соответствующими связями обеспечивает формирование адресов очерёдньпк команд для каждой из программ устройства, т.е. постоянную или переменную последовательность выполнения ойёраци соотвётствук щйми группами мв энизмов намоточного оборудования.

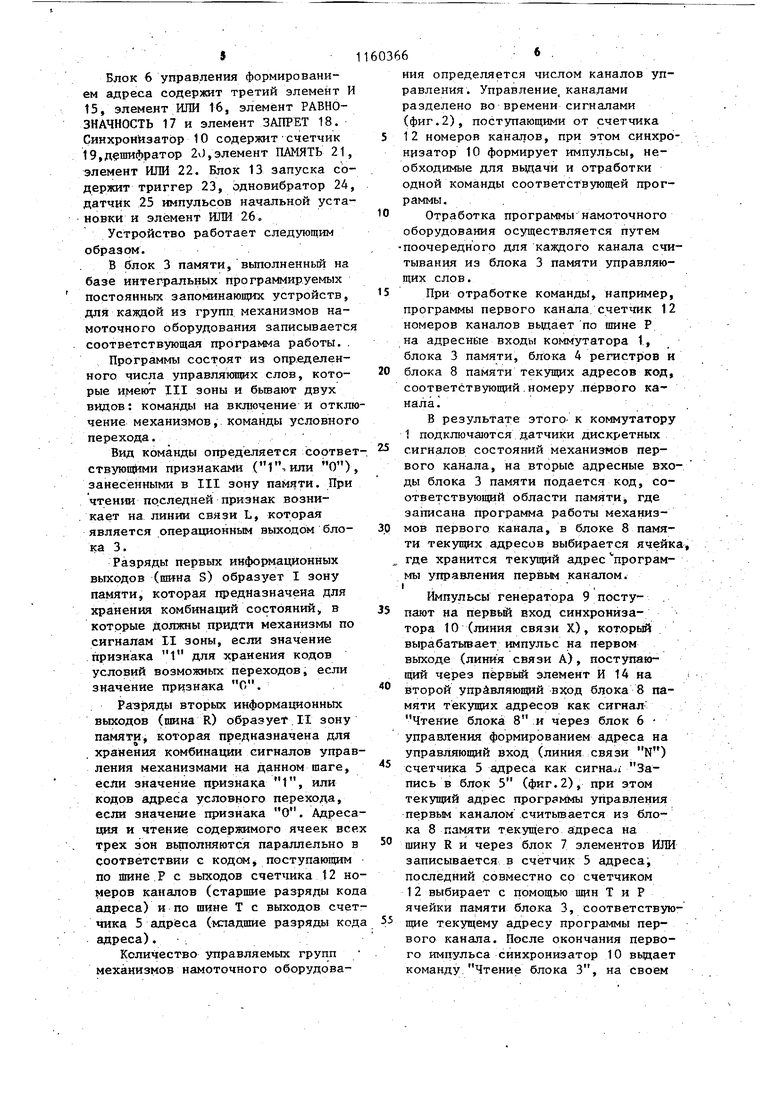

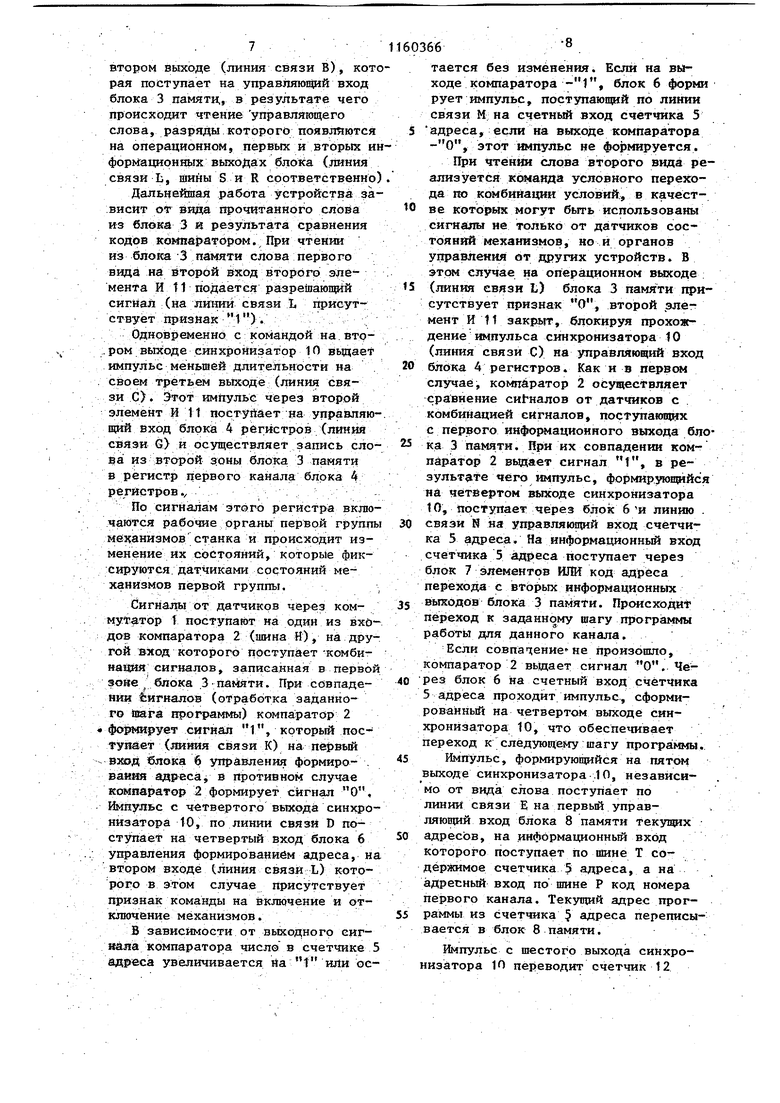

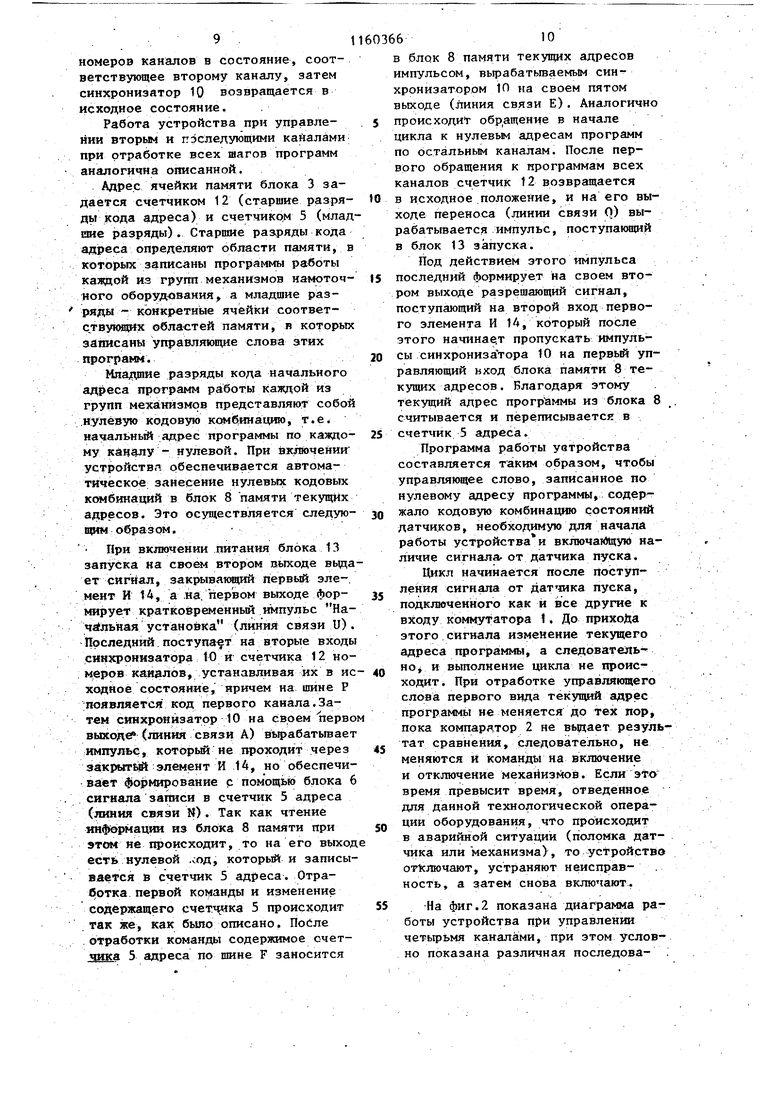

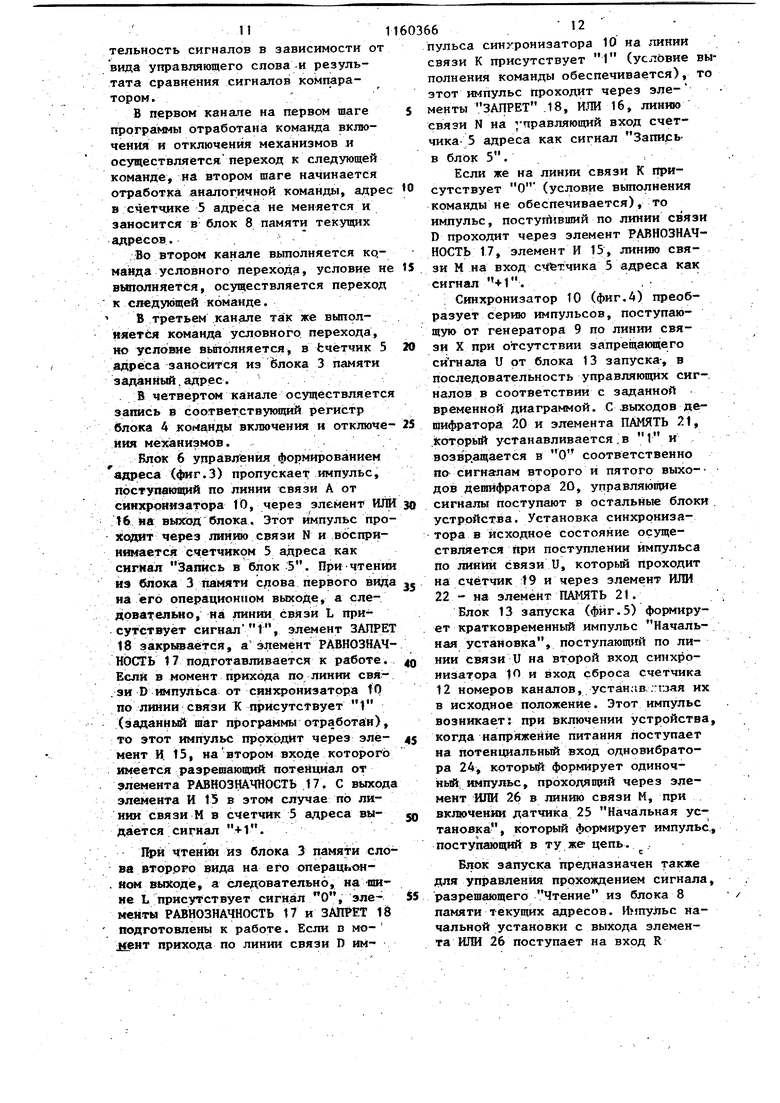

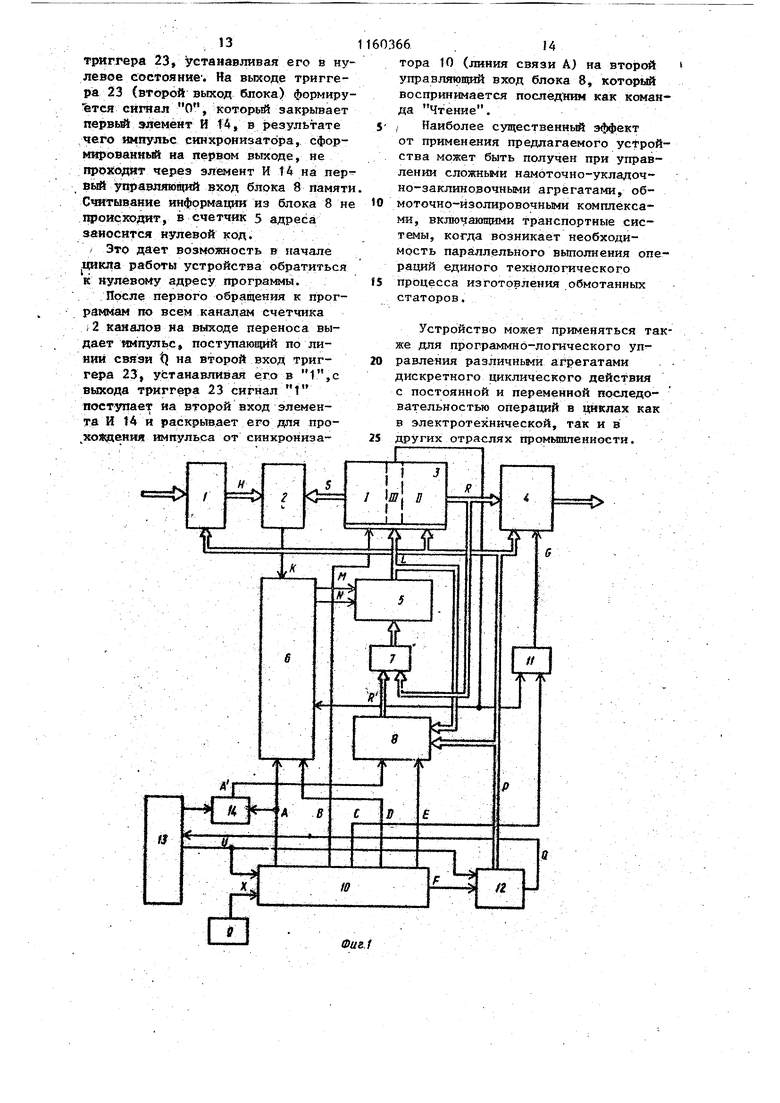

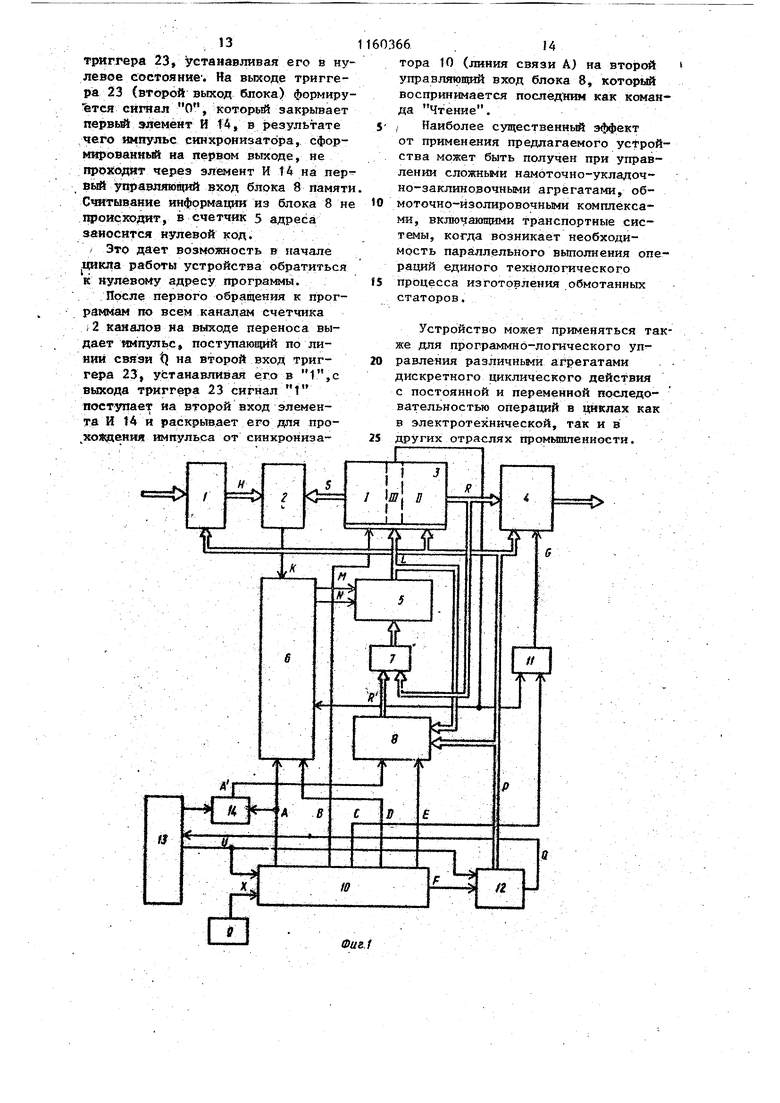

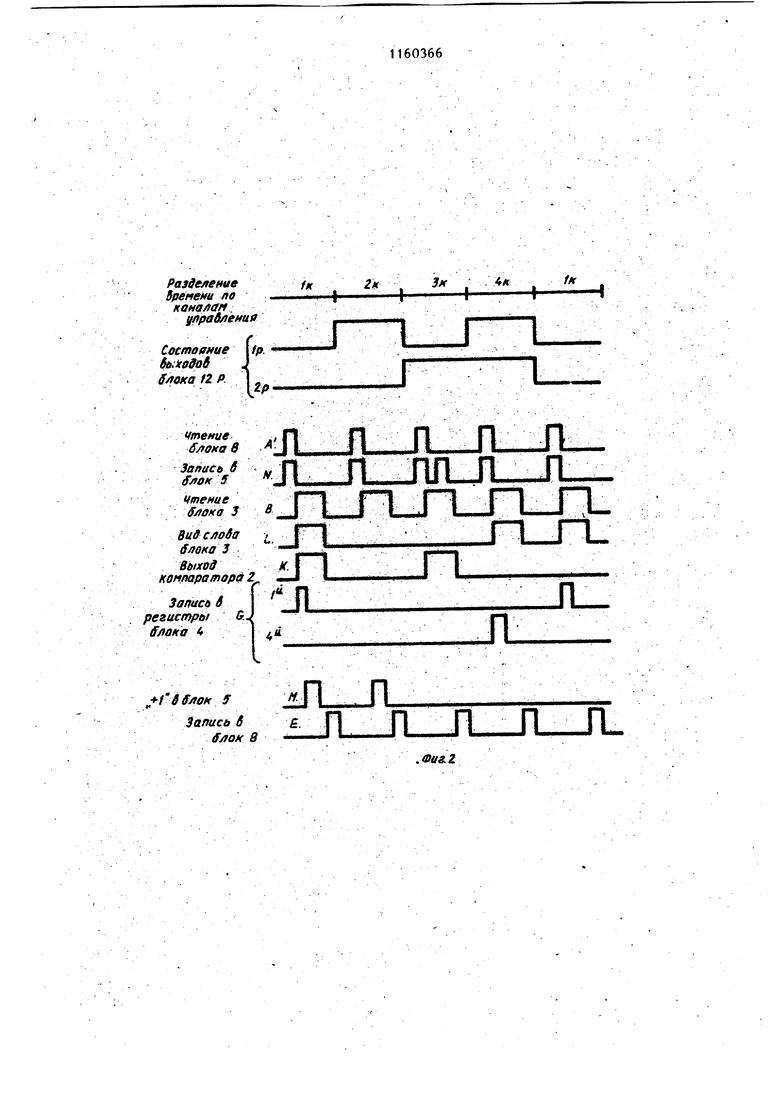

.На фиг,1 изображена функциональная схема устройства; на фиг,2 диаграмма его работыj на «гЛ функщюнальйая «схема блока управления формированием адреса на фиг,4 - то же, и диаграмма работы синхро ни атрра на фиг,5 - функцнон альнай схема блока запуска.

Устройство содержит коммутатор 1V компаратор 2, 3 памяти, блрк 4 регистров, счетчик 5 адреса, блок 6 управления формированием адреса, блок 7 элементов ИЛИ блок 8 памяти теку1цих адресов, генератор 9 импульсов, синхронизатор 10, второй элемент Ии-, 12«номеров каналов, блок 13 запуска, первый элемент И 14,

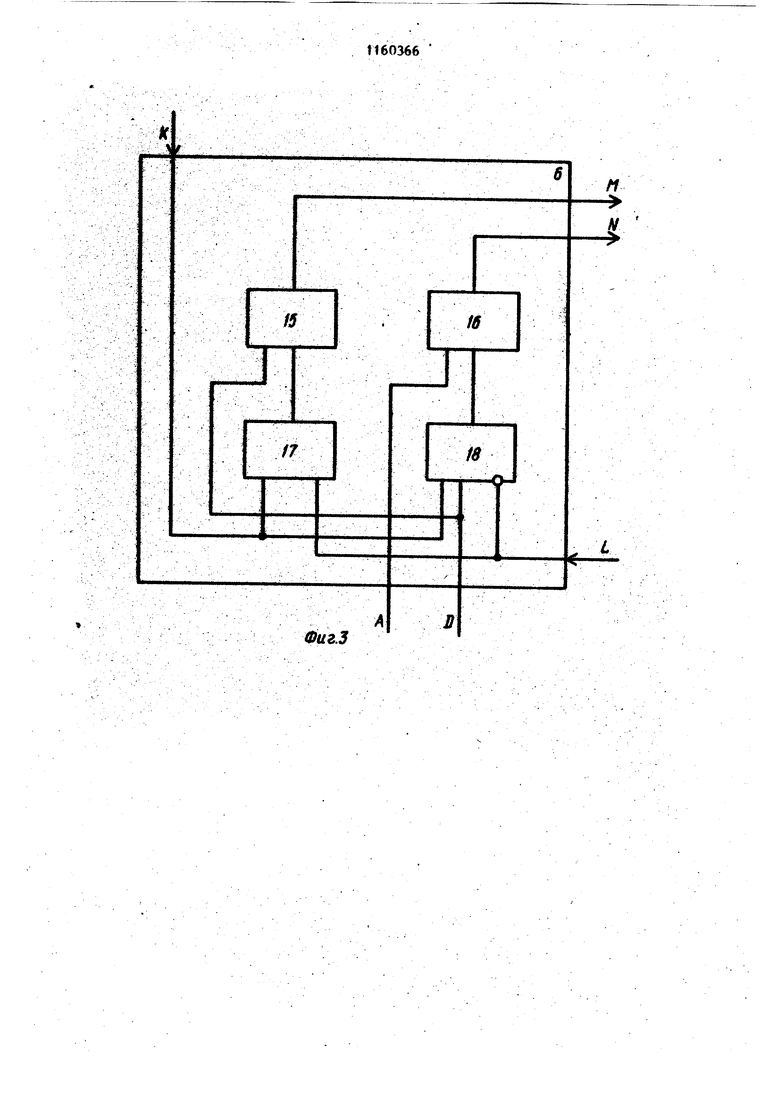

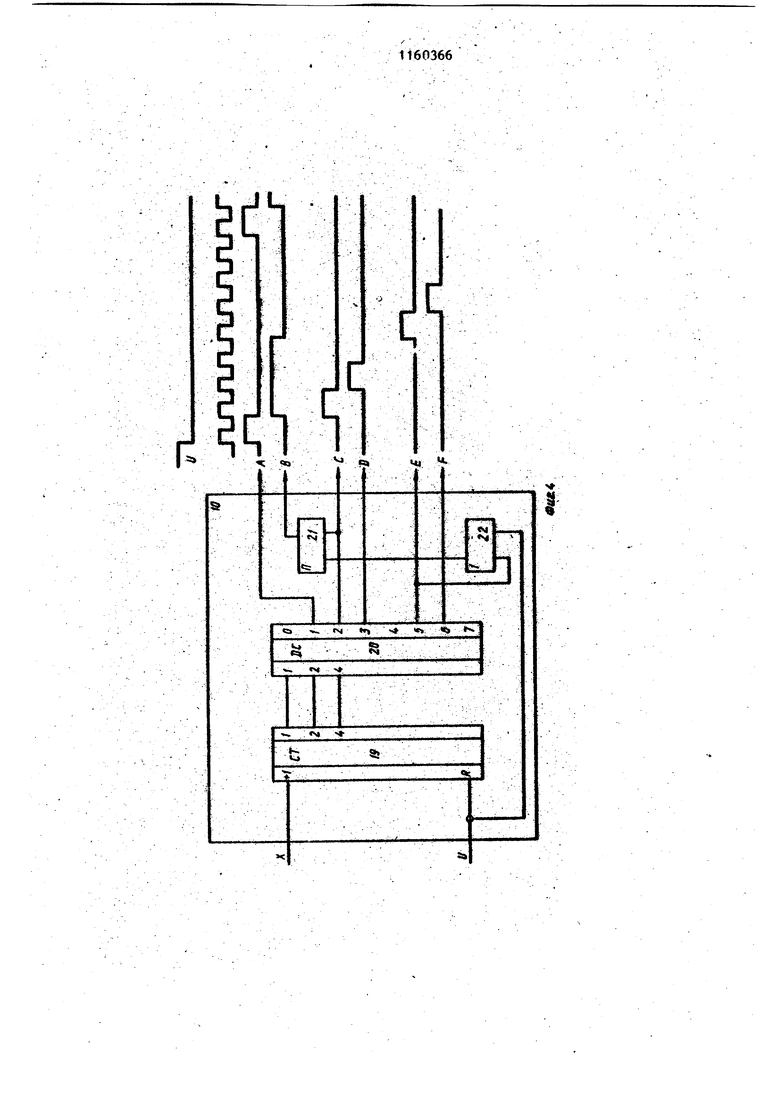

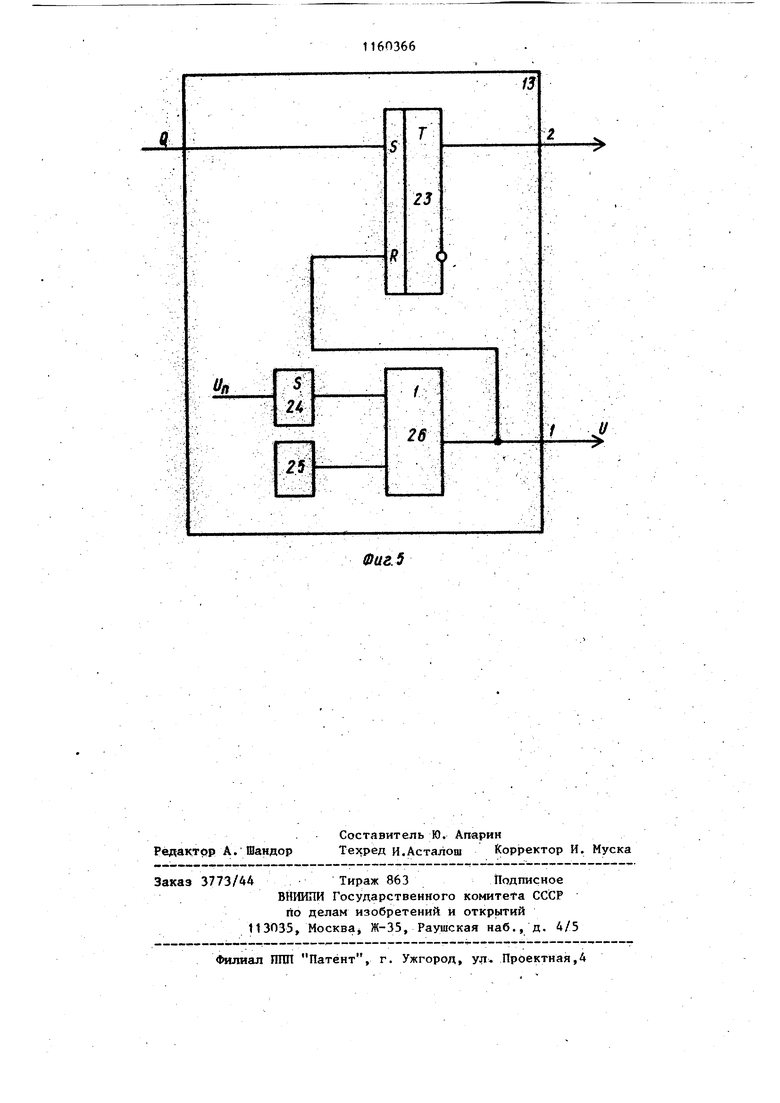

Блок 6 управления формированием адреса содержит третий элемент И 15, элемент ИЛИ 16, элемент РАВНОЗНАЧНОСТЬ 17 и элемент ЗАПРЕТ 18. Синхронизатор 10 содержит счетчик 19,дешифратор ,элeмeнт ПАМЯТЬ 21, элемент ИЛИ 22. Блок 13 запуска содержит триггер 23, одновибратор 24, датчик 25 импульсов начальной установки и элемент ИЛИ 26.

Устройство работает следующим образом.

В блок 3 памяти, вьтолненный на базе интегральных программируемых постоянных запоминающих устройств, для каждой из групп, механизмов намоточного оборудования записывается соответствующая программа работы. . Программы состоят из определенного числа управляю1цих слов, которые имеют III зоны и бьгоают двух видов: команды на включение и отключение механизмов , команды условного перехода.

Вид команды определяется соответствующими признаками (Г-.или О), занесенными в III зону памяти. При чтении последней признак возникает на линии связи L, которая является операционным выходом блока 3.

Разряды первых информационных выходов (шина S) образует I зону памяти, которая предназначена для хранения комбинаций состояний, в которые должны придти механизмы по сигналам II зоны, если значение признака 1 для хранения кодов условий возможных переходов, если значение признака О.

Разряды вторых информационных выходов (шина R) образует И зону памяти, которая предназначена для хранения комбинации сигналов управления механизмами на данном шаге, если значение признака 1, или кодов адр.еса условного перехода, если значение признака О. Адресация и чтение содержимого ячеек всех трех зон вьшолняются параллельно в соответствии с кодом поступающим по шине Р с выходов счетчика 12 номеров каналов (старшие разряды кода адреса) и по шине Т с выходов счетчика 5 адреса (младшие разряды кода адреса). .

Количество управляемых групп механизмов намоточного оборудования определяется числом каналов управления. Управление каналами разделено во времени сигналами (фиг.2), поступающими от счетчика 5 12 номеров каналов, при этом синхронизатор 10 формирует импульсы, необходимые для вьщачи и отработки одной команды соответствующей программы.

0 Отработка програ№1Ы намоточного оборудования осуществляется путем поочередного для каждого канала считывания из блока 3 памяти управляющих слов.

5 При отработке команды, например, программы первого канала, 12 номеров каналов вьщает по шине Р на адресные входы коммутатора 1., блока 3 памяти, блока 4 регистров и

0 блока 8 памяти текущих адресов код, соответствующий.номеру .первого канала . ,

В результате этого- к коммутатору 1 подключаются датчики дискретных

5 сигналов состояний механизмов первого канала, на вторые адресные входы блока 3 памяти подается код, соответствующий области памяти где записана программа работы механизр мов первого канала, в блоке 8 памяти теку1щх адресов выбирается ячейка, „ где хранится текущий адрес программы управления первьм каналом. I - : . . - Импульсы генератора 9 поступают на первьй вход синхронизатора 10 (линия связи X), который вьфабатывает импульс на первом выходе (линия связи А), поступающий через первый элемент И 14 на второй управляющий вход блока 8 памяти текущих адресов как сигнал Чтение блока 8 и через блок 6 управления формированием адреса на управляющий вход (линия связи N)

счетчика 5 адреса как сигнал Запись в блок 5 (фиг.2), при этом текущий адрес програьол управления первым каналом .считьшается из блока 8 памяти текущего а:дреса на

° пгану R и через блок 7 элементов ИЛИ записывается в счетчик 5 адреса; последний .совместно со счетчиком 12 выбирает с помощью шин Т и Р ячейки памяти блока 3, соответствующие текущему адресу программы первого канала. После окончания первого импульса синхронизатор 10 выдает команду.Чтение блока 3, на своем

втором выходе (линия связи В), которая поступает на управляющий вход блока 3 памяти., в результате чего происходит чтение управляющего слова, разряды которого появляются на операционном, первых и вторых информ ационшк выходах блока (линия связи Ь, шины S и R соответственно)

Дальнейшая работа устройства зависит от вида прочитанного слова из блока 3 8 результата сравнения кодов компаратором. При чтении из блока 3 памяти слова первого вида на йторой вход второго эдемента И 11 подается разре{аающий сигнал (на лшдай связи L присутствует признак 1) .

Одновременно с командой на втр.ром выходе синхронизатор 10 вьщает импульс меньшей длительности на . своем третьем выходе (линия связи С). Этот импульс через второй элемент И 11 постуйает на управляющИй Вход блока 4 регистров (линия связи G) и осуществляет запись слова из второй зоны блока 3 памяти в регистр первого канала блока 4 регистров./

По сигналам этого регистра включаются рабочие органы первой группы механизмовстанка и происходит изменение их состояний, которые фиксируются датчиками состояний механизмов первой группы.

Сигналы от датчиков через комМУШтор 1 поступают на один из входов компаратора 2 (шина Н), на другой вход которого поступает комбинация сигналов, записанная в первой зове блока 3пайяти. При сов паденйн Сигналов (отработка заданного teajpa программы) компаратор 2 формирует сигнал 1, который поступает (линия связи К) на первый блока 6 управления формиро- . ваиия адреса, в противном случае компаратор 2 формирует сигнал О, Йипульс с четвертого выхода синхронизатора 10, по линии связи D поступает на четвертый вход блока 6 управления формированием адреса, на втором входе (линия СВЯЗИ L) которого в этом случае присутствует признак команды на включение и отключение механизмов .

В зависимости от выходного сигаала компаратора число в счетчике 5 адреса ув еличивается йа 1 или ос60366 .

тается без изменения. Если на выходе компаратора , блок 6 форми рует импульс, поступающий по линии связи М на счетный вход счетчика 5 5 адреса, если на выходе компаратора , этот импульс не формируется.

При чтении слова второго вида реализуется команда условного перехода ио комбинация условий, в качество ве которых могут быть использованы сигналы не только от датчиков состояний механизмов, но и органов управления от других устройств. В этом случае на операционном выходе : 5 (линия связи L) блока 3 памяти присутствует признак О, второй элемент И 11 закрыт, блокируя прохождение 1в спульса синхронизатора 10 (линия связи С) на управляющий вход 20 блока 4 регистров. Как и в nepacw случае, компаратор 2 осуществляет сравнение cи нaлoв от датчиков с комбинацией сигналов, поступактдах с первого информационного выхода блока 3 памяти. Ири их совпадении компаратор 2 вьздает сигнал 1, в результ те чего 1шпульс, формируюпщйся на выходе синхронизатора 10, iioiCTynaeT через блок 6 и линию .

0 связи N на управляющий вход счётчика 5 адреса. На информационный вход счетчика 5 адреса поступает через блок 7 элементов ИЛИ код адреса , перехода с вторых информационных

5 выходов блока 3 памяти. Происходит переход к заданному шагу программы работы для данного канала.

Если совпадениене произошло, компаратор 2 вьДает сигнал О. Через блок 6 на счетный вход счётчика 5 адреса проходит импульс, сформированный на четвертом выходе синхронизатора 10, что обеспечивает переход к следующему шагу программы.

5 Импульс, формируюпр1йся на пятом выходе синхронизатора .10, независимо от вида слова поступает по линий связи Е на первый управляюищй вход блока 13 памяти текущих

0 адресов, на информационный вхОд которого поступает по шине Т содёрзшмое счетчика 5 адреса, а на адресный вход по шине Р код номера первого канала. Текущий адрес программы из счетчика 5 адреса переписывается в блок 8 памяти..

Шпульс с шестого выхода синхронизатора Ю переводит счетчик 12

номеров каналов в состояние, соответствующее второму каналу, затем синхронизатор 10 возвращается в исходное состояние,

Работа устройства при управле- 5 НИИ вторым и пэследутощими каналами при отработке всех шагов программ аналогична описанной.

Адрес ячейки памяти блока 3 з адается счетчиком 12 (старшие разря- Ю ды кода адреса) и счетчикрм 5 (младшие разряды). Старшие рааряды кода адреса определяют области памяти, в которых записаны программы работы каящой из групп механизмов намоточ- 15 ного оборудования а младшие разряды - конкретные ячейки соответс.твукицйх областей памяти, в которых записаны управляющие слова этих программ.20

Младшие разряды кода начального адреса программ работы каждой из групп механизмов представляют собой .нулевую кодовую комбина цию, т.е. начальньй адрес программы по каждо- 25 му КЙН4ЛУ - нулевой. При включении устройства обеспечивается автоматическое занесение нулевых кодовых комбинаций в блок 8 памяти текущих адресов. Это осуществляется следую- зо щим образом.

При включении питания блока 13 запуска на своем втором выходе вьщает сигнал, закрывающий первьй эле-. мент И 14, а .на первом выходе фор- 35 трует кратковременный импульс Начйдьная установка (линия связи U). Последний.поступает на вторые входы синхронизатора Ю и счетчика 12 но: меров каналов, устанавливая их в ис- 40 ходНое состояние, причем на шине Р появляется код первого канала.Затем синхрон изатрр 10 на своем liepBOM выходе (линия связи А) вырабатывает импульс, который не проходит через 45 закрытий элемент И 14, но обеспечивает формирование с помощью блока 6 сигнала записи в счетчик 5 адреса (линия связи N). Так как чтение информации из блока 8 памяти при 50 9Т( не происходит, то на его выходе есть нулевой .;од, который и записывается в счетчик 5 адреса. ОтраiSoTKa первой и изменение содержащего счетл ка 5 происходит 55

.так же, как было описано. После отработки команды содержимое счетчика 5 адреса по шине F заносится

в блок 8 памяти текущих адресов импульсом, вырабатываемым синхронизатором Ш на своем пятом выходе (линия связи Е). Аналогично происходит обр ащение в начале цикла к нулевым адресам программ по остальным каналам. После первого обращения к программам всех каналов счетчик 12 возвращается в исходное положение, и на его выходе переноса (линии связи 0) вырабатывается импульс, поступающий в блок 13 запуска.

Под действием этого импульса последний формирует на своем втором выходе разрешающий сигнал, поступающий на второй вход первого элемента И 14, который после этого начинает пропускать иМпульсы синхронизатора 10 на первый управляющий вход блока памяти 8 текущих адресов . Благодаря этому текущий адрес прогрТаммы из блока 8 считывается и переписывается в счетчик 5 адреса.

Программа работы увтройства составляется таким образом, чтобы управляющее слово, записанное по нулевому адресу программы, содержало кодовую комбинацию состояний датчиков, необходимую для начала работы устройства и включакМцую наличие сигнала- от датчика пуска.

Цикл начинается после поступления сигнала от датчика пуска, подключенного как и iace другие к входу коммутатора t. До прихоДа этого сигнала изменение текущего адреса программы, а следовательHOj и выполнение цикла не происходит. При отработке управляющего слова первого вида текущий адрес программы не меняется до тех пор, пока компаратор 2 не вьщает результат сравнения, следовательно, не меняются И команды на включение и отключение мехайизг ов. Если это время превысит время, отведенное для данной технологической операции оборудования, что происходит в аварийной ситуации (поломка датчика или механизма), то устройство отключают, устраняют неисправ- . ность, а затем снова включают.

На фиг.2 показана диаграмма работы устройства при управлении четьфьмя каналами, при этом условно показана различная последова11 1

тельность сигналов в зависимости от вида управляющего слова-и результата сравнения сигналов компаратором.

В первом канале на первом шаге программы отработана команда включения и отключения механизмов и осуществля ется переход к следующей команде, на втором шаге начинается отработка аналогичной команды, адрес в счетчике 5 адреса не меняется и заносится в блок 8 памяти текущих адресов.

Во втором канапе вьтолняется ко.манда УСЛОВНОГО перехода, условие не вьтолняется, осуществляется переход к следующей команде. В третьем канале так же выполняется команда условного перехода, но условие выполняется, в Ьчетчик 5 адреса заносится из Ълока 3 памяти заданный,адрес.

. В четвертом ка1нале осуществляется запись в соответствующий регистр блока 4 команды включения и отключения механизмов.

Блок 6 управления формированием адреса (фиг.3) пропускает импульс, поступающий по линии связи А от синхронизатора 10, через злемент ИЛИ 16 йа выход блока. Этот импульс проводит через линию связи N и воспринимается счетчиком 5 адреса как сигнал Запись в блок 5. При чтении иэ блока 3 памяти сдова первого вида на его операционном выходе, а следрвателыю, на линии связи L присутствует сигнал , элемент ЗАПРЕТ 18 закрывается, а элемент РАВНОЗНАЧНОСТЬ 17 подготавливается к работе. Если в момент прихода по линии свя.зи D импульса от синхронизатора 10 по линии связи К присутствует 1 (заданный шаг программы отработан), то этот импульс проходит через элемент И. 15, на втором входе которого имеется разрешающий потенциал от элемента РАВНОЗНАЧНОСТЬ 17, С выхода элемента И 15 в этом случае по линии связи М в счетчик 5 адреса выдается сигнал -И.

чтении из блока 3 памяти слова вторрго вида на его операцьонном выходе, а следовательно, на iiiHне L присутствует сигнал О, элементы РАВНОЗНАЧНОСТЬ 17 и ЗАПРЕТ 1)3 подготовлены к работе. Если в молент прихода по линии связи D им0366 . ,

пульса синхронизатора 10 на линии связи К присутствует 1 (условие выполнения команды обеспечивается), то этот импульс проходит через элементы ЗАПРЕТ .18, ИЛИ 16, линию связи N на управляющий вход счетчика- 5 адреса как сигнал Записьв блок 5.

Если же на связи К присутствует (условие вьшолнения команды не обеспечивается), то импульс, постугй1вший по линии связи D проходит через злемент РАВНОЗНАЧНОСТЬ 17, элемент И 15, линию связи М на вход счетчика 5 адреса как сигнал +1..

; Синхронизатор 10 (фиг.А) преобразует серию импульсов, поступающую от генератора 9 по линии связи X при отсутствии запрещающего сигнала и от блока 13 запуска-, в последовательность управляющих сигналов в соответствии с заданной временной диаграммой. С .выходов де5 (йифратора 20 и элемента ПАМЯТЬ 21, .Который устанавливается,в 1 и возвращается в О соответственно по сигналам второго и пятого выхо-дов дешифратора 20, управляющие

0 сигналы поступают в остальные блоки . устройства. Установка синхронизатора в исходное состояние осуществляется йри поступлении импульса по линии связи и, который проходит

J на счетчик 19 и через элемент ИЛИ 22 - на элемент ПАМЯТЬ 21.

Блок 13 запуска (фиг.5) формирует кратковременный импульс Начальная установка, поступающий по ли0 НИИ связи и на второй вход синхронизатора 10 и вход сброса счетчика 12 номеров каналов, устан;1в.;:глая их в исходное положение. Этот импульс возникает: при включении устройства,

5 когда напряжение питания поступает на потенциальный вход одновибратора 24, который формирует одиночный, импульс, проходящий через элемент ИЛИ 26 в линию связи М, при

0 включении датчика 25 Начальная установка , который формирует импульс., поступающий в тУ же цепь.

Блок запуска предназначен такхе для управления прохождением сигнала, 5 разрешающего Чтение из блока 8 памяти текущих адресов. Илпульс начальной установки с выхода элемента ИЛИ 26 поступает на вход R

13

триггера 23, устанавливая его в нулевое состояние . На выходе триггера 23 (второй выход блока) формиру ется сигнал О, которой закрывает первьй элемент И 14, в результате чего импульс синхронизатора, сформировайньй на перовом выходе, не проходит через элемент И 14 на пер В1 Управляющий вход блока 8 памяти Считывание информация из блока 8 не происзсадит, в счетчик 5 адреса заносится нулевой код.

/ Это дает возможность в начале дикяа работы устройства обратиться к нулевому адресу программы.

После первого обращения к программам по всем каналам счетчика

i 2 каналов на выходе переноса выдает импульс, поступающий по линии связи tj на второй вход триггера 23, устанавливая его в 1,с выхода триггера 23 сигнал 1 поступает на второй вход элемента И t4 и раскрывает его для прохождения импульса от cKHxpoHHsa0366 . 14

тора 10 (линия связи А) на второИ управляющий вход блока В, который воспринимается последним как команда Чтение.

5 / Наиболее существенный эффект от применения предлагаемого устройства может быть получен при управлении сложньми намоточно-укладочно-заклиновочными агрегатами, обмоточно-изолировочными комплексами, включающими транспортные системы, когда возникает необходимость параллельного вьтолнения операций единого технологического процесса изготовления обмотанных статоров.

Устройство может применяться также для программно-логического управления различньми агрегатами дискретного циклического действия с постоянной и переменной последовательностью операций в циклах как в электротехнической, так и в других отраслях промыпшенности.

Разделение Кренем по каналвн yflpa&aeHuff

Соствание &л;ио9р8 Илока П Р. Чтение , S/юна $ Запись 6 „ f/iOK S Чтение Злака 3 Вид слаба блока 3 выход конварвтора Z Залась Л регистры 5. ff/HJK «

/АЗк

4

+teff/raK f

Запись 6 в

1

IS

n

Фиг.З

n

4

16

Ш

dl

п

к :яо;

«VI

.- - К| - .. ,; .:-«

V. р.

ч

г

«М:

Фиг. 5

Авторы

Даты

1985-06-07—Публикация

1983-04-08—Подача