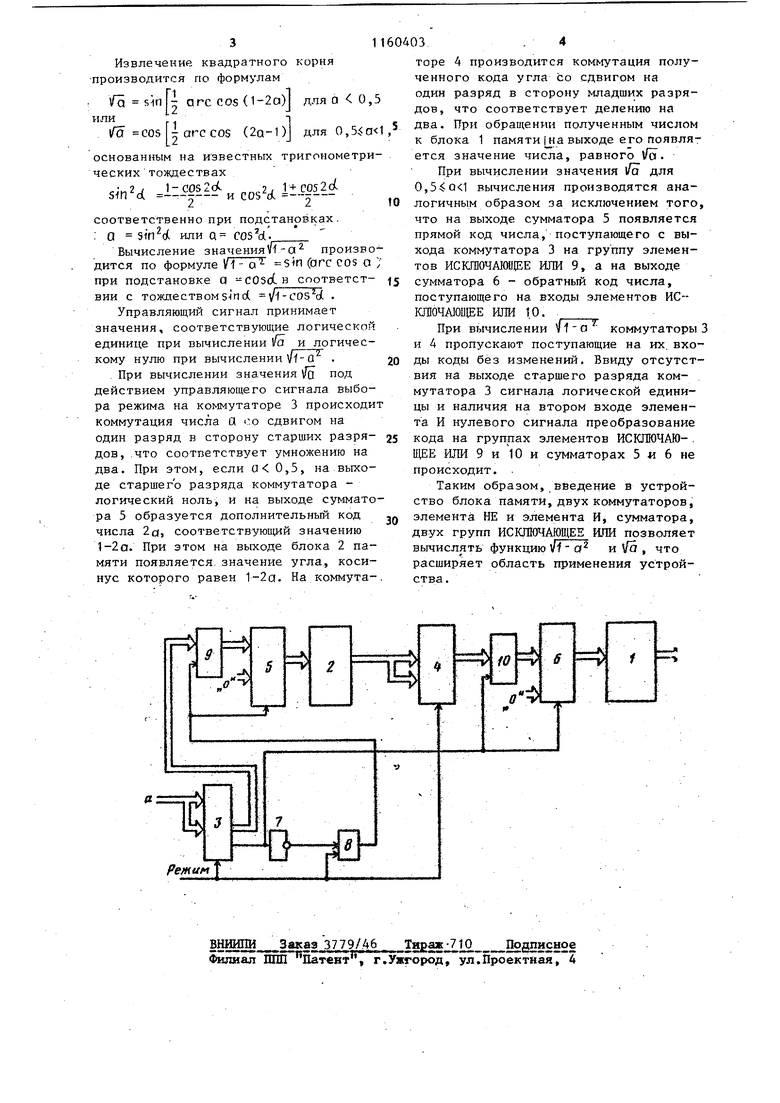

Изобретение относится к вычислительной технике и может быть исполь зовано в арифметических устройствах специализированных вычислительных машин. Известно устройство для извлечен квадратного корня матричного типа, основанное на представлении подкоре ного числа в виде сумму членов ряда последовательных нечетных чисел 1 Недостатком этого устройства является Ограниченная разрядности представления числа. Увеличение раз рядности влечет за собой увеличение времени вычисления в два раза за счет необходимости повторных вычислений. Кроме того, лри извлечении квадратного корня из мантиссы проис ходит уменьшение точности. Наиболее близким по назначению и технической сущности к изобретени является устройство для извлечения квадратного корня, содержащее блок памяти тригонометрических функций, сумматор, сдвиговый регистр, умножитель и адресный регистр. При этом на первый вход сумматора, подается сигнал, соответствующий значению подкоренного числа, на второй вход подается логическая единица, выход .сумматора соединен с входом сдвигов го регистра, выход которого подключен к первому входу умножителя. Кро ме того, сигнал, соответствующий значению подкоренного числа, подает -ся на вход адресного регистра, выхо которого подключен к адресному входу ПЗУ, а выход ПЗУ подключен к второму входу умножителя, выход которого является выходом устройства 23 . Недостатками известного устройства являются ограниченные функциональные возможности, которые не обе печивают вычисления значений , а также необходимость специальной организации ПЗУ для адресации значе ниями подкоренного числа и необходи мость модификации устройства при извлечении квадратного корня из чис ла, меньшего единицы, что приводит к увеличению аппаратурных затрат и снижению быстродействия. Цель изобретения - расширение функциональных возможностей устройства путем получения возможности вычисления функции /1-а помимо функцйиУа . Поставленная цель достигается тем, что устройство для извлечения квадратного корня, содержащее первый, блок памяти ипервьм сумматор, дополнительно содержит второй блок памяти, первый и второй коммутаторы, второй сумматор, элемент НЕ, элемент И, две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вход выбора режима устройства соединен с управляющими входами первого и второго коммутаторов и первым входом элемента И, выход которого соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы и входом переноса младщего разряда первого сумматора, разрядные входы первого слагаемого которого соединены соответственно свыходами элементов ИСКЛЮЧАЮЩЕЕ. ИЛИ первой группы, вторые входы которых соединены соответственно с выходами первого коммутатора, вы::од старшего разряда которого соединен с первыми входами элементов ИСКПЮЧАЮГЦЕЕ ИЛИ второй группы, входом переноса младшего разряда второго сумматора и входом элемента НЕ, разрядные входы первого слагаемого второго сумматора соединены соответственно с выходами элементов ИСКЛЮЧАЕШЦЕЕ ИЛИ второй группы, вторые входы которых соединены соответственно с выходами второго коммутатора, выход 1 -го разряда первого блока памяти соединен с i-м и (1-1 )-м информационными .входами второго коммутатора (f-1,П , где П разрядность операндов), адресные входы первого блока памяти соединены соответственно с выходами первого сумматора, выход элемента НЕ соединен с вторым входом элемента И, выходы второго сумматора соединены с адресными входами второго блока памяти, вход Т-го разряда операнда устройства соединен с I-M и (l+D-M входами первого коммутатора, входы второго слагаемого первого и второго сумматоров соединены с шиной логического нуля устройства. На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит блоки 1 и 2 памяти, коммутаторы 3 и 4, сумматоры 5 и б, элемент НЕ 7, элемент И 8, группы элементов ИСКЛЮЧАЮКЩЕ ИЛИ 9 и 10. . Устройство работает следующим образом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Вычислительное устройство | 1983 |

|

SU1080135A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1108440A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Устройство для вычисления функции arctg y/x | 2017 |

|

RU2642385C1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1104511A1 |

| Устройство для формирования дуг и окружностей на экране телевизионного индикатора | 1990 |

|

SU1800476A1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1089578A1 |

| Устройство для извлечения квадратного корня | 1989 |

|

SU1626253A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее первый блок памяти, первый сумматор, отличающееся тем, что, с целью расширения функциональных возможностей путем получения возможности вычисления функции || - а по мимо функции fa, оно дополнительно; содержит второй блок пймяти, первый и второй коммутаторы, второй сумматор, элемент НЕ, элемент И, две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вход выбора режима устройства соединен с управляющими входами первого и второго коммутаторов и первым входом элемента И, выход которого соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ пе.рвой группы и входом переноса младшего разряда первого сумматора, разрядные входы первого слагаемого которого соединены соответственно с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, вторые входы которых соединены соответственно с выходами первого коммутатора, выход старшего разряда которого соединен с первыми ВХОДАМИ элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, входом переноса младшего разряда второго сумматора и входом элемента НЕ, разрядные входы первого слагаемого второго сумматора соединены соответственно с выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы которых соединены соответственно с выходами второго коммутатора, выход f-ro разряда первого блока памяти соединен с I-м и (l-D-M ин(Л формацио1 ными входами второго коммутатора (, п , где п разрядность операндов), адресные входы первого Плока памяти соединены соответственно с выходами первого сумматора, выход элемента НЕ соединен с вторым входом элемента И, выходы второго сумматора соединены с адресными входами второго блока памяти, вход |,-го разряда операнда устройства соединен с i-м и (I+D-M входами первого ком05 О мутатора , входы второго слагаемого о первого и второго сумматоров соединены С шиной логического нуля устройства. 00

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для извлечения квадратного корня | 1979 |

|

SU924702A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Rom-stored sine functions yield scfuare roots | |||

| - Electronics, 48, № 23, 1975, p | |||

| Способ подпочвенного орошения с применением труб | 1921 |

|

SU139A1 |

Авторы

Даты

1985-06-07—Публикация

1983-06-01—Подача