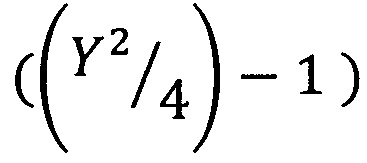

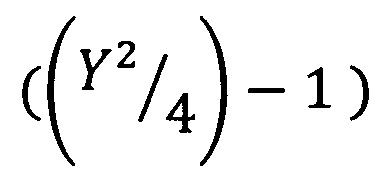

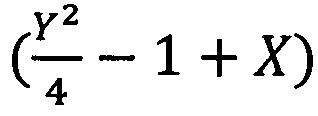

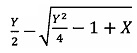

Изобретение относится к цифровой вычислительной технике и может быть использовано для ускоренного вычисления функции  .

.

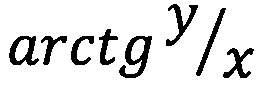

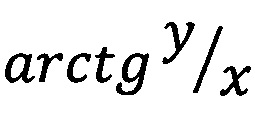

Известны устройства для вычисления функции  [а.с. 1067510 СССР, 1984 г.; а.с. 1206767 СССР, 1984 г.]. К недостатку известных устройств можно отнести низкую точность вычисления.

[а.с. 1067510 СССР, 1984 г.; а.с. 1206767 СССР, 1984 г.]. К недостатку известных устройств можно отнести низкую точность вычисления.

Наиболее близким по технической сущности к данному изобретению является устройство для вычисления функции  [а.с. 1297041 СССР, 1987 г.], содержащее регистр аргумента X, регистр аргумента Y, блок синхронизации, сумматор, два коммутатора, три буферных регистра, регистр результата, причем выходы первого и второго коммутаторов соединены с входами первого и второго слагаемых сумматора соответственно, выход которого соединен с информационными входами регистра результата, первого буферного регистра, первый и второй выходы блока синхронизации соединены соответственно с управляющими входами первого и второго коммутаторов. Кроме того, оно содержит вычитатель, блок памяти

[а.с. 1297041 СССР, 1987 г.], содержащее регистр аргумента X, регистр аргумента Y, блок синхронизации, сумматор, два коммутатора, три буферных регистра, регистр результата, причем выходы первого и второго коммутаторов соединены с входами первого и второго слагаемых сумматора соответственно, выход которого соединен с информационными входами регистра результата, первого буферного регистра, первый и второй выходы блока синхронизации соединены соответственно с управляющими входами первого и второго коммутаторов. Кроме того, оно содержит вычитатель, блок памяти  , блок памяти значений квадратного корня, первый и второй блоки памяти значений арктангенса, выходы которых соединены с первыми информационными входами первого и второго коммутаторов соответственно, вторые входы которых соединены с выходами регистра аргумента Y и регистра аргумента X соответственно, третьи информационные входы первого и второго коммутаторов соединены с выходами блока памяти значений

, блок памяти значений квадратного корня, первый и второй блоки памяти значений арктангенса, выходы которых соединены с первыми информационными входами первого и второго коммутаторов соответственно, вторые входы которых соединены с выходами регистра аргумента Y и регистра аргумента X соответственно, третьи информационные входы первого и второго коммутаторов соединены с выходами блока памяти значений  и второго буферного регистра соответственно, адресный вход блока памяти значений

и второго буферного регистра соответственно, адресный вход блока памяти значений  соединен с выходом регистра аргумента Y, выходы первого и второго коммутаторов соединены с входами уменьшаемого и вычитаемого вычитателя соответственно, выход которого соединен с информационным входом третьего буферного регистра, выход которого соединен с адресным входом второго блока памяти значений арктангенса, выход сумматора соединен с адресным входом блока памяти значений квадратного корня, выход которого соединен с адресным входом второго буферного регистра, третий, четвертый и пятый выходы блока синхронизации соединены с входами синхронизации соответственно первого, второго и третьего буферных регистров, выход первого буферного регистра соединен с адресным входом первого блока памяти значений арктангенса.

соединен с выходом регистра аргумента Y, выходы первого и второго коммутаторов соединены с входами уменьшаемого и вычитаемого вычитателя соответственно, выход которого соединен с информационным входом третьего буферного регистра, выход которого соединен с адресным входом второго блока памяти значений арктангенса, выход сумматора соединен с адресным входом блока памяти значений квадратного корня, выход которого соединен с адресным входом второго буферного регистра, третий, четвертый и пятый выходы блока синхронизации соединены с входами синхронизации соответственно первого, второго и третьего буферных регистров, выход первого буферного регистра соединен с адресным входом первого блока памяти значений арктангенса.

К недостатку известного устройства относится низкая точность вычисления функции  .

.

Задача настоящего изобретения является совершенствование возможностей устройства для вычисления функции  .

.

Технический результат - получение более точного значения арктангенса.

Технический результат достигается предложенным устройством для вычисления функции  , содержащим регистр аргумента X, регистр аргумента Y, блок синхронизации, сумматор, два коммутатора, три буферных регистра, регистр результата, причем выходы первого и второго коммутаторов соединены с входами первого и второго слагаемых сумматора соответственно, выход которого соединен с информационными входами регистра результата, первого буферного регистра, первый и второй выходы блока синхронизации соединены соответственно с управляющими входами первого и второго коммутаторов, вычитатель, блок памяти значений

, содержащим регистр аргумента X, регистр аргумента Y, блок синхронизации, сумматор, два коммутатора, три буферных регистра, регистр результата, причем выходы первого и второго коммутаторов соединены с входами первого и второго слагаемых сумматора соответственно, выход которого соединен с информационными входами регистра результата, первого буферного регистра, первый и второй выходы блока синхронизации соединены соответственно с управляющими входами первого и второго коммутаторов, вычитатель, блок памяти значений  , блок памяти значений квадратного корня, первый и второй блоки памяти значений арктангенса, выходы которых соединены с первыми информационными входами первого и второго коммутаторов соответственно, вторые входы которых соединены с выходами регистра аргумента Y и регистра аргумента X соответственно, третьи информационные входы первого и второго коммутаторов соединены с выходами блока памяти значений

, блок памяти значений квадратного корня, первый и второй блоки памяти значений арктангенса, выходы которых соединены с первыми информационными входами первого и второго коммутаторов соответственно, вторые входы которых соединены с выходами регистра аргумента Y и регистра аргумента X соответственно, третьи информационные входы первого и второго коммутаторов соединены с выходами блока памяти значений  и второго буферного регистра соответственно, адресный вход блока памяти значений

и второго буферного регистра соответственно, адресный вход блока памяти значений  соединен с выходом регистра аргумента Y, выходы первого и второго коммутаторов соединены с входами уменьшаемого и вычитаемого вычитателя соответственно, выход которого соединен с информационным входом третьего буферного регистра, выход которого соединен с адресным входом второго блока памяти значений арктангенса, выход сумматора соединен с адресным входом блока памяти значений квадратного корня, выход которого соединен с адресным входом второго буферного регистра, третий, четвертый и пятый выходы блока синхронизации соединены с входами синхронизации соответственно первого, второго и третьего буферных регистров, выход первого буферного регистра соединен с адресным входом первого блока памяти значений арктангенсов.

соединен с выходом регистра аргумента Y, выходы первого и второго коммутаторов соединены с входами уменьшаемого и вычитаемого вычитателя соответственно, выход которого соединен с информационным входом третьего буферного регистра, выход которого соединен с адресным входом второго блока памяти значений арктангенса, выход сумматора соединен с адресным входом блока памяти значений квадратного корня, выход которого соединен с адресным входом второго буферного регистра, третий, четвертый и пятый выходы блока синхронизации соединены с входами синхронизации соответственно первого, второго и третьего буферных регистров, выход первого буферного регистра соединен с адресным входом первого блока памяти значений арктангенсов.

Кроме того, в устройство дополнительно введен блок сдвига, причем его выходы связаны с регистрами первого и второго аргументов X и Y соответственно, а их входы являются входами аргументов X и Y.

Это является новым техническим решением в технике цифровых вычислительных устройств, поскольку результаты проведенного авторами анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного устройства.

Предложенное устройство для вычисления функций  имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков и связей между ними позволяет повысить точность вычисления функций.

имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков и связей между ними позволяет повысить точность вычисления функций.

Предложенное устройство для вычисления  промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических элементов).

промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических элементов).

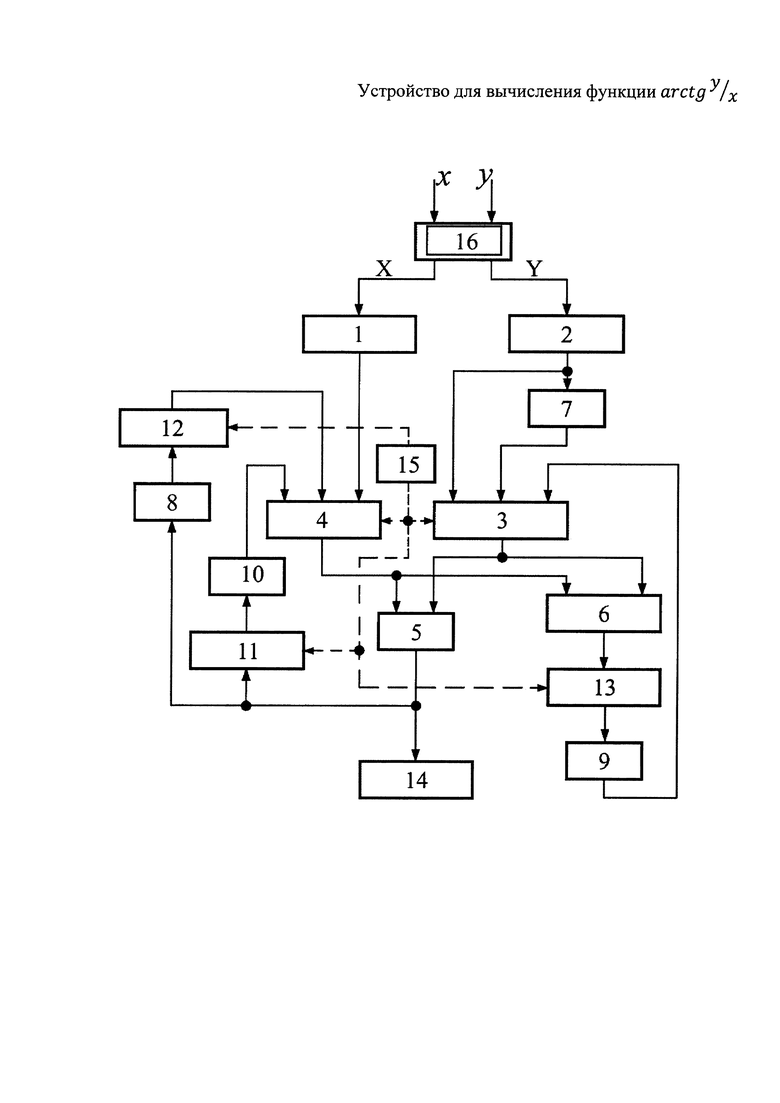

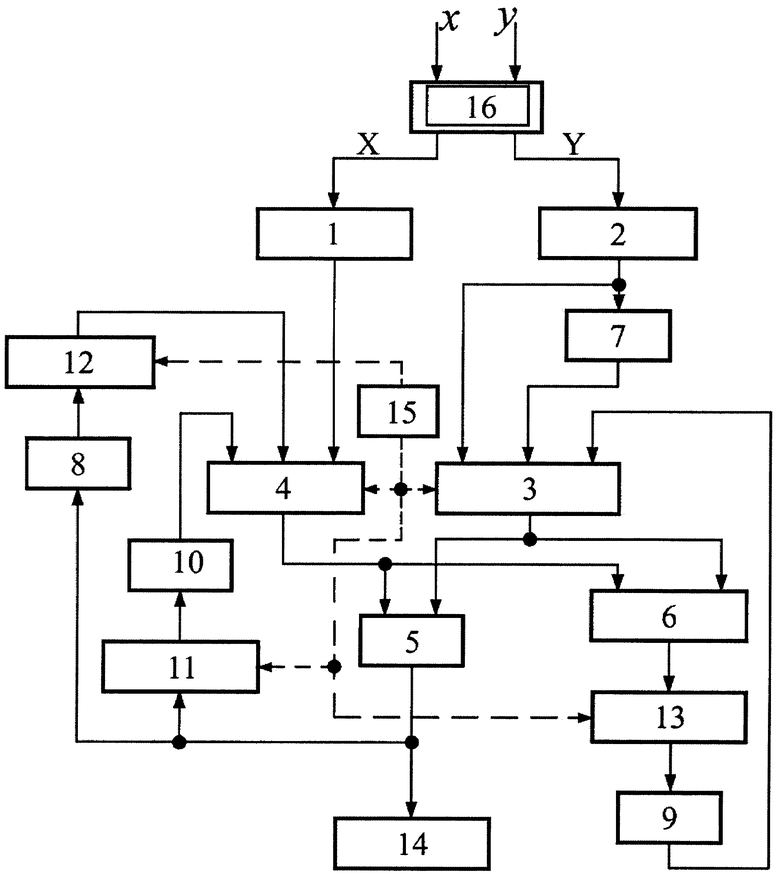

На чертеже представлена схема устройства, которое содержит регистр 1 первого аргумента X, регистр 2 второго аргумента Y, первый и второй коммутаторы 3 и 4, сумматор 5, вычитатель 6, первый, второй, третий и четвертый блоки 7-10 памяти, первый, второй и третий буферные регистры 11-13, регистр 14 результата, блок 15 синхронизации и блок 16 сдвига.

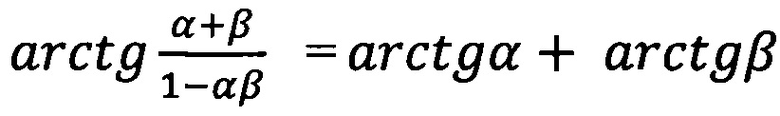

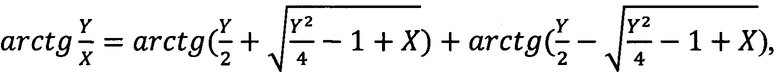

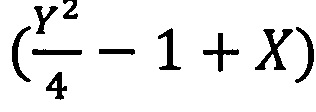

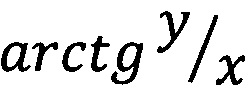

Устройство вычисляет значения функции  путем введения вспомогательных переменных α и β, для которых α+β=y, 1-α⋅β=х, и использования формулы

путем введения вспомогательных переменных α и β, для которых α+β=y, 1-α⋅β=х, и использования формулы  , вытекающей из свойств функции арктангенса. Это дает для вычисления функции

, вытекающей из свойств функции арктангенса. Это дает для вычисления функции  определяющее соотношение

определяющее соотношение

позволяющее на всех этапах промежуточных преобразований вычислять вспомогательные функции от одного аргумента разрядности N, а наличие двух слагаемых учитывать с помощью суммирования на сумматоре и вычитателе.

Регистры 1, 2 первого X и второго Y аргументов получают нормированные значения аргументов х и y от блока 16 сдвига, где происходит сдвиг аргументов х и y влево до появления старшей единицы, наибольшей из входных переменных х и y, в старшем разряде. При этом число сдвигов входных переменных одинаково. Так, например, если х=00001010, y=00100110, то на выходе блока 16 сдвига получим сдвинутые коды переменных X=00101000, Y=10011000. То есть X=х⋅2k, Y=y⋅2k, где k=2.

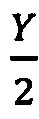

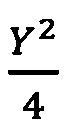

Регистр 1 первого аргумента хранит значение аргумента X, а регистр 2 второго аргумента содержит значение аргумента Y. В первом блоке 7 памяти хранится таблица значений  , во втором блоке 8 памяти - таблица значений квадратного корня, а в третьем и четвертом блоках 9-10 памяти - таблица значений арктангенса.

, во втором блоке 8 памяти - таблица значений квадратного корня, а в третьем и четвертом блоках 9-10 памяти - таблица значений арктангенса.

Устройство работает в три такта, определяемых блоком 15 синхронизации, следующим образом. В первом такте сигналы от блока 15 синхронизации, воздействуя на управляющие входы, подключают к выходу первого коммутатора 3 первый его вход, к выходу второго коммутатора 4 третий его вход, к выходу второго коммутатора 4 третий его вход, а второй буферный регистр 13 фиксирует в этом такте поступающую на его вход информацию. В первом такте значение Y с регистра 2 второго аргумента Y преобразуется в первом блоке 7 памяти, образуя на его выходе значение  , поступающее через первый вход первого коммутатора 3 на первый вход сумматора 5, на второй вход которого поступает через третий вход второго коммутатора 4 с регистра 1 первого аргумента значение X. В результате на выходе сумматора 5 формируется значение

, поступающее через первый вход первого коммутатора 3 на первый вход сумматора 5, на второй вход которого поступает через третий вход второго коммутатора 4 с регистра 1 первого аргумента значение X. В результате на выходе сумматора 5 формируется значение  , запоминаемое во втором буферном регистре 12.

, запоминаемое во втором буферном регистре 12.

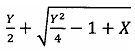

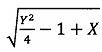

Во втором такте сигналы от блока 15 синхронизации, воздействуя на управляющие входы, подключают к выходу первого коммутатора 3 третий его вход, к выходу второго сумматора 4 - первый его вход, а первый и третий буферные регистры 11 и 13 фиксируют в этом же такте поступающую на его вход информацию. Выход регистра 2 второго аргумента Y подключен к третьему входу первого коммутатора 3 со смещением на один двоичный разряд вправо, чтобы обеспечить формирование на этом входе значения кода  . На первые входы сумматора 5 и вычитателя 6 поступает значение

. На первые входы сумматора 5 и вычитателя 6 поступает значение  , а на вторые их входы с выхода второго блока памяти 8 значение

, а на вторые их входы с выхода второго блока памяти 8 значение  . На выходе сумматора 5 формируется значение

. На выходе сумматора 5 формируется значение  , запоминаемое на первом буферном регистре 11, а на выходе вычитателя 6 - значение

, запоминаемое на первом буферном регистре 11, а на выходе вычитателя 6 - значение  , запоминаемое в третьем буферном регистре 13.

, запоминаемое в третьем буферном регистре 13.

В третьем такте сигналы от блока 15 синхронизации, воздействуя на управляющие входы, подключают к выходу первого и второго коммутаторов 3 и 4 вторые их входы. Третий и четвертый блоки 9-10 памяти выполняют нахождение арктангенса от промежуточных аргументов, а сумматор 5 складывает эти результаты, образуя на своем выходе окончательный результат  , запоминаемый в регистре 14 результата.

, запоминаемый в регистре 14 результата.

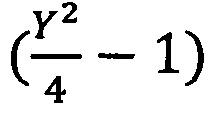

Нормализация значений аргументов х и y, осуществляемая блоком 16 сдвига позволяет увеличить точность вычислений, так как увеличивает количество значащих двоичных разрядов в кодах аргументов. Кроме того, сокращаются погрешности округлений до N двоичных разрядов результатов промежуточных вычислений  и

и  . При этом возведении числа в квадрат отбрасывается N младших разрядов произведения, а при извлечении квадратного корня из N-разрядного числа верными являются только половина

. При этом возведении числа в квадрат отбрасывается N младших разрядов произведения, а при извлечении квадратного корня из N-разрядного числа верными являются только половина  весомозначных разрядов подкоренной величины.

весомозначных разрядов подкоренной величины.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ | 1985 |

|

SU1297041A1 |

| Устройство для вычисления функции арктангенса отношения | 1990 |

|

SU1751750A1 |

| Устройство для выполнения преобразования координат | 1987 |

|

SU1462299A1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Устройство для вычисления функций | 1984 |

|

SU1206767A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для вычисления функций | 1982 |

|

SU1078427A1 |

| Устройство для адаптивного скользящего сглаживания | 1987 |

|

SU1529246A1 |

| Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике | 1989 |

|

SU1667092A1 |

Устройство относится к цифровой вычислительной технике и может быть использовано для ускоренного вычисления функции

Устройство для вычисления функции  , содержащее регистр аргумента X, регистр аргумента Y, блок синхронизации, сумматор, два коммутатора, три буферных регистра, регистр результата, причем выходы первого и второго коммутаторов соединены с входами первого и второго слагаемых сумматора соответственно, выход которого соединен с информационными входами регистра результата, первого буферного регистра, первый и второй выходы блока синхронизации соединены соответственно с управляющими входами первого и второго коммутаторов, вычитатель, блок памяти значений

, содержащее регистр аргумента X, регистр аргумента Y, блок синхронизации, сумматор, два коммутатора, три буферных регистра, регистр результата, причем выходы первого и второго коммутаторов соединены с входами первого и второго слагаемых сумматора соответственно, выход которого соединен с информационными входами регистра результата, первого буферного регистра, первый и второй выходы блока синхронизации соединены соответственно с управляющими входами первого и второго коммутаторов, вычитатель, блок памяти значений  , блок памяти значений квадратного корня, первый и второй блоки памяти значений арктангенса, выходы которых соединены с первыми информационными входами первого и второго коммутаторов соответственно, вторые входы которых соединены с выходами регистра аргумента Y и регистра аргумента X соответственно, третьи информационные входы первого и второго коммутаторов соединены с выходами блока памяти значений

, блок памяти значений квадратного корня, первый и второй блоки памяти значений арктангенса, выходы которых соединены с первыми информационными входами первого и второго коммутаторов соответственно, вторые входы которых соединены с выходами регистра аргумента Y и регистра аргумента X соответственно, третьи информационные входы первого и второго коммутаторов соединены с выходами блока памяти значений  и второго буферного регистра соответственно, адресный вход блока памяти значений

и второго буферного регистра соответственно, адресный вход блока памяти значений  соединен с выходом регистра аргумента Y, выходы первого и второго коммутаторов соединены с входами уменьшаемого и вычитаемого вычитателя соответственно, выход которого соединен с информационным входом третьего буферного регистра, выход которого соединен с адресным входом второго блока памяти значений арктангенса, выход сумматора соединен с адресным входом блока памяти значений квадратного корня, выход которого соединен с адресным входом второго буферного регистра, третий, четвертый и пятый выходы блока синхронизации соединены с входами синхронизации соответственно первого, второго и третьего буферных регистров, выход первого буферного регистра соединен с адресным входом первого блока памяти значений арктангенса, отличающийся тем, что в него дополнительно введен блок сдвига, причем его выходы связаны с регистрами первого и второго аргументов X и Y соответственно, а вход каждого из них является входом аргументов X и Y.

соединен с выходом регистра аргумента Y, выходы первого и второго коммутаторов соединены с входами уменьшаемого и вычитаемого вычитателя соответственно, выход которого соединен с информационным входом третьего буферного регистра, выход которого соединен с адресным входом второго блока памяти значений арктангенса, выход сумматора соединен с адресным входом блока памяти значений квадратного корня, выход которого соединен с адресным входом второго буферного регистра, третий, четвертый и пятый выходы блока синхронизации соединены с входами синхронизации соответственно первого, второго и третьего буферных регистров, выход первого буферного регистра соединен с адресным входом первого блока памяти значений арктангенса, отличающийся тем, что в него дополнительно введен блок сдвига, причем его выходы связаны с регистрами первого и второго аргументов X и Y соответственно, а вход каждого из них является входом аргументов X и Y.

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЗРЫВОМ ПРИ ПРОВЕДЕНИИ СЕЙСМОРАЗВЕДОЧНЫХ РАБОТ | 0 |

|

SU164555A1 |

| УСТРОЙСТВО ДЛЯ ПРИВЕДЕНИЯ ФУНКЦИЙ К МУЛЬТИПЛИКАТИВНОМУ АЛГОРИТМУ ВЫЧИСЛЕНИЙ | 1990 |

|

RU2028659C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ГЕНЕРАТОР СЛУЧАЙНЫХ ПЕРЕСТАНОВОК И СОЧЕТАНИЙ | 2010 |

|

RU2427885C1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

Авторы

Даты

2018-01-24—Публикация

2017-04-06—Подача