Изобретение относится к вычислительной технике и может быть исполь зовано для ускоренного выполнения операций умножения, деления, возве дения в степень и извлечения корня в быстродействующих специализированных и универсальных машинах-. Известно матричное устройство д возведения в квадрат, извлечения квадратного корня и умножения, содержащее две вычислительные матриц группу коммутаторов записи и считы вания сумматоры результата и промежуточных результатов 1J. Недостатком данного устройства является сложность его реализации, так как это устройство использует матричный принцип вычисления. С ро том разрядности операндов объем аппаратурных затрат существенно возрастает. Известно умножительное устройст во, позволяющее выполнять операции умножения и деления и содержащее регистры первого и второго операндо регистр результата, блоки памяти, сумматоры и комГЛутаторы, причем старшей и глладшей частей регистра первого операнда соединены со входом соответственно первого и второго блоков памяти, выходы старшей и младшей частей регистра второго операнда соединены со входами соответственно третьего и четвертого блоков памяти, входы первого сумматора соединены с выходами первого и второго коммутаторов, а выход - со- входом регистра результата входы второго сумматора подключены к выходам третьего и четвертого коммутаторов, выходы первого блока памяти соединены с первыми входами первого и третьего коммутаторов, выход второго блока памяти соединен со вторым входом четвертого коммутатора, выход четвертого блока памя ти соединен со вторым входом четвертого коммутатораi Устройство, кроме того, содержит три блока памя ти, -буферные, регистры, сдвигатели, преобразователи прямого кода в дополнительный многоразрядный ключ и блок -переключения режимов, причем выход первого сумматора соединен со входом пятого блока памяти, выход которого подключен ко входу первого сдвигателя, выход которого соединен с первым входом второго коммутатора выход первого сумматора соединен со входом второго сдвигателя, выход которого подключен ко входу первого буферного регистра, выход младшей части которого соединен со входом шестого блока памяти,- выход которог подключен ко второму входу второго коммутатора, выход второго сумматора соединен со входом второго буфер ного регистра, выход которого соединен со входом седьмого блока памяти, выход которого подключен ко вхоДУ третьего сдвигателя, выход которого подключен ко входу третьего буферного регистра, выход которого соединен со входом первого преобразователя прямого кода в дополнительный, выход которого подключен ко второму входу третьего коммутатора, выход второго сумматора соединен со входом четвертого буферного регистра, выход которого соединен с третьим Входом четвертого коммутатора, выход третьего сдвигателя соединен со входом четвертого буферного регистра, выход пятого блока памяти соединен со входом пятого буферного регистра, выход которого подключен ко второму входу первого коммутатора, выход третьего блока памяти соединен со входом второго преобразователя прямого кода в до- / полнительный выход которого подключен; к третьему входу второго коммутатора, третьему входу третьего коммутатора, и с информационным входом многоразрядного ключа, выход которого соединен с четвертым входом третьего коммутатора, выходы старшей и младшей частей буферного регистра соединены с третьим и четвертым входами первого коммутатора, выход второго буферного регистра соединен с четвертым входом второго коммутатора, управляющие входы преобразователей прямого кода в дополнительный и многоразрядного ключа подключены к выходу блока переключения режимов С 2 . I Недостатком такого устройства является невозможность выполнения операций возведения в степень и извлечения корня.; Цель изобретения - расширение класса задач за счет получения возможности, помимо выполнения операций умножения и деления, выполнения операции возведения в степень и изт влечения корня. Поставленная цель достигается тем, что вычислительное устройство, содержащее регистры первого и второго операндов, три блока памяти, преобразователь прямого кода в дополнительный, сумматор, регистр результата, причем разрядные выходы регистра первого операнда соединены с адресными входами первого блока памяти, разрядные выходы регистра второго операнда соединены с адресными входами второго блока памяти, управляющий вход преобразователя прямого кода в дополнительный соединен с входом задания режима умножения или деления устройства, разрядные выходы сумматора соединены с адресными входами третьего

блока памяти, информационные выходы которого соединены с разрядными входами регистра результата, дополнительно содержит два сдвигателя, группу элементов И, причем вход показателя степени первого операнда устройства соединен с управляющим входом первого сдвигателя, информационные входы которого соединены с информационными входами первого яблока памяти, разрядные выходы первого сдвигателя соединень с входами первого слагаемого сумматора, вход .показателя степени звторого операнда устройства;, соединен с управляющим входом второго сдвигателя, информационные входы которого соединены с информационными выходами второго блока памяти, разрядные выходы вто рого сдвигателя соединены с разрядными входами преобразователя прямого кода в дополнительный, вход управления возведением в степень устройства соединен ; с первыми вход ми элементов И группы, вторые входы которых соединены соответственно с разрядными выходами преобразователя прямого кода в дополнительный, выходы элементов И группы соединены ;соответственно с разрядными входами ;второго слагаемого сумматбра.

.Вычисления в множительном устройстве производяточ на основе соотно;шения ( ,4 иначе можно

- ; - Л J J I

записать

.,,У

(г)

где f + 1, 2 0,1, что эквивалентно выражению (ij при Е f i 1г Откуда следует, что при f 1 производится умножение, а при 5 - 1 деление y2«. в частности,

0

. / 1 е 0

производится, соответственно, умножение (f ; и деление ( -Д) X на, у. При f О и О произво,5дйтся возведение х в степень 2 а при 1 О извлечение из х корня степени .

Сделав подстановку в выражение ч 2) X « у V, получим

0

m Eog- V

или

rn.

25

где m 2. + . 2.

Таким образом, возведение в степень m производится путем подачи на оба

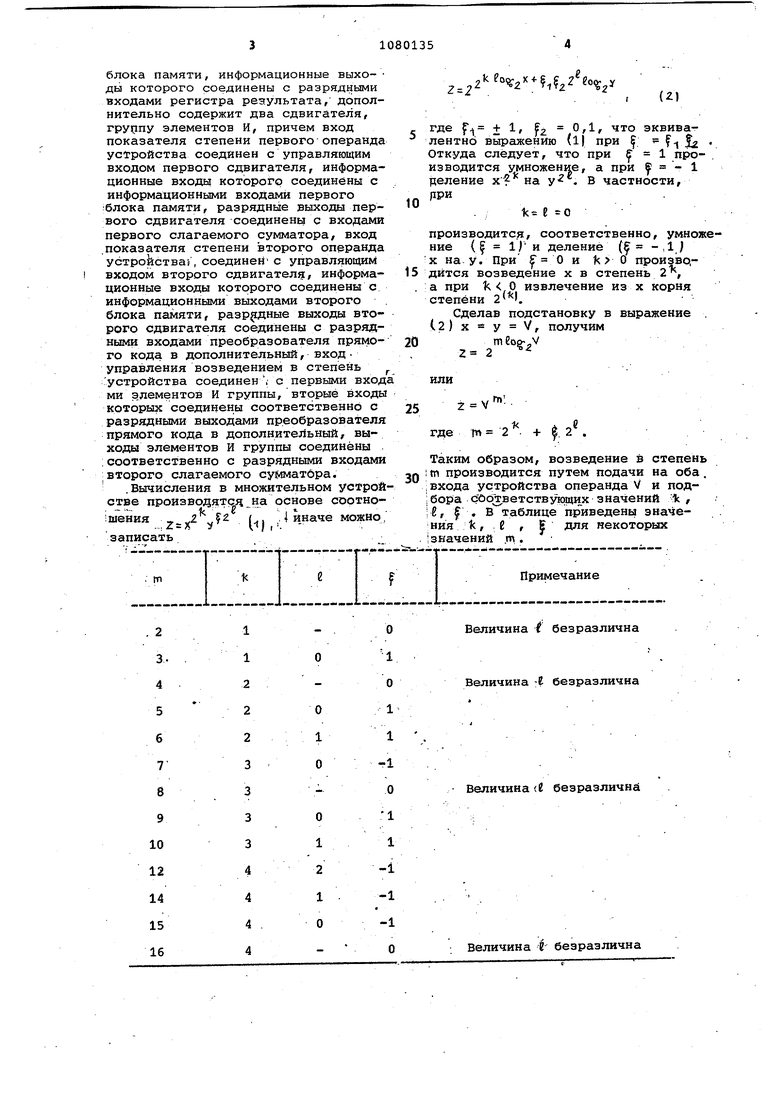

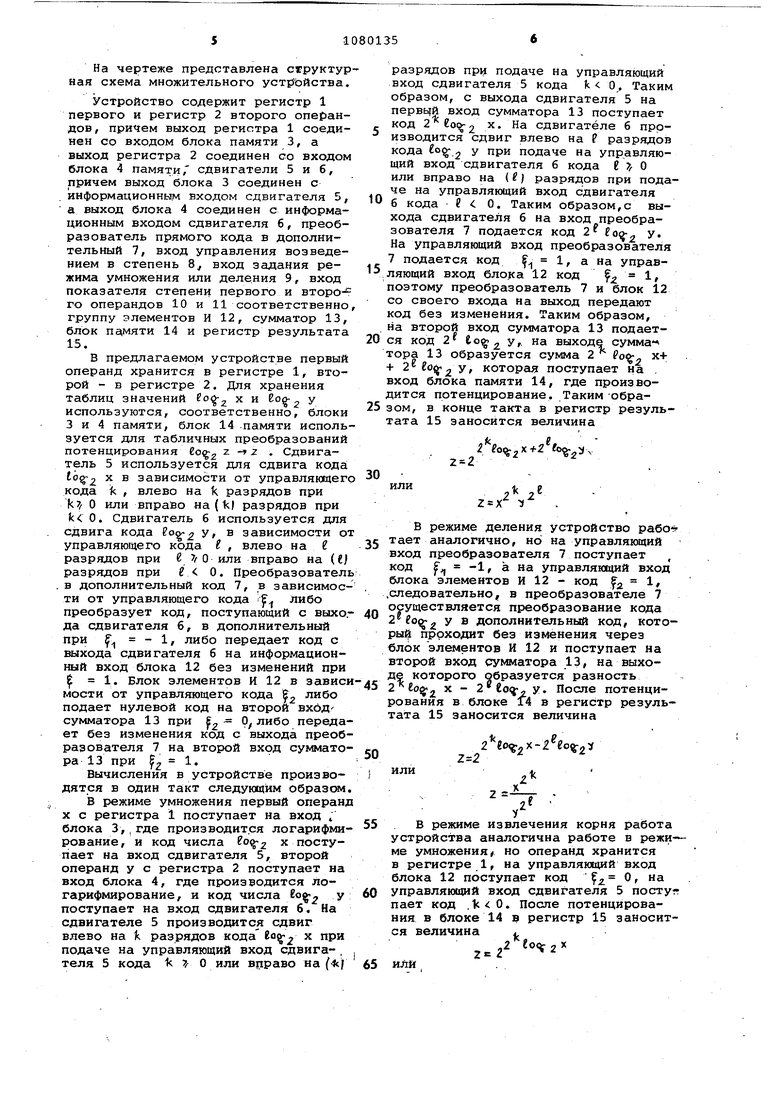

30 входа устройства операнда V и под|бора сОоз ветствующих значений 1с , Л, f , в таблице приведены значения 1( , е , Б для некоторых значений .т . На чертеже представлена структур ная схема множительного устЕ$Ьйства. Устройство содержит регистр 1 первого и регистр 2 второго операндов , причем выход регистра 1 соединен со входом блока памяти 3, а выход регистра 2 соединен со входом блока 4 памяти, сдвигатели 5 и б, причем выход блока 3 соединен с информационным входом сдвигателя 5, а выход блока 4 соединен с информационным входом сдвигателя б, преобразователь прямого кода в дополнительный 7, вход управления возведением в степень 8 вход задания режима умножения или деления 9, вход показателя степени первого и второго операндов 10 и 11 соответственно группу элементов И 12 f сумматор 13, блок памяти 14 и регистр результата 15. В предлагаемом устройстве первый операнд хранится в регистре 1, второй - в регистре 2. Для хранения таблиц значений 2 используются, соответственно, блоки 3 и 4 памяти, блок 14 .памяти используется для табличных преобразований потенцирования Со z - 2 . Сдвигатель 5 используется для сдвига кода . зависимости от управляющего кода k , влево на k разрядов при k7f О ИЛИ вправо на(| разрядов при k 0. Сдвигатель б используется для сдвига кода о зависимости от управляющего кода , влево на разрядов при в 7/0 или вправо на (i) разрядов при 0. Преобразователь . в дополнительный код 7, в зависимоети от управляющего кода - либо преобразует код, поступающий с выхо.да сдвигателя б, в дополнительный при - 1, либо передает код с выхода сдвигателя б на информационный вход блока 12 без изменений при 1. Блок элементов И 12 в зависи мости от управляющего кода 2 либо подает нулевой код на второй вхоД сумматора 13 при 2 Р/ либо передает без изменения код с выхода преобразователя 7 на второй вхрД сумматора 13 при 2 Вычисления в устройстве производятся в один такт следующим образе В режиме умножения первый операнд X с регистра 1 поступает на вход блока 3,,где производится логарифмирование, и код числа X поступает на вход сдвигателя 5, второй операнд у с регистра 2 поступает на вход блока 4, где произ водится логарифмирование, и код числа У поступает на вход сдвигателя б. На сдвигателе 5 производится сдвиг влево на Я разрядов кода во х при подаче на управляющий вход сдвига-, теля 5 кода О или вправо на (4cf разрядов прц подаче на управляющий вход сдвигателя 5 кода k О, Таким образом, с выхода сдвигателя 5 на первцй вход сумматора 13 поступает код 2 Ко(2 - На сдвигателе б производится сдвиг влево на Р разрядов кода оЯГ-2 У Р подаче на управляющий вход сдвигателя б кода 6 / О или вправо на (I} разрядов при подаче на управляющий вход сдвигателя б кода 0. Таким образом,с выхода сдвигателя б на вход преобразователя 7 подается код 2 foo-- у. На управляющий вход преобразователя 7 подается код -, 1, а на управяющий вход блока 12 код 1, поэтому преобразователь 7 и блок 12 со своего входа на выход передают код без изменения. Таким образом, на второй вход сумматора 13 подается код 2 S 2 У выходе сумма- ора 13 образуется сумма 2 о х+ 2 У которая поступает на , вход блока памяти 14, где произвоится потенцирование. Таким образом, в конце такта в регистр резульата 15 заносится величина f/fo v. 2 2 -S В режиме деления устройство рабо тает аналогично, но на управляющий вход преобразователя 7 поступает , код , -1, а на управляющий вход блока элементов И 12 - код f д .следовательно, в преобразователе 7 осуществляется преобразование кода у в дополнительный код, которы проходит без изменения через блок элементов Н 12 я поступает на второй вход сумматора 13, на выходе которого образуется разность , X - 2€о у. После потеь потенцирования в блоке 14 в регистр результата 15 заносится величина В режиме извлечения корня работа устройства аналогична работе в режиме умноженияf но операнд хранится в регистре 1, на управляющий вход блока 12 поступает код О, на управляющий вход сдвигателя 5 поступает код .. После потенцирования в блоке 14 в регистр 15 заносится величина или

г 7х .

в режиме возведения в степень работа устройства аналогична работе в режиме умножения но операнд хранится в обоих регистрах 1 и 2,.величина k , t , f f., f ВЫбирак1.тся из таблицы для требуемого знаЦения показателя степени w. После потенцирования в блоке 14 в регистр 15 заносится величина

m

Таким образом, предлагаемое устройство обладает расширенными функциональными возможностями по сравнению с прототипом.

Введение двух сдвигателей, блока элементов И и соответствующих связей между блоками позволяет осуществить вычисления по формуле (1|, что существенно расширяет функционашьные возможности множительного

I устройства по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для логарифмирования | 1981 |

|

SU962926A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Устройство для вычисления обратной величины | 1989 |

|

SU1711150A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

| Вычислительное устройство | 1990 |

|

SU1742814A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

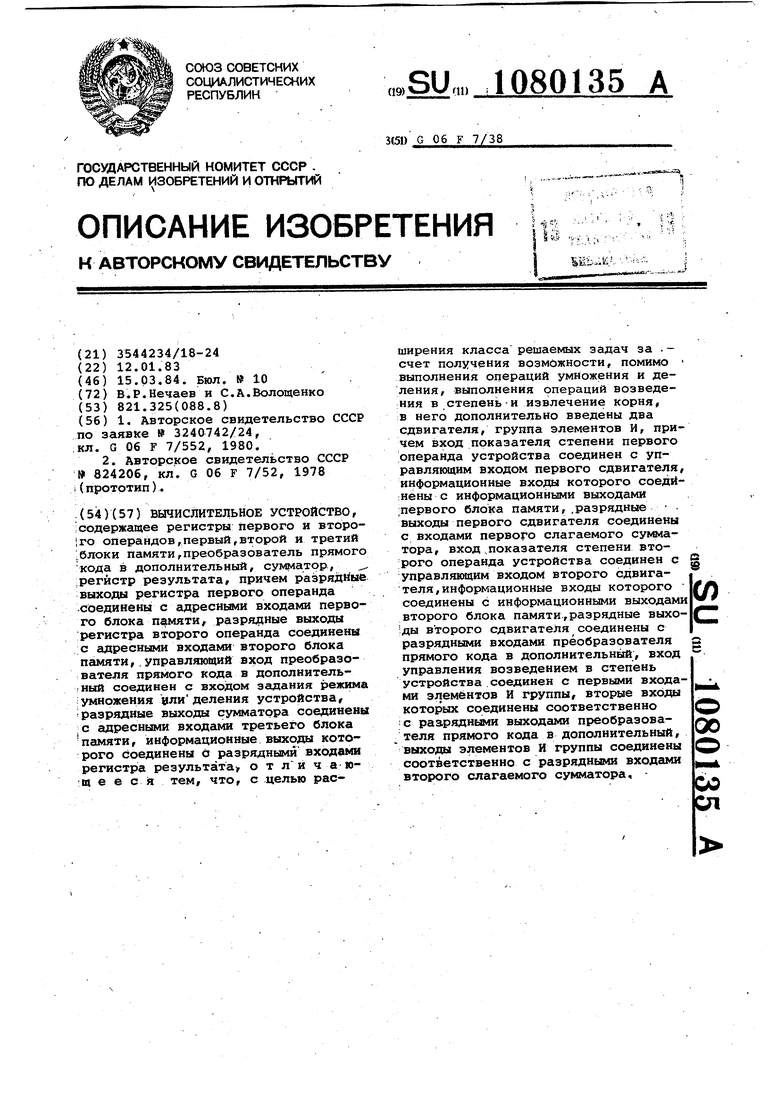

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, ;содержащее регистры первого и второ|го операндов,первый,второй и третий .блоки памяти,преобразователь прямого кода в дополнительный, сумматор, регистр результата, причем разрядные выходы регистра первого операнда .соединены с адресными входами первого блока памяти, разрядные выходы ;регистра второго операнда соединены с адресными входами второго блока памяти,.управляющий вход преобразователя прямого кода в дополнительный соединен с входом задания режима :умножения елиделения устройства, iразрядные выходы сумматора соединены с адресными входами третьего блока памяти, информационные выходы которого соединены о разрядными входами регистра результата о т ч а ющ е е с я тем, что, с целью расширения класса решаемых задач за . счет получения возможности, помимо выполнения операций умножения и деления, выполнения операций возведения в степень-и извлечение корня, в него дополнительно введены два сдвигателя, группа элементов И, причем вход показателя степени первого операнда устройства соединен с управляющим входом первого сдвигателя, информационные входы которого соединены с информационными выходами ;первого блока памяти,.разрядные выходы первого сдвигателя соединены с входами первого слагаемого сукматора, вход ,показателя степени втос рого операнда устройства соединен с управляющим входом второго сдвигателя, информационные входы которого соединены с информационными выходами второго блока памяти,разрядные выхо ды второго сдвигателя соединены с разрядными входами преобразователя 2 прямого кода в дополнительный, вход управления возведением в степень устройства соединен с первыми входами элементов И группы, вторые входы которых соединены соответственно с раарядньаяс выходами преобразова00 теля прямого кода в дополнительный, выходы элементов И группы соединены соответственно с разрядными входами второго слагаемого сумматора, со ел

12

10 11

О-1

J V

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке 3240742/24, ;кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1984-03-15—Публикация

1983-01-12—Подача