1 1

Изобретение относится к вычислительной технике и может быть использовано при создании микропроцессорных систем с больш:им объемом памяти.

Известно устройство, содержащее куб памяти- (объем памяти, ограниченный разрядностью адресной шины микропроцессора, т.е. для КР580ИК80А 64 Кбайт) и магистраль микро-ЭВМ,шины адреса и данных которой, а также сигналы Запись, Чтение и Вьщача шины управления соединены с cooтвeтcтвyюшJiми входами куба памяти D3Основным недостатком устройства является ограниченньй объем адресуемой памяти.

Известно устройств), содержащее дешифратор адреса и регистр,причем вход дешифратора адреса подключен к адресному входу устройства,выход дешифратора адреса подключен к входу выборки регистра, информационньй вход которого подключен к информационному входу устройства, управляющий вход регистра подключен к входу записи ввода-вьгоода устройства 2j .

Недостатком известного устройства является невозможность использования стандартных команд CALL или JM3 для перехода к адресам, расположенным в кубах памяти, отличных от нулевого, и стандартной команды RETURN для возврата в нулевой куб.

Цель изобретения - расширение области применения за счет увеличения объема ад,ресуемой памяти при ограниченном количестве адресных разрядов.

Поставленная цель достигается тем, что в устройство для адресации памяти, содержащее дешифратор адре- ; са и первьй регистр, причем вход дешифратора адреса подключен к адресному входу устройства, выход дешифратора адреса подключен к входу выборки первого регистра, информационный вход которого подключен к информационному входу устройства, синхровход первого регистра подключен к входу записи ввода-вывода устройства,, введены второй регистр, дешифратор команд, элемент ИЛИ, два элемента И, элемент задержки, триггер и коммутатор,причем выход

604092

первого регистра подключен к информационному входу второго регистра, входы сброса и записи которого подключены соответственно 5 к входу сброса устройства и выходу первого элемента И, выход второго регистра подключен к адресному входу коммутатора, информационный .вход которого подключен к входу заO Дания режима работы устройства, « -йвыход ко1Ф1утатора подключен к i -му выходу задания режима работы устройства (, N, где N - количество адресуемых блоков памяти), вход

5 дешифратора команд подключен к входу кода операции устройства, выходы дешифратора команд подключены к входам элемента ИЛИ, выход которого подключен к первому входу второго элемента И, второй вход которого подключен к входу йачала цикла устройства, выход второго элемента И подключен к синхровходу триггера, выход которого через элемент

5 задержки подключен к первому входу . первого элемента И, второй вход которого подключен к входу начала цикла устройства, выход первого элемента И подкл}очен к входу устаногки в о триггера.

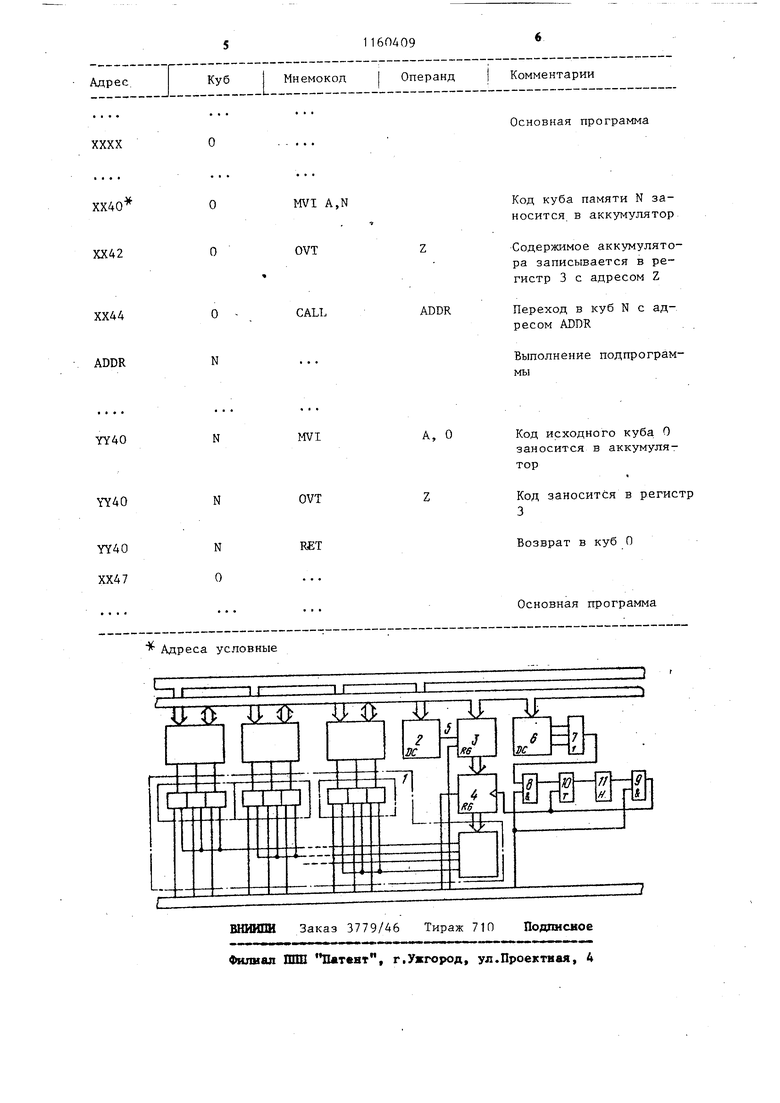

На чертеже представлена схема устройства для адресации памяти.

Устройство содержит коммутатор 1, дешифратор 2 адреса, регистры 3 и 4, выход 5 дешифратора адреса, дешифратор 6 команд, элемент ИЛИ 7, элементы И 8 и 9, триггер 10 и элемент 11 задержки.

Устройство работает следуюпртм образом.

Предположим, что 1 -и выход коммутатора 1 подключен к входу управления i -го куба памяти, адресный вход которого подключен к входу адреса устройства.

При включении питания микро-ЭВМ (или при начальной установке в процессе работы) S задающем генераторе микро-ЭВМ вырабатьтается сигнал Сброс, устанавливающий адресньй вход в нулевое состояние и сбрасываюш й в нулевое состояние регистр 4, нулевой код с выхода которого поступает на вход коммутатора 1 и приводит к коммутации сигналов управления на вход нулевого куба памяти.

3

Переход из куба в куб мохсет осуществляться по командам: JMP ADDR - безусловньй переход на адрес ADDR, CALL ADDR - переход на подпрограмму с адреса ADDR, RET возврат из подпрограммы.

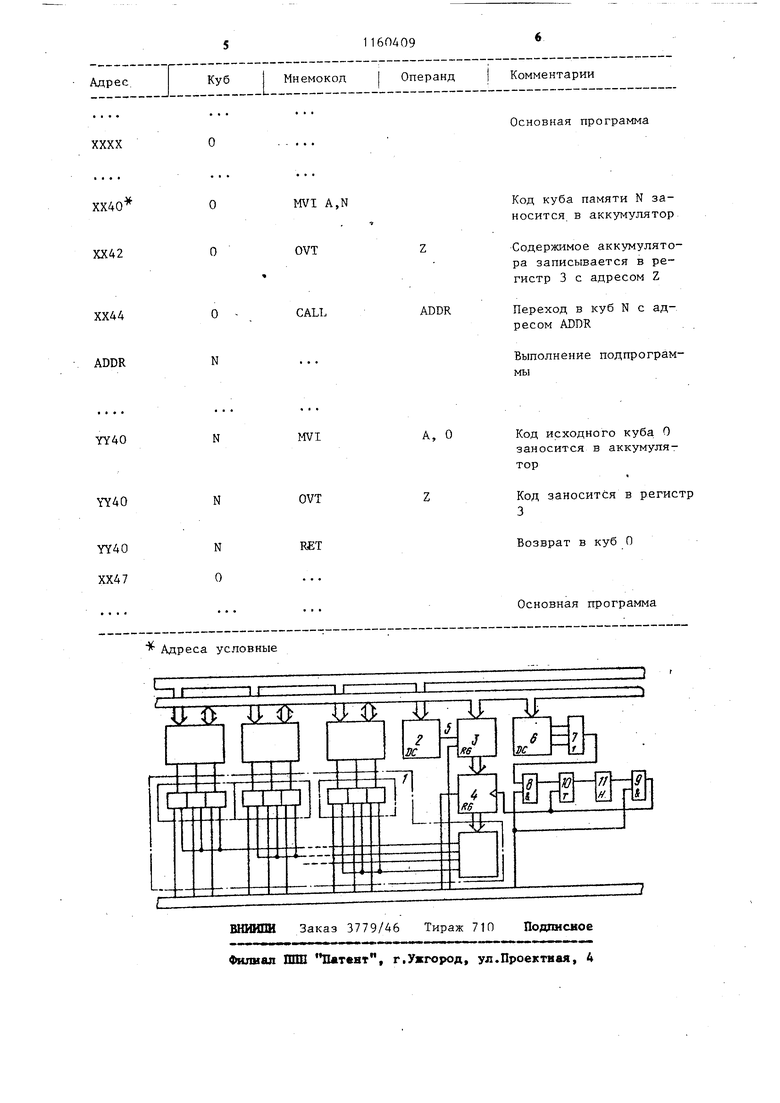

В таблице приведен фрагмент программы перехода из куба О в куб N и обратно.

Для перехода из куба О в куб N необходимо в основной программе записать в аккумулятор микропроцессора код N и по команде OVT записать содержимое аккумулятора в регистр 3 с адресом Z.

По адресу программы ХХ40 записывается в аккумулятор код куба памяти N (команда fVI), к которому необходимо произвести переход. По следующему адресу ХХ42 записана команда OUT Z, при этом в первом машинном цикле микропроцессор читае команду, во втором - адрес, а в третьем вьщает на адресный вход уст ройства адрес Z, на информационный вход код N, а на вход записи ввода-вывода сигнал Запись В/В, при этом дешифратор 2 адреса вьщает на выходе 5 логическую 1, подаваемзто на управляющий вход регистра 3, который по приходу сигнала записи ЗАПИСЬ В/В записывает код N с информационного входа, т.е. на его выходе появлйется код N.

При вьтолнении следующей команды CALL ADBR в первом машинном цикле микропроцессор считывает с информационного входа код команды CALL, этот же код дешифрируется дешифратором 6 команд, который вьщает логическую l на одном из входов,через элемент ИЛИ 7 поступаюй по на первьй вход первого элемента И 8, стробируя сигнал первого цикла команды. Дешифратор команд вьдает логическую 1 на первом выходе в случае появления на его входе кодов команд перехода (JMP) , на втоП409 , 4

ром - ,(CALL), на третьем - 09ie

(RET). Элемент И 3 необходим для того, чтобы отличить коды команд перехода от данных, могущих иметь 5 тот же код (команды сопровождаются сигналом Ml) . Положительны импульг на выходе первого элемента И 8 по заднему фронту устанавливает триггер 10 в единичное состояние, положительный перепад через время,

обусловленное элементом 11 задержки, появляется на первом входе второго элемента И 9. Время задержки элемента 11 подобрано так, что не i.pof5 исходит совпадения положительных уровней на выходе элемента 11 задержки и сигнала Ml команды, во время которой произошло переключение (в нашем случае команды CALL).

20 Далее микропроцессор выполняет действия, предписанные командой CALL.

При приходе любой следующей команды сигнал первого машинного цикла Ml проходит через элемент И

25 9 и по переднему фронту импульса на выходе элемента И 9 происходит запись кода N с выхода регистра 3 в регистр 4, а также сброс триггера 10. В это же время код N поступает на вход коммутатора 1 и, следовательно, сигналы управления памятью подключаются к кубу памяти N.

Процесс возврата в исходный

5 куб памяти происходит аналогично. По адресу УУ40 (условно) записывается код первоначального куба памяти О в аккумулятор, по адресу УУ42 это значение .записывается в регистр

0 ; 3, и по команде RET происходит воэi врат в куб О памяти по команде, записанной по адресу ХХ47, после чего микропроцессор вьтолняет основную исходную программу.

5 Таким образсм, имея в регистрах 9 по восемь разрядов, можно обеспечить расширение адресного пространства до 256 кубов памяти, т.е. 16 Мбайт.

51160А09

I

Куб j Мнемокод I Операнд

Адрес,

о

хххх

Комментарии

Основная программа

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации памяти | 1987 |

|

SU1481760A1 |

| Устройство адресации памяти | 1984 |

|

SU1238072A2 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для адресации памяти | 1987 |

|

SU1442990A1 |

| Микропроцессор | 1985 |

|

SU1290340A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для контроля последовательности выполнения программ | 1987 |

|

SU1536389A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ, содержащее дешифратор адреса и первый регистр, причем вход дешифратора адреса подключен к адресному входу устройства, выход дешифратора адреса подключен к входу выборки первого регистра, информационньпЧ вход которого подключен к информационному входу устройства, синхровход первого регистра подключен к входу записи ввода-вывода устройства, отличающееся тем, что, с целью расширения области применения за счет увеличения объема адресуемой памяти при ограниченном количестве адресных разрядов, оно содержит второй регистр, дешифратор команд, элемент ИЛИ, два элемента И, элемент задержки, триггер и коммутатор, причем выход первого регистра подключен к информационному входу второго регистра, входы сброса и записи которого подключены соответственно к входу сброса устройства и выходу первого элемента И, выход второго регистра подключен к адресному входу коммутатора, информационный вход которого подключен к входу задания режима работы устройства, /f -и выход коммутатора подключен к 1-му выходу з адания режима работы устройства ( 1, N где ц - коли(Л чество адресуемых блоков памяти), вход дешифратора команд подключен к входу кода операции устройства, выходы дешифратора команд подключены к входам элемента ИЛИ, выход которого подключен к первому входу второго элемента И, второй вход которого подключен к входу начала цикла устройства, выход второго эле05 мьнта И подключен к синхровходу . о триггера, выход которого через элемент задержки подключен к первому входу первого элемента И, второй - вход которого подключен к входу на чала цикла устройства, выход первого элемента И подключен к входу установки О триггера.

ХХ40

MVI A,N

ХХ42

OVT

ХХ44

О

CALT.

ADDR

N

MVI

N

OVT

N О

Адреса условные

Ьх

-LL

J-L

л о. . о. .1 о.

Код куба памяти N заносится в аккумулятор

Содержимое аккумулятора записывается в регистр 3 с адресом Z

DDR

Переход в куб N с адресом ADDR

Выполнение подпрограммы

О

Код исходного куба О заносится в аккумулятор

Код заносится в регистр 3

Возврат в куб О

Основная программа

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Контроллер программируемый универсальный | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Насос | 1917 |

|

SU13A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Григорьев В.Л | |||

| Программное обеспечение микропроцессорных систем | |||

| М., Энергоатомиздат,1983лс | |||

| , | |||

Авторы

Даты

1985-06-07—Публикация

1984-01-11—Подача