Bmi Ш-орки

Шина yfifgoMHu

С/)

4 4; to

ее. со

Bxoi некем aielВходночам цикла устрайстоа

1

мент ИЛИ 8, формирователь импульсов 9, два регистра 10, 11, элемент задержки 12, триггер 13 И коммутатор 14. Новым в устройстве являются третий элемент И, регистр ресурсов, сдвиговый регистр и формирователь импульсов с их функциональными связями. Устройство позволяет при выполнеНИИ команды микропроцессорной системы переходить из куба в куб памяти по любой команде, не требуя наличия

программ доступа к данным в каждом кубе памяти. Устройство позволяет также маскировать кубы памяти, в которых хранятся команды или данные, которые подлежат защите, при этом запись информации в замаскированные кубы памяти запрещена. Таким образом, упрощение доступа к данным и командам, защита кубов памяти приводят к повышению надежности функционирования устройства. I ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации памяти | 1984 |

|

SU1160409A1 |

| Устройство для адресации памяти | 1987 |

|

SU1481760A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Устройство адресации памяти | 1984 |

|

SU1238072A2 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Устройство для захвата магистрали ЭВМ | 1982 |

|

SU1075247A1 |

| Устройство для ввода информации | 1991 |

|

SU1800452A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для ввода данных | 1986 |

|

SU1348810A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

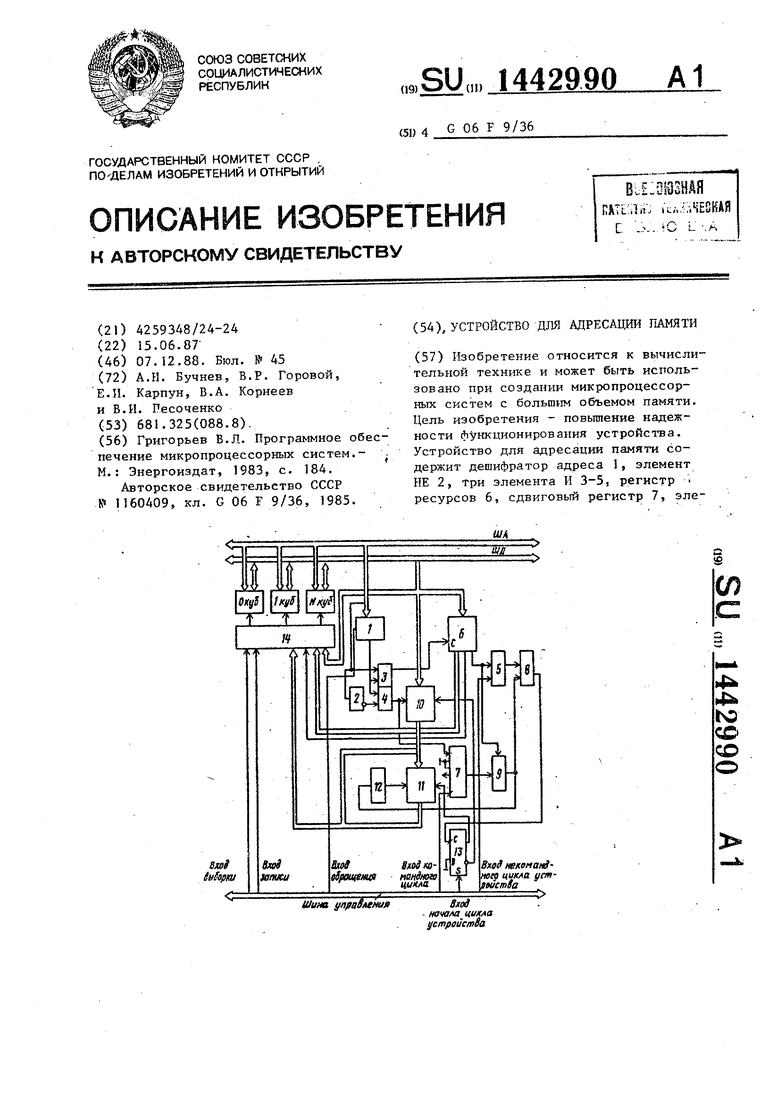

Изобретение относится к вычислительной технике и может быть использовано при создании микропроцессорных систем с большим объемом памяти. Цель изобретения - повышение надежности функционирования устройства. Устройство для адресации памяти содержит дешифратор адреса 1, элемент НЕ 2, три элемента И 3-5, регистр ресурсов 6, сдвиговый регистр 7, эле

1

Изобретение относится к вычислительной технике и может быть использовано при создании микропроцессорных систем с большим объемом памяти.

Цель изобретения - повышение надежности функционирования устройства

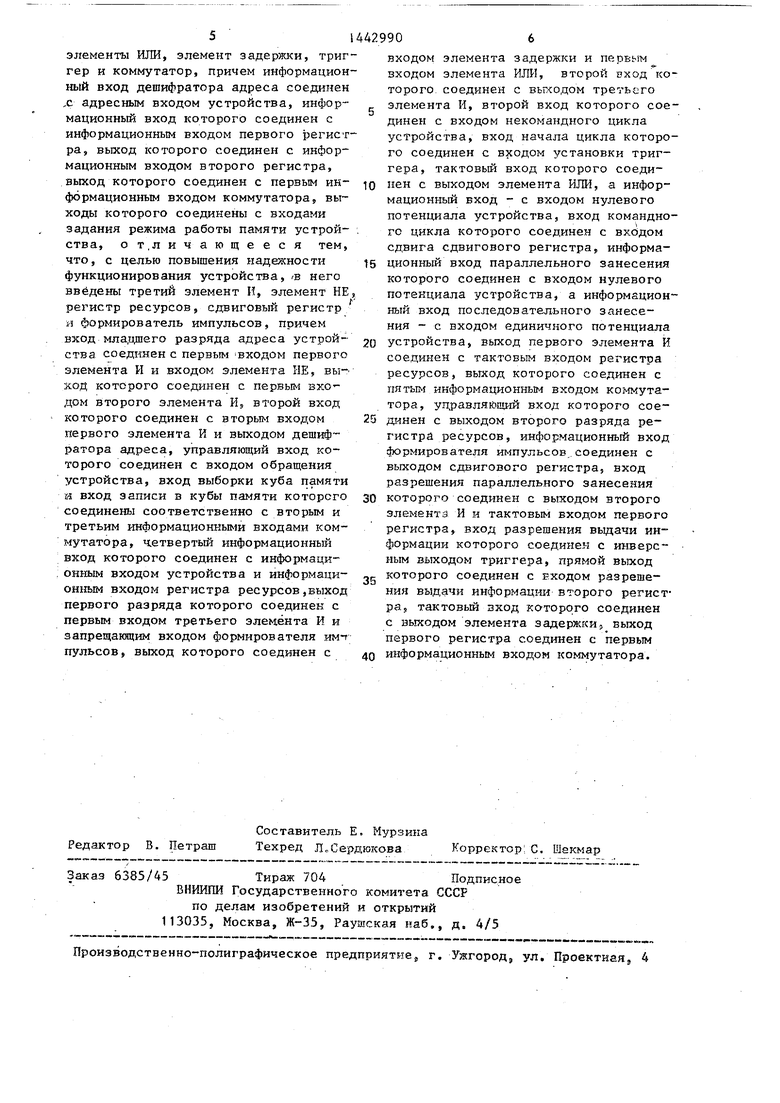

На чертеже приведена функциональная схема устройства.

Устройство для адресации памяти содержит дешифратор I адреса, элемен НЕ 2, первый 3, второй 4 и третий 5 элементы И, регистр 6 ресурсов, сдвиговый регистр 7, элемент ИЛИ 8, формирователь 9 импульсов, первый 10 и второй 11 регистры, элемент 12 за- держки, триггер 13, коммутатор 14.

Устройство работает следующем образом.

Предположим, что i-й выход коммутатора 14 подключен к входу управле- НИН i-ro куба памяти, а(ресный вход которого подключен к входу адреса устройства. При начальной установке в процессе работы в задающем генераторе микроэвм вырабатывается сигнал Сброс, устанавливающий адресный вход в нулевое состояние и сбрасывающий в нулевое состояние регистры 10 и 11 (не показано), нулевой код с выходов которых поступает на пер- вый информационный вход коммутатора 14 и приводит к коммутации сигналов управления на вход нулевого куба памйти. Состояние триггера 13 в на- чальньй момент устанавливается произ вольно и определяет, какой из регистров, 10 или 11, выдает информацию.

; Переход из куба в куб может осуществляться, как по командам IMPADDR CAbLADDR, RET, так и по любой другой команде. Запись в регистр ресурсов производится по командам Ш1, OUT. При выполнении команды OUT дешифратор 1 выдает на выходе логическую I, которая проходит через первый элемент И 3 и поступает на тактовый вход регистра 6 ресурсов, последний заносит в себя код М. Устройство работает в двух режимах.

Младший разряд регистра 6 ресурсов управляет режимами работы устройства. Первый режим работы устройства устанавливается, если в младшем разряде регистра 6 ресурсов записан логический о, при этом работа формирователя 9 импульсов разрешается, а работа элемента И 5 блокируется. Для перехода из куба О в куб 1(0 ) необходимо в основной программе записать в аккумулятор микропроцессора код i и по команде OUT записать содержимое аккумулятора в регистр 10 с адресом Z.

При выполнении команды OUT Z в первом машинном микропроцессор читает команду, во втором - адрес, а в третьем выдает на адресный вход устройства адрес Z, на информационный вход - код i, а на вход обращени устройства - сигнал, который разре- шает работу дешифратора. При этом дешифратор выдает на выходе логическую 1, которая через элемент И 4, на второй вход которого с выхода..

инвертора подается логическая , поступает на тактовый вход регистра 0, последний записывает код i с информационного входа. Логическая с выхода элемента И 4 также обнуляет сдвиговый регистр 7.

При выполнении следующей команды (все команды сопровождаются сигналом

кода куба памяти, содержащего дан1а.1е5 в регистр 10, аналогично первому режиму работы.

Далее выполняется основная программа. При этом, если происходит цикл чтения команды, код на первый информационный вход коммутатора 14 выдает регистр 1 I, если происзсодит

Ml, который поступает на вход команд- ю любой другой цикл, то сигнал Ml, коного цикла устройства), которая может быть как ко мандой,, С ALL, IMP так и любой другой командой, сдвиговый регистр 7 заносит логическую 1 в первый разряд, дал1е микропроцессор выполняет команду, при приходе любой следующей команды на втором выходе сдвигового регистра 7 появляется логическая 1. При появлении, фор- мирователь 9 импульсов вырабатывает на выходе импульс, который сбрасывает триггер 13 и поступает на вход элемента задержки. Так как триггер 13 сброшен, информацию начинает выдавать регистр 10, а выход регистра П переходит в третье состояние.

По завершении этих операций импульсный сигнал, задержанный элементом 12 задержки, поступает на тактовый вход регистра 11, по которому в него записывается код, содержащийся в регистре 10. В начале следунщего обмена микропроцессора триггер 13 устанавливается сигналом синхронизации

торый сопровождает любой цикл микропроцессора, кроме командного, посту- пает на вход некомандного цикла уст- ройствау проходит через элементен, 5, 15 элемент ИЛИ 8 и сбрасьшает триггер 13, что вызывает переключение на выдачу кода на первый информационный вход коммутатора 14 регистра 10. В начале следующего цикла обмана триг- 20 гер 13 снова устанавливается.

Конфликтных ситуаций при сбросе и установке 13 не бывает, так как сигнал HI поступает позже, чем сигнал синхронизации обмена. 25 Коммутатор 14 работает следукчцим образом.

Если во втором разряде регистра 6 ресурсов устройства, поступающем на управляющий вход коммутатора 14, 30 записана 1, начинается выполнение программы установки масок. Эта программа записана в 0-м кубе памяти. При этом блокируется запись и чтение всех кубов памяти, кроме .нулевого, а

Если во втором разряде регистра 6 ресурсов устройства, поступающем на управляющий вход коммутатора 14, 30 записана 1, начинается выполнение программы установки масок. Эта программа записана в 0-м кубе памяти. При этом блокируется запись и чтение всех кубов памяти, кроме .нулевого, а

обмена, который поступает на вход на- -g коммутатор 14 по сигналу записи, почала цикла устройства, при этом выходы регистра 10 переходят в третье состояние, а регистр 11 начинает выдавать код на первый информационный вход коммутатора.

Процесс возврата в исходный или любой другой куб памяти происходит аналогично после выполнения команды OUT Z микропроцессором. Устройство ждет, когда выполнится следующая команда за OUT Z, а затем переключает регистры 10 и 11 так, что на пер- вьй информационный вход коммутатора поступает код куба памяти, в который происходит возврат или переход.

Второй режим работы устройства устанавливается, если в младщий разряд регистра ресурсов записана логическая 1, при этом работа формирователя 9 импульсов блокируется, а рэ eg бота.элемента И 5 разрешается. Б регистре 11 записан код куба памяти, содержащий команда. Далее микропроцессор выполняет процедуру записи

ступающему на его третий информационный вход, производит запись инфорч мации в регистр маски, код которого поступает на его пятый информацион40 ный вход с регистра 6 ресурсов (стар шие 5 разрядов). После записи масок для всех кубов памяти микропроцессор записывает во второй разряд регистра ресурсов логический О, при этом

45 коммутатор 14 пропускает коды адреса кубов памяти, поступающие с регистро 11 и 10 на его первый информацио1шый вход, и сигналы выборки куба памяти и записи в кубы памяти, поступающие соответственно на его второй и трети информационные входы. Из замаскироп ; ванного куба памяти возможно только чтение информации.

Формула изобретения

Устройство для адресации памяти, содержащее дешифратор адреса, первый и второй регистр, первый и второй

50

кода куба памяти, содержащего дан1а.1е5 в регистр 10, аналогично первому режиму работы.

Далее выполняется основная программа. При этом, если происходит цикл чтения команды, код на первый информационный вход коммутатора 14 выдает регистр 1 I, если происзсодит

торый сопровождает любой цикл микропроцессора, кроме командного, посту- пает на вход некомандного цикла уст- ройствау проходит через элементен, 5, 5 элемент ИЛИ 8 и сбрасьшает триггер 13, что вызывает переключение на выдачу кода на первый информационный вход коммутатора 14 регистра 10. В начале следующего цикла обмана триг- 0 гер 13 снова устанавливается.

Конфликтных ситуаций при сбросе и установке 13 не бывает, так как сигнал HI поступает позже, чем сигнал синхронизации обмена. 5 Коммутатор 14 работает следукчцим образом.

Если во втором разряде регистра 6 ресурсов устройства, поступающем на управляющий вход коммутатора 14, 0 записана 1, начинается выполнение программы установки масок. Эта программа записана в 0-м кубе памяти. При этом блокируется запись и чтение всех кубов памяти, кроме .нулевого, а

g коммутатор 14 по сигналу записи, по

ступающему на его третий информационный вход, производит запись инфорч мации в регистр маски, код которого поступает на его пятый информационный вход с регистра 6 ресурсов (старшие 5 разрядов). После записи масок для всех кубов памяти микропроцессор записывает во второй разряд регистра ресурсов логический О, при этом

коммутатор 14 пропускает коды адреса кубов памяти, поступающие с регистров 11 и 10 на его первый информацио1шый вход, и сигналы выборки куба памяти и записи в кубы памяти, поступающие соответственно на его второй и третий информационные входы. Из замаскироп ; ванного куба памяти возможно только чтение информации.

Формула изобретения

Устройство для адресации памяти, содержащее дешифратор адреса, первый и второй регистр, первый и второй

элементы ИЛИ, элемент задержки, триггер и коммутатор, причем информационный вход дешифратора адреса соединен с адресным входом устройства, информационный вход которого соединен с информационным входом первого регистра, выход которого соединен с информационным входом второго регистра, выход которого соединен с первым информационным входом коммутатора, выходы которого соединены с входами задания режима работы памяти устрой- . ства, от.личающееся тем, что, с целью повышения надежности функционирования устройства, В него введены третий элемент И, элемент НЕ, регистр ресурсов, сдвиговый регистр и формирователь импульсов, причем вход мла.цшего разряда адреса устройства соединен с первым -входом первого элемента И и входом элемента ЫЕ, вы- код которого соединен с первым входом второго элемента MS второй вход которого соединен с вторым входом первого элемента И и выходом дешифратора адреса, управляющий вход которого соединен с входом обращения устройства, вход выборки куба памяти м вход записи в кубы памяти которого соединены соответственно с вторым и третьим информационными входами коммутатора, четвертый информационный вход которого соединен с информаци- онным входом устройства и информационным входом регистра ресурсов,выход первого разряда которого соединен с первым входом третьего элемента И и запрещающим входом формирователя имт пульсов, выход которого соединен с

входом элемента задержки и nepEbiM входом элемента ИЛИ, второй вход которого, соединен с выходом третьего

элемента И, второй вход которого сое-

динен с входом некомандного цикла

устройства, вход начала цикла которого соединен с входом установки триггера, тактовый вход которого соедипен с выходом элемента ИЛИ, а информационный вход - с входом нулевого потенциала устройства, вход командного цикла которого соединен с входом сдвига сдвигового регистра, информационный вход параллельного занесения которого соединен с входом нулевого потенциала устройства, а информационный вход последовательного занесения - с входом единичного потенциала

устройства, выход первого элемента И соединен с тактовым входом регистра ресурсов, выход которого соединен с пятым информационньм входом коммутатора, управляющий вход которого соединен с выходом второго разряда регистра ресурсов, информационный вход формирователя импульсов соединен с выходом сдвигового регистра, вход разрешения параллельного занесения

которого соединен с выходом второго элемента И и тактовым входом первого регистра, вход разрешения вьщачи информации которого соединен с инверсным выходом триггера, прямой выход которого соединен с входом разрешения выдачи информации второго регистра, тактовый вход которО|го соединен с выходом элемента задержки, выход первого регистра соединен с первым

информационным входом коммутатора.

| Григорьев В.Л | |||

| Программное обеспечение микропроцессорных систем.- М | |||

| : Энергоиздат, 1983, с | |||

| Переносная печь-плита | 1920 |

|

SU184A1 |

| Устройство для адресации памяти | 1984 |

|

SU1160409A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-07—Публикация

1987-06-15—Подача