(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации памяти | 1984 |

|

SU1160409A1 |

| Устройство адресации памяти | 1984 |

|

SU1238072A2 |

| Устройство для адресации памяти | 1987 |

|

SU1442990A1 |

| Устройство для приоритетного прерывания | 1985 |

|

SU1287159A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство для ввода информации | 1991 |

|

SU1800452A1 |

| Микропроцессорное устройство для моделирования систем массового обслуживания | 1984 |

|

SU1196886A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании микропроцессорных систем с большим объемом памяти. Цель изобретения - расширение области применения за счет увеличения объема адресуемой памяти при ограниченном количестве адресных разрядов. Поставленная цель достигается тем, что устройство содержит первый дешифратор 1, сдвигающий регистр 2, к регистров 3, где K - число членов разложения значения N, а N - число кубов памяти, обслуживаемых устройством, второй дешифратор 4, первый 5 и второй 6 элементы И, элемент 7 задержки, триггер 8 и блок 9 коммутации. 1 з.п.ф-лы, 1 ил.

Јъ

оо

о

Изобретение относится к вычислительной технике и может быть использовано при создании микропроцессорных систем с большим объемом памяти.

Цель изобретения - расширение области применения за счет увеличения объема адресуемой памяти при ограниченном количестве адресных разрядов.

На чертеже приведена схема устройства.

Устройство для адресации памяти содержит первый дешифратор 1, сдвигающий регистр 2, К регистров 3, второй дешифратор 4, первый и второй элементы И 5 и 6, элемент 7 задержки, триггер 8, блок 9 коммутации, элемент ИЛИ 10. Блок 9 коммутации содержит коммутатор и К групп коммутаторов 12.

Устройство работает следующим образом.

При включении питания микро-ЭВМ (или при начальной установке в процессе работы) в задающем генераторе микро-ЭВМ вырабатывается сигнал «Сброс, устанавливающий адресный вход в нулевое состояние и сбрасывающий в нулевое состояние регистр 2 и регистры 3, нулевые коды с выходов которых поступают на управляющие входы блока 9 коммутации и приводят к коммутации сигналов управления на вход нулевого куба памяти.

Переход из куба в куб может осуществляться, например, по командам: JMP /ШЈ #-безусловный переход на адрес ADDR, CALL ADDR. переход на подпрограмму с адреса ADDR, RET возврат из подпрограммы.

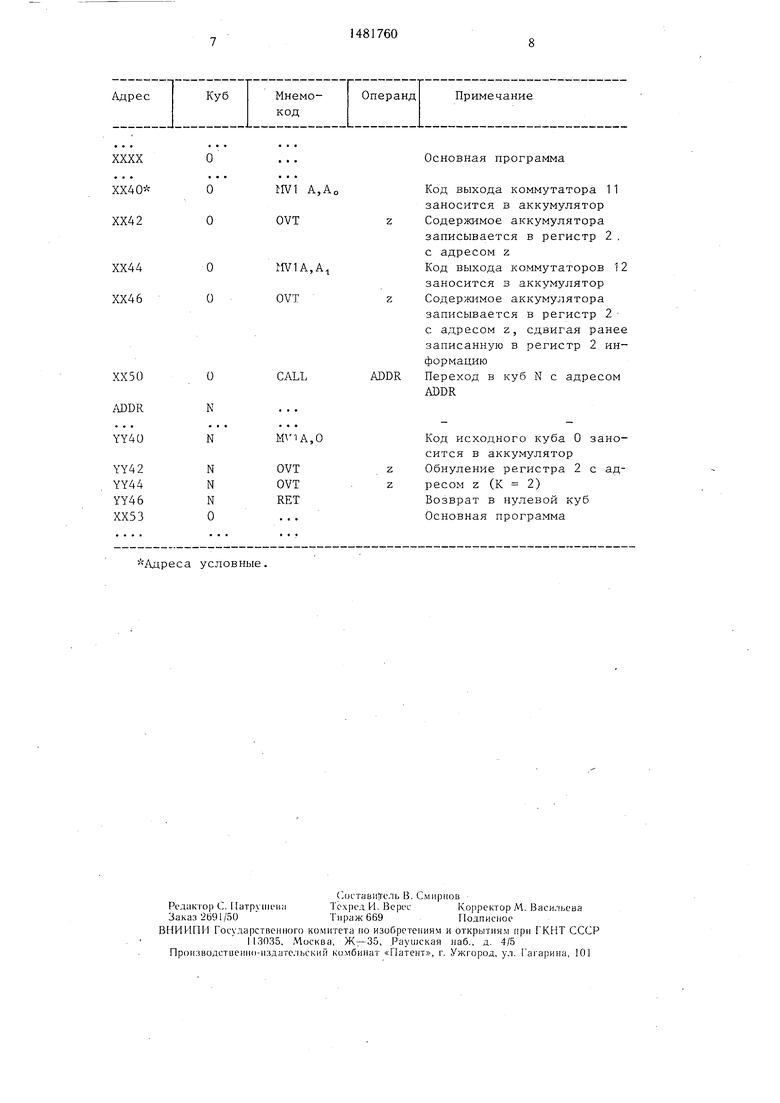

В таблице приведен фрагмент программы перехода из куба О в куб N и обратно.

Для выборки yV-ro куба памяти необходимо разложить число /V в конечную сумму

ряда А, -2м , причем Л, любого ,1...,(К-1). Полученные коэффициенты А,, где ,1,...,(К-1), определяют номера выбираемых выходов коммутаторов 12 на (K-i)-x. уровнях коммутации.

В соответствии с логикой работы блока 9 коммутации для перехода из куба О в куб /V необходимо в основной программе выполнить следующую процедуру. Записать АО в акку- мчлятор микропроцессора и затем по команде OVT записать содержимое аккумулятора в регистр 2 с адресом Z. Данную процедуру необходимо выполнить последовательно для оставшихся коэффицинтов А,, где (1,2,..., (К-1). Таким образом, на выходе сдвигающего регистра 2 находится код куба памяти Л/, представленный в виде коэффициентов разложения.

В таблице приведен случай (фрагмент программы) для двухуровневой коммутации кубов памяти (/(2). По адресу программы ХХ40 командной MV/ записывается в аккумулятор код А0. По следующему адресу ХХ42 записана команда OVTZ, при этом в первом машинном цикле микропроцессор

0

о

5

0

5

0

5

читает команду, во втором - адрес, а в третьем выдает на адресный вход устройства адрес Z, на информационный вход код А0, а на вход задания режима работы устройства - сигнал «Запись В/В, при этом дешифратор 1 выдает на выходе логическую «1, подаваемую на синхровход регистра 2, который по приходу сигнала записи «Запись В/В записывает код А0 с информационного входа. По адресу ХХ44 командной MYI записывается в аккумулятор код А, (т. е. номер возбужденно го выхода коммутатора 12 первого уровня коммутации).

По адресу ХХ46 записана команда OVTZ, при этом в первом машинном цикле микропроцессор читает команду, во втором - адрес, а в третьем выдает на адресный вход устройства адрес Z, на информационный вход код Ai, а на вход задания режима работы устройства сигнал «Запись В/В, при этом дешифратор I выдает на выходе логическую «I, подаваемую на управляющий вход регистра 2, который по приходу сигнала «Запись В/В сдвигает код АО в регистре 2 и записывает код А с информационного входа.

При выполнении следующей команды CALL ADDR в первом машинном цикле микропроцессор считывает с информационного входа код команды CALL, этот же код дешифрируется дешифратором 4, который выдает логическую «I. на одном из выходов, через элемент ИЛИ 10 поступающую на первый вход элемента И 6, стробируя сигнал первого цикла команды. Дешифратор 4 выдает логическую «1 на первом выходе в случае появления на его входе кодов команд перехода C3ib (jMP), на втором - Ci6 (CALL), на третьем - O9,6 (RET). Элемент И 6 необходим для того, чтобы отличить коды команд перехода от данных, которые могут иметь тот же код (команды сопровождаются сигналом Ml). Положительный импульс на выходе элемента И 6 по заднему фронту устанавливает триггер 8 в единичное состояние, положительный перепад через время, обусловленное элементом 7 задержки, появляется на первом входе элемента И 5. Время задержки элемента 7 подобрано так, что не происходит совпадения положительных уровней на выходе элемента 7 задержки и сигнала Ml команды, во время которой произошло переключение (в нашем случае команды CALL). Далее микропроцессор выполняет действия, предписанные командой CALL.

При приходе любой следующей команды сигнал первого машинного цикла МГ проходит через элемент И 5 и по переднему фронту импульса на выходе элемента И 5 происходит запись адресов Ло и А куба памяти N с выхода регистра 2 в регистры 3, а также сброс триггера 8. В это же время коэффициент А поступает на вход коммутатора 11, а также коэффициент АО

поступает на вход коммутаторов 12 первого уровня и, следовательно, сигналы управления памятью подключаются к кубу памяти N. Процесс возврата в исходный куб памяти происходит аналогично. По адресу YY 40 (условно) записывается код первоначального куба памяти О в аккумулятор, по адресу YY 42 это значение записывается в регистр 2, по адресу YY 44 записанное значение сдвигается в регистре 2 и повторно записывается ноль в регистр 2. После коман- ды RET происходит возврат в куб О памяти по команде, записанной по адресу XX 53, после чего микропроцессор выполняет основную исходную программу.

Формула изобретения

5

5

0

0

5

0

суемой памяти при ограниченном числе адресных разрядов, в него введены сдвигающий регистр и с второго по /г-й регистры, где k - число членов разложения значения N, а Л - число кубов памяти, обслуживаемых устройством, причем вход признака записи членов разложения значения /V устройства подключен к входу записи сдвигающего регистра, вход установки в начальное состояние устройства подключен к входам установки в «О сдвигающего регистра и регистров с второго по к-й, информационный вход устройства подключен к информационному входу сдвигающего регистра, синхровход которого подключен к выходу первого дешифратора, выход второго элемента И подключен к входам записи регистров с второго по к-й, выходы с первого по к-й сдвигающего регистра подключены соответственно к информационным входам регистров с первого по к-й, выходы регистров с второго по к-й подключены соответственно к направляющим входам с второго по к-й блока коммутации, выходы которого подключены к выходам признаков выбора кубов памяти устройства.

О О О

О О

MV1 А,А, OVT

MV1A,At OVT

--Адреса условные.

Основная программа

Код выхода коммутатора 11 заносится в аккумулятор Содержимое аккумулятора записывается в регистр 2 с адресом z

Код выхода коммутаторов 12 заносится в аккумулятор Содержимое аккумулятора записывается в регистр 2 с адресом z, сдвигая ранее записанную в регистр 2 информацию

| Григорьев В | |||

| Л | |||

| Программное обеспечение микропроцессорных систем.-М.: Энергоатомиздат, 1983, с | |||

| Переносная печь-плита | 1920 |

|

SU184A1 |

| Устройство для адресации памяти | 1984 |

|

SU1160409A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-09-14—Подача