Изобретение относится к вычислительной технике и может быть использовано при создании микропроцессорных систем с большим объемом памяти, а также микропроцессорных графических систем отображения информации .

Цель изобретения - повьшение быстродействия.

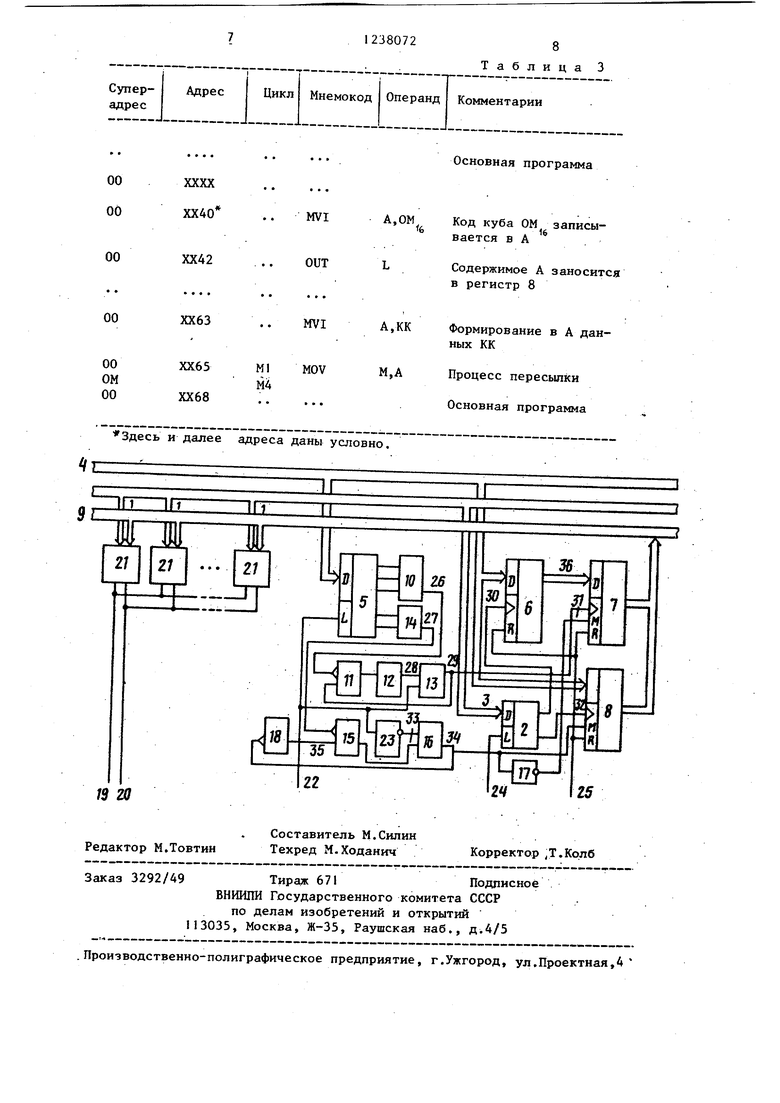

На чертеже представлена функциональная схема устройства.

Устроство содержит выход 1 младших разрядов адреса устройства, дешифратор 2 адреса, вход 3 младших разрядов адреса устройства, инфор- . мационный вход 4 устройства, дешифратор 5 команд перехода, регистры 6,7 и 3, выход 9 старших разрядов адреса устройства, элемент ИЛИ 10, триггер 11, элемент 12 задержки, элемент И 13, элемент ИЛИ 14, триггер 15, элемент И 16, элемент НЕ 17, одновибратор 18, входы 19 признака записи информации 20, признака чтения информации устройства, адресный выход 21 устройства, вход 22 признак перехода в другой куб памяти устройства, элемент НЕ 23, входы 24 признака старших разрядов адреса устройства, 25 сброса устройства, входы И выходы 26 - 36 устройства.

Устройство работает следующим образом.

Дешифратор 5 выделяет команды, приведенные в табл. 1. Предполагается, что адресное прост- ранств.о блока памяти разбито на разделы (кубы), каждый из которых может адресоваться посредством младших разрядов адреса.

Устройство может работать в двух режимах: программного перехода из адресного пространства одного куба в другой, и быстрой пересылки информации из одного куба в другой, при программном нахождении в одном и том же кубе памяти.

Выбор режима осуществляется дешифратором 5 команд перехода, так как при появлении трех первых команд (см. табл.) на первых трех выходах дешифратора 5, а следовательно, и на выходе 26 первого элемента ИЛИ 10 10ЯВИТСЯ 1, что соответствует первому режиму, а при появлении на шине данных четвертой и пятой команд (см. табл.1) на соответствующих выходах дешифратора 5 и выходе 27 второго

2380722

элемента ИЛИ 14 появится 1, что соответствует второму режиму.

Первьй режим. При включении питания микроэвм или для повторного 5 запуска в микроЭВМ формируется сигнал Сброс 25, устанавливающий регистры 6,-7 и 8 в нулевое состояние. Одновременно на входе 3 устанавливается нулевой начальный адрес, и на 10 выходе 9 также нулевой адрес. Таким образом, при пуске микроЭВМ она начи- нает выполнение программы, записанной в первом кубе памяти, адрес ко35

45

50

16

торого равен 00.

15 Программный переход реализуется при появлении на шине данных первых команд из табл. 1.

В табл.. 2 на примере фрагмента программы показан процесс перехода

20 из куба О в куб N и обратно.

Для перехода из куба 00., в ON необходимо в определенном месте основной программы записать в аккумулятор микропроцессора (А)код ON

25 по команде МУ1 (или другой) и вывести содержимое А в регистр 6 с адресом Z по команде OUT (см. табл.2 адреса ХХХХ - ХХ42). При этом при выполнении команды OUT в первом ма30 шинном цикле микропроцессор (далее МП) читает команду, во втором - читает адрес, а в третьем - выдает на вход. 3 адрес Z, на вход 4 - код ON , а на вход 24 - сигнал Запись В/В, при этом на первом выходе дешифратора адреса 2 по совпадению сигнала Запись В/В 24 и кода Z на входе 3 появляется 1 - 30, по переднему фронту которой в регистр 6 пишется код ON - 36. При выполении следующей команды CALL ADDR в первом машинном цикле МП считывает с входа 4 код команды CALLrCD, при этом этот же код поступает на вход дешифратора 5 команд перехода и по совпадению с сигналом первого машинного цикла Ml входа 22 на первом выходе дешифратора 5 появится положительный импульс, который через элемент ИЛИ 10 поступит на вход 26 первого триггера 11 и по заднему фронту установит триггер в I, который с задержкой (на элементе 12) большей, чем время наступления второго машинного цикла, поступит на вход 28 элемента И 13, в ос55 тальных циклах команды CALL ПМ выполняет свои штатные обязанности. При приходе любой следующей команды на второй вход элемента И 13 по входу

If2 первого машинного цикла также оступит 1, которая пройдет через лемент И 13 и по линии 29.сбросит о переднему своему фронту триггер 11 в О и запишет код ON с входов j 36 в регистр 7, при этом (так как на входе 31 присутствует 1 и не бьшо обращения к триггеру 15) код ON появится на выходе 9, т.е. следующую команду МП будет выполнять ю уже в кубе ON .Возврат в исходный куб происходит аналогичным образом.

Второй режим реализуется при появлении на входе 4 четвертой и пятой команд перехода (см. табл.1). 15

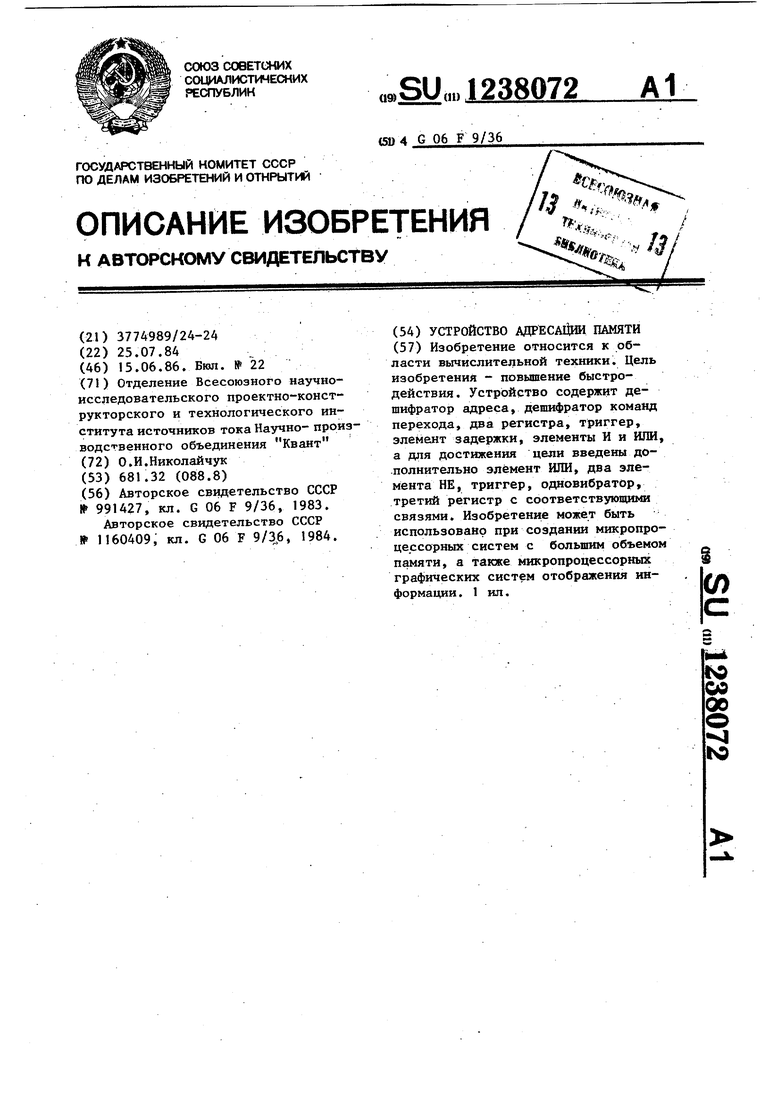

Процесс быстрой пересылки показан на примере фрагмента программы пересылки из куба 00 в куб ОМ (см. табл.3).

20

Для осуществления быстрой пересьшки данных необходимо определить уб, в который будет осуществлять- ся пересылка, для зтого в основной программе формируется в А код куба 25 ерехода ЬМ(например с помощью команды KV1) и по команде OUT записывается в регистр 8 с адресом L, при этом во втором цикле команды перехода (М4) MOV формируется 1 на выходе 34 второго элемента И 16, которая на время М4 открывает третий регистр 8, выставляя тем самым временный суперадрес.

Процесс происходит следующим образом. При появлении одной из команд 35 MOV М,А ипи MOV А,М на выходе 27 второго элемента ИЛИ 14 появляется 1, . по заднему фронту которой триггер 15 устанавливается в 1, которая поступает на второй 33 вход второго эле- 40 мента И 16, на первый вход которого поступает сигнал Ml, а на выходе 34 формируется открывающая 1, поступающая на вход управления выдачей регистра 8. Сброс триггера 15 осу- 5 ществляется выходным сигналом одновиб- ратора 18, срабатывающего по заднему фронту сигнала 34.

Формула изобретения 50

Устройство адресации памяти,содержащее дешифратор) адреса, дешифратор команд перехода, два регистра, триггер, элемент задержки, два эле- SS мента И и элемент ИЛИ, причем адрес- ,ный выход устройства подключен к входу младших разрядов адреса устройства и к входу дешифратора адреса, первый выход которого подключен к синхровходу первого регистра, информационный вход, вход установки в О и выход которого подключен соответственно к информационному входу устройства, входу сброса устройства к информационному входу второго регистра, синхровход и вход установки в О которого подключены соответственно ;:к ВЫХОДУ первого элвмвнта и и к входу сброса устройства, информационный вход которого подключен к входу дешифратора команд перехода, первая группа выходов ;которого подключена к входам первого элемента ИЛИ, выход которого подключен к счетному входу первого триггера, выход которого через элемент задержки подключен к первому входу первого элемента И, второй вход и выход которого подключены соответственно к входу признака перехода в другой куб памяти устройства и к входу установки в О первого триггера, о т- л и ч а ю щ е е с я тем, что, с целью повьшения быстродействия, в |Него введены второй элемент ИЛИ, два элемента НЕ, второй триггер, одновибратор, третий регистр, причем вход признака перехода в другой куб памяти устройства подключен к входу выборки дешифратора команд перехода и через первый элемент НЕ к первому входу второго элемента И, второй вход и выход которого подключены соответственно к выходу второго триггера и к входу выборки третьего регистра, информационный вход, вход установки в О и синхровход которого подключены соответственно к информационному входу устройства, входу сброса устройства и второму выходу дешифратора адреса, стробиру- ющий вход дешифратора адреса подключен к входу признака наличия старших разрядов адреса устройства, входа признаков записи и чтения являются выходами признаков соответственно записи и чтения устройства, вторая группа выходов дешифратора команд перехода подключена к входам второго элемента ИЛИ, выход которого подключен к счетному входувторого триггера , вход установки в О которого подключен к выходу одновибратора, выход второго элемента И подключен к входу одновибратора, через второй элемент НЕ - к входу выборки второго регистра, выход которого объединен с выходом третьего регистра и

00

00

00

N

ХХ40

ХХ42

ХХ44

ADDR

MVI А,о Код куба памяти ON

заносится в аккумулятор (А)

OUT Z Содержимое А записывается в регистр 6 с адресом Z

CALL ADDR Переход в куб ON с

адреса ADDR

Вьтолнение программы

Здесь и далее адреса даны условно.

подключен к выходу старших разрядов адреса устройства.

Таблица 1

Таблица 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации памяти | 1984 |

|

SU1160409A1 |

| Устройство для адресации памяти | 1987 |

|

SU1442990A1 |

| Устройство для синхронизации обмена микропроцессора с памятью отображения | 1989 |

|

SU1786489A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для адресации памяти | 1987 |

|

SU1481760A1 |

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

Изобретение относится к области вычислительной техники. Цель изобретения - повьшение быстродействия. Устройство содержит дешифратор адреса, дешифратор комаид перехода, два регистра, триггер, элемент задержки, элементы И и ШШ, а для достижения цели введены до- .полнительно элемент ШШ, два элемента НЕ, триггер, одновибратор, третий регистр с соответствующими связями. Изобретение может быть использовано при создании микропроцессорных систем с большим объемом памяти, а также микропроцессорных графических систем отображения информации. 1 ил. i О) 1C 00 00 lN9

| Устройство для адресации памяти микро-ЭВМ | 1980 |

|

SU991427A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для адресации памяти | 1984 |

|

SU1160409A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-07-25—Подача