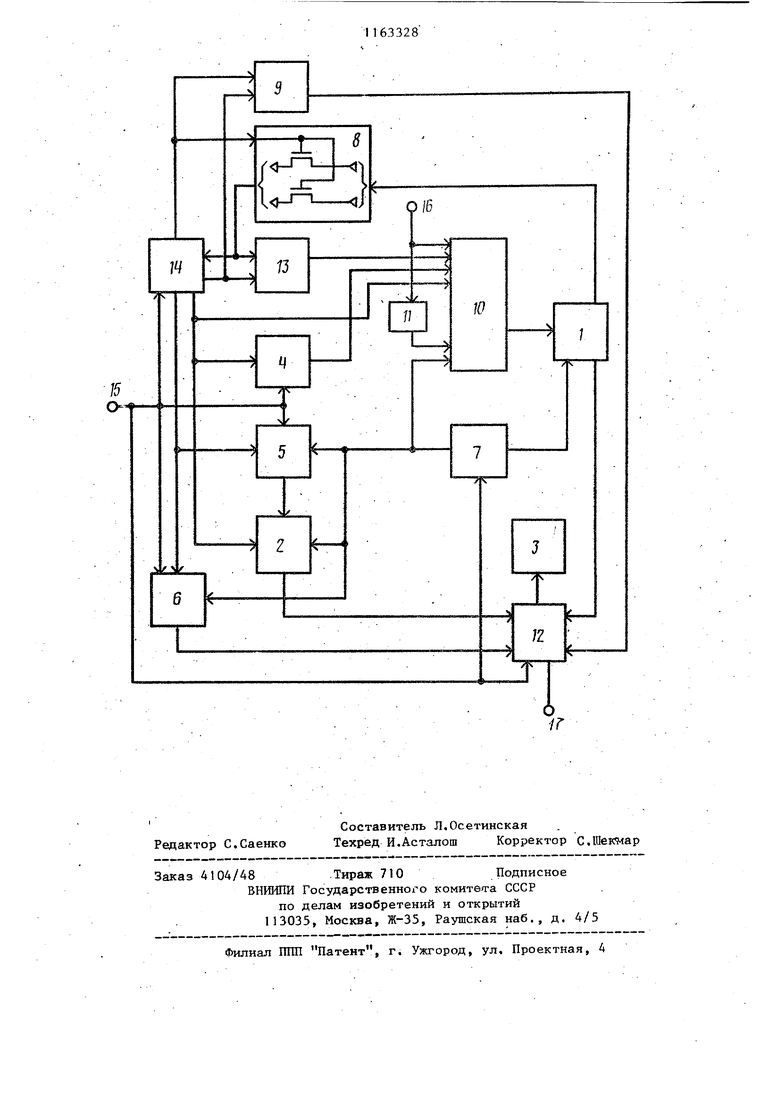

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах для контроля микро-ЭВМ. Цель изобре гения - повьшение достоверности контроля путем проверки микро-ЭВМ в реальном масштабе времени. На чертеже представлена блок-схем предлагаемого устройства для контрол микро-ЭВМ. Устройство содержит блоки 1 и 2 памяти, многоразрядный индикатор 3, счетчики 4 - 6, блок 7 ввода-вывода информации, блок 8 ключей, построенный, например, на МШ-транзисторах, элемент И 9, мультиплексор 10, элемент НЕ 11, регистры 12 и 13, контро лируемую микро-ЭВМ 14, вход Пуск 15, вход Режим 16, выход Конец контроля 17.. Адрес, поступающий на блок I памя ти, снимается с выходов мультиплексо ра 10, а формируется он либо на выходах блока 7 ввода-вывода, либона выходах регистра 13 и счетчика 4 IB зависимости от режима, задаваемого с входа Режим 16. По данному адресу блок 1 памяти вьщает входные воз действия на контролируемую микро-ЭВМ Ни признак правильности выходной информации с контролируемой микpipЭВМ 14. Заполненж информацией блоко 1 и 2 памятки счетчика 6 осуагествля ется с блока 7 ввода-вывода. По окон чании ввода инфо{Я4 ции на шине Режим 16 изменяется сигнал и мультиплексор 10 перекгаочает адресный вход блока 1 памяти на выходы регистра 13 и счетчика 4. Поясним принцип работы.блока I памяти на примере значений, приведенных в таблице (в шестнадцатиричиой форме ).. . При каждом обращении к цифровьм входам-выходам (которые яЬляются совмещенными по входу и выходу, так как; существуют огр вничения на число выводов корпуса микро-ЭВМ 14 ) проис: ходит наращивание счетчика 4, а еледовательноэ изменение зоны блока 1 памяти. При этом изменяется (или не изменяется) информация на цифровых выходах микро- )4. Эта информация запоминается иа регистре 13 и через мультиплексор 10 поступает на адресные входы блока 1 памяти. Таким образом, выбоЬ ячейки в блоке 1 памяти определяется двумя составляющими адреса. В выбранной ячейке памяти в блоке 1. памяти содержатся входные тесты (воздействия и разряд, определяющий правильность работы микро-ЭВМ 14 при вьщаче информации на цифровые выходы. Входные воздействия поступают на микро-ЭВМ 14 только в том случае, если с микроЭВМ 14 поступает признак Ввод на блок 8 ключей. Эта ситуация возникает только в том случае, ксяда цифровые входы-вьрсоды микро-ЭВМ 14 находятся в состоянии Вход и на регистр 13 не поступает признак Вывод с микро-ЭВМ I4. Этим обеспечивается возможность контроля совмещенных цифровых входов-выходов микроэвм 14. «Определяющий разряд, равный единице, характеризует правильность работы микро-ЭВМ 14 при вьдаче управляющих воздействий на ее цифровые входы-выходы. Остальные определяющие разряды равны нулю. Заполнение блока 1 памяти производится блоком 7 ввода-вьгеода информации. Шина Режнм 16 подключает адресные входы блока 1 памяти к выходам блока 7 ввода-вывода информации, который подаёт на адресные входы блока 1 памяти информацию, соответствующую эталонной выходной информации микро-ЭВМ 14, При подаче адреса на блок 1 памяти должны производиться запись- значения определяющего разряда, равного единице, и запись входных воздействий, если они присутствуют. В противном случае значение входных воздействий рав«о нулю. Регистр 13 вьтолняет Лункцию хранения адреса при обращении к блоку 1 памяти. Изменение информации в регистре 13 происходит по признаку Вьшод из микро-ЭВМ 14 при вьщаче инЛормации на цифровие выходы. При подаче входных воздействий в регистре 13 сохраняется последняя выходная реакция микро-ЭВМ 14. Длительность цикла обращений на цифровые входы-выходы фиксируется счетчиком 5. Совпадение его значения с эталонным проверяется блоком 2 памяти, содержащим определяющий разряд по каждому адресу, равному содержимому счетчика. 5. Контроль микро-ЭВМ 14 производится следующим образом. По сигналу на вход Пуск 15 происходит сброс счетчиков 4 и-5, а также запуск счетчика 6, При этом сбра сьшается также регистр 12. По оконча нии сигнала на входе Пуск 1 SlipoHC ходит запуск микро-ЭВМ 14, которая начинает выполнять определенную программу. При этом происходит изменение информации на ее выходах и требу ется изменять соответствующим образо информацию на ее входах. В данном случае рассматривается наиболее общий вариант, когда шины входов и выходов контролируемой микро-ЭВМ 14 совмещены. При считьшании информации с входов-выходов микро-ЭВМ 14 по ее сигналу происходит запись этой инфор мации в регистр 13. По признаку обращения из микро-ЭВМ 14 происходит считьгеание информации из блока 1 памяти, а по окончании признака обращения - наращивание содержимого счет чика 4. Первый адрес блока памяти определяется нулевым содержимым счет чика 4 и информацией, записанной в регистр 13. В выбранной ячейке блока 1 памяти содержатся входные воз-, действия, которые считьюаются на вхо ды блока 8 ключей. Входные воздействия поступают на входы микро-ЭВМ 14 только в том случае, если с микроЭВМ 14 поступает признак Ввод на блок 8 ключей. Эта ситуация возникает, когда цифровые входы-выходы микро-ЭВМ 14 находятся в состоянии .Вход и на регистр 13 не поступает признак Вывод с микро-ЭВМ 14. Этим обеспечивается возможность контроля совмещенных входов-выходов микроЭВМ 14. Определяющий разряд блока 1 памяти, равный единице, характеризует правильность работы микро-ЭВМ 14 при вьдаче управляющих воздействий на ее цифровые выходы. Остальные зна чения определяющего разряда равны нулю. Изменение информации в регистре 13 происходит по признаку Вьюод микро-ЭВМ 14 при выдаче информации на выходы. При подаче входных воздействий в регистре 13 сохраняется последняя выходная реакция микроЭВМ 14. Длительность цикла обращений к цифровым входам-ьыходам фиксируется счетчиком 5. Совпадение его значе ния с эталонным проверяется блоком 2 памяти, содержап1им определяющий разряд, характеризующий правильную длительность между обращениями микро-ЭВМ 14 по входам-выходам. Мультиплексор 10 осуществляет коммутацию адреса и управляющих сигналов, которые поступают либо с блока 7 ввода-вывода, либо с микроЭВМ 14 и счетчика 4. Сигнал с входа , Режим 16 поступает на первый управляющий вход мультиплексора 10 и через элемент НЕ 11 на другой управляющий вход мультиплексора 10. Элемент И 9 вьшолняет роль фиксатора возможной неисправности микроЭВМ 14. При эгой неисправности микроЭВМ 14 вьщает два признака: Ввод, на блок 8 ключей и Вьшод йа регистр 13, что соответствует ситуации, когда цифровые входьг-выходы микроЭВМ 14 находятся в состоянии Вывод и блок 8 ключей находится в состоянии входа, т.е. передает сигналы блока памяти 1 на входы-выходы микро-ЭВМ 14. Следовательно, возможна ситуация наложения сигналов блока 8 ключей и сигналов микро-ЭВМ 14, Элемент И 9 фиксирует это состояние на регистре 1 2 и многоразрядном индикаторе 3. Разбраковка микро-ЭВМ 14 начинается с того, что мультиплексор 10 по сигналу со входа Режим 16 подключает к первым адресным входам блока I памяти выходы регистра 13. Этим обеспечивается подача информации цифровых выходов микро-ЭВМ 14 на адресные входы блока 1 памяти. Вторые адресные входы блока 1 памяти формируются путем подсчета числа обращений микро-ЭВМ 14 к внешним устройствам. Счетчик 4 подсчитывает эти обращения. В исходном состоянии содержимое счетчика 4 равно нулю. Сформированный таким, образом адрес выбирает в блоке 1 памяти значения определяющего разряда и входных воздействий на микро-ЭВМ 14. Разделение входных и выходных состояний цифровых входов-выходов микро-ЭВМ 14 осуществляется самой ми{ ро-ЭВМ 14 по ее выходным признакам Ввод и Вьгеод. По сигналу Вьгоод запоминается выходная информация микро-ЭВМ 14 в регистре 1 3 до следующего появления признака Вьшод. При появлении признака Ввод происходит считьтание из блока I памяти входной информации на микро-ЭВМ 14 через блок 8 ключей, выходы которого могут находиться .в трех состояниях: Нуль, Единица и Обрыв, т.е. ни Нуль, ни Единица. В состоянии Обрыв выходы многоканального блока 8 ключей находятся при от сутствии признака Ввод с выхода микро-ЭВМ 1А. При наличии последнего выходы блока 8 ключей находятся в состояниях,соответствующих выходной информации блока 1 памяти. Таким образом осуществляется подача входных воздействий на микро-ЭВМ 14. В случае прихода неверной информации с цифровыхВЫХОДОВ микро-ЭВМ 14, не со ответствующей эталонной таблице тестов , происходит считьгоание из определякйцего разряда блока 1 памяти нуля в регистр 12, который фиксирует неправильность функционирования микро-ЭВМ 14. Таким образом, неправильная выходная реакция микро-ЭВМ 14 всегда фиксируется определяняцим разрядом блока 1 памяти исходя из построения тестов (таблица ). Конец контроля микро-ЭВМ 14 определяется с помощью счетчика 6, в который перед началом контроля из бло ка 7 ввода-вьшода записьгеается установка, указьшающая на промежуток вре мени не меньше, чем время вьшолнения контрольного примера, . { По истечении заданного времени счетчик 6 выдает на регистр 12 сигнал, означающий окончание контроля, который подается на выход 17 Конец контроля. Временные интервалы между обращениями микро-ЭВМ 14 к цифровым входам-выходам фиксируются с помощью счетчика 5, который подсчитьгоает число команд (либо число обращений к памяти ) микро-ЭВМ 14. Сравнение чис- ла команд, фиксируемых счетчиком 5, осуществляется в блоке 2 памяти по значению определяющего разряда, который формируется аналогично определяющему разряду в блоке .1 памяти. Ввод ;эталонной информации в блок 2 памяти осуществляется аналогично вводу информации в блок 1 памяти. Микро-ЭВМ 14 контролируется по контрольным примерам целевой программы, заложенной внутри нее. В случае, если для реализации задачи необходима дополнительная память, то к ее магистральным вьгаодам подстыковывается дополнительный блок памяти, который может отсутствовать или присутствовать в зависимости от последнего требования .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микроЭВМ | 1988 |

|

SU1578716A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для управления роботом | 1983 |

|

SU1228074A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРО-ЭВМ, содержащее блок ввода-вывода информации, три счетчика, два регистра, первый блок памяти, информационный вход которого соединен с первым выходом блока ввода-вывода, отличающееся тем, что, с целью повьшения достоверности контроля путем проверки в реальном масштабе времени, оно содержит второй блок памяти, мультиплексор, элемент НЕ, блок ключей, многоразрядный индикатор, причем вход Пуск устройства соединен с первыми сбросовыми входапи первого, второго и третьего счетчиков, блока ввода-вьшода, первого регистра и контролируемой микроЭВМ, второй выход блбка ввода-вывода соединен с вторыми сбросовьи-1И входами, второго и третьего счетчиков, информационным входом второго блока памяти и первым информационным входом мультипт ксора, выход которого соединен с адресным входом первого блока памяти, первый и второй информационные выходы которого соединены соответственно с первым информационным входом лервого регистра и через блок ключей с информационными входами контролируемой микро-ЭВМ и второго регистра, выход которого и выход первого счетчика соединены с вторым и третьим информационными входами мультиплексора, первый и второй управляющие входы которого соединены непосредственно и через элемент НЕ с входом Режим устройства, а третий управляющий вход - с. выходом Запрос ввода-вьшода контролируемой микроЭВМ, соединенным также со счетным входом первого счетчика и входом Чтение второго блока памяти, счетные входы второго и третьего счетчи(О ков соединены с тактовым выходом контролируемой микро-ЭВМ, выход второго счетчика соединен с адресным входом второго блока памяти, первый вход элемента И и синхровход второго яаЛ, регистра соединены с синхровходом контролируемой микро-ЭВМ, выход приз3t нака Ввод которой соединен с управ:о : ю эо лякяцим входом блока ключей и вторым входом элемента И, выход которого соединен с разрешающим входом первого регистра, входы разрядов Конец контроля и Останов которого соединены соответственно с выходами третьего счетчика и второго блока памяти, информационный выход соединен с входом многоразрядного индикатора, а выход разряда Конец контроля является одноименным выходом устройства.

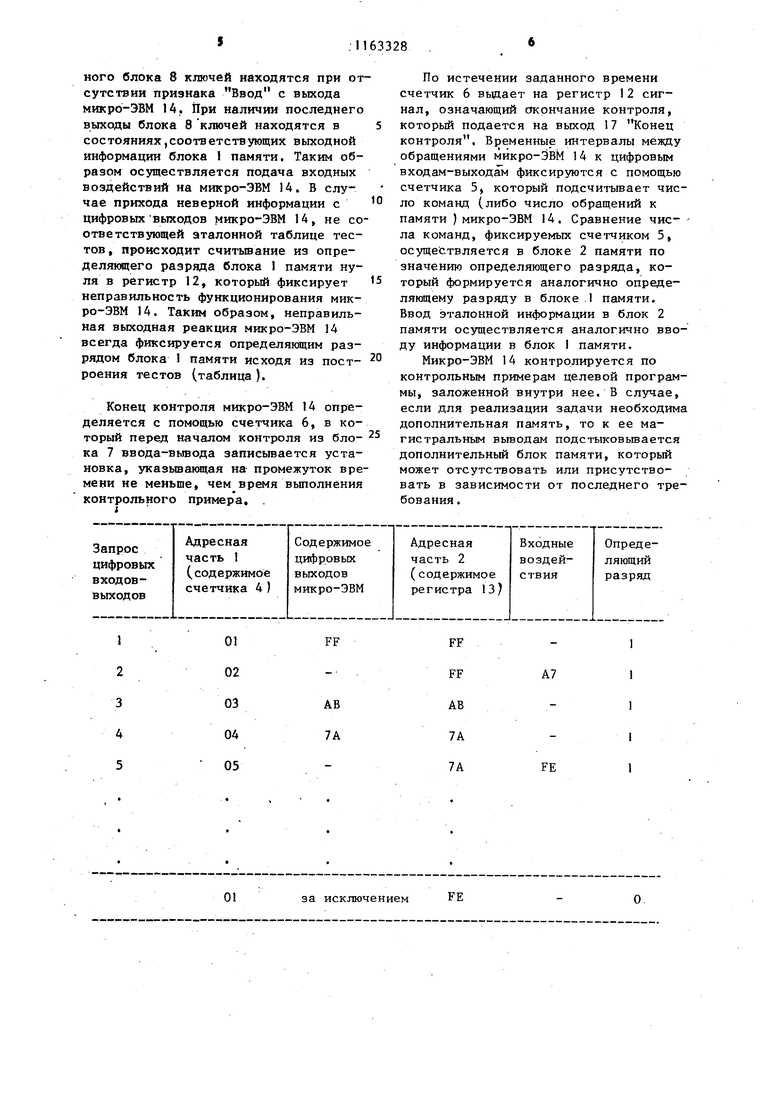

1 2 3 4 5

01 02 03 04 05

FF

АВ 7А

за исключениемFE

О

FF FF АВ 7А 7А

А7

FE

Авторы

Даты

1985-06-23—Публикация

1982-10-11—Подача