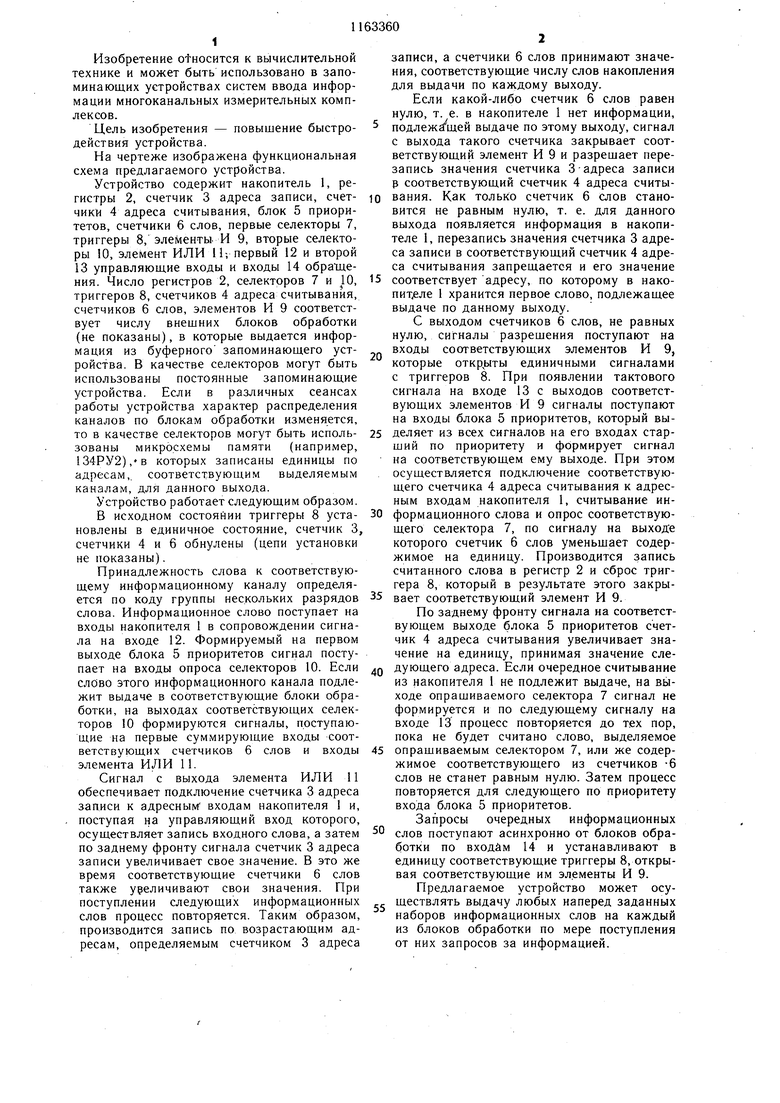

Изобретение о1носится к вычислительной технике и может быть использовано в запоминающих устройствах систем ввода информации многоканальных измерительных комплексов. Цель изобретения - повышение быстродействия устройства. На чертеже изображена функциональная схема предлагаемого устройства. Устройство содержит накопитель 1, регистры 2, счетчик 3 адреса записи, счетчики 4 адреса считывания, блок 5 приоритетов, счетчики 6 слов, первые селекторы 7, триггеры 8, элементы. И 9, вторые селекторы 10, элемент ИЛИ П; первый 12 и второй 13 управляющие входы и входы 14 обратцения. Число регистров 2, селекторов 7 и 10, триггеров 8, счетчиков 4 адреса считывания, счетчиков 6 слов, элементов И 9 соответствует числу внешних блоков обработки (не показаны), в которые выдается информация из буферного запоминающего устройства. В качестве селекторов могут быть использованы постоянные запоминающие устройства. Если в различных сеансах работы устройства характер распределения каналов по блокам обработки изменяется, то в качестве селекторов могут быть использованы микросхемы памяти (например, 134РУ2),«в которых записаны единицы по адресам,, соответствующим выделяемым каналам, для данного выхода. Устройство работает следующим образом. В исходном состоянии триггеры 8 установлены в единичное состояние, счетчик 3, счетчики 4 и 6 обнулены (цепи установки не показаны). Принадлежность слова к соответствующему информационному каналу определяется по коду группы нескольких разрядов слова. Информационное слово поступает на входы накопителя 1 в сопровождении сигнала на входе 12. Формируемый на первом выходе блока 5 приоритетов сигнал поступает на входы опроса селекторов 10. Если слово этого информационного канала подлежит выдаче в соответствующие блоки обработки, на выходах соответствующих селекторов 10 формируются сигналы, поступающие на первые суммирующие входы соответствующих счетчиков 6 слов и входы элемента ИЛИ 11. Сигнал с выхода элемента ИЛИ 11 обеспечивает подключение счетчика 3 адреса записи к адресным входам накопителя 1 и, поступая на управляющий вход которого. осуществляет запись входного слова, а затем по заднему фронту сигнала счетчик 3 адреса записи увеличивает свое значение. В это же время соответствующие счетчики 6 слов также увеличивают свои значения. При поступлении следующих информационных слов процесс повторяется. Таким образом, производится запись по возрастающим адресам, определяемым счетчиком 3 адреса записи, а счетчики 6 слов принимают значения, соответствующие числу слов накопления для выдачи по каждому выходу. Если какой-либо счетчик 6 слов равен нулю, т. е. в накопителе 1 нет информации, подлежг(щей выдаче по этому выходу, сигнал с выхода такого счетчика закрывает соответствующий элемент И 9 и разрешает перезапись значения счетчика 3-адреса записи Э соответствующий счетчик 4 адреса считывания. Как только счетчик 6 слов становится не равным нулю, т. е. для данного выхода появляется информация в накопителе 1, перезапись значения счетчика 3 адреса записи в соответствующий счетчик 4 адреса считывания запрещается и его значение соответствует адресу, по которому в накопит еле 1 хранится первое слово, подлежащее выдаче по данному выходу. С выходом счетчиков 6 слов, не равных нулю, сигналы разрешения поступают на входы соответствующих элементов И 9, которые открыты единичными сигналами с триггеров 8. При появлении тактового сигнала на входе 13 с выходов соответствующих элементов И 9 сигналы поступают на входы блока 5 приоритетов, который выделяет из всех сигналов на его входах старший по приоритету и формирует сигнал на соответствующем ему выходе. При этом осуществляется подключение соответствующего счетчика 4 адреса считывания к адресным входам накопителя 1, считывание информационного слова и опрос соответствующего селектора 7, по сигналу на выходе которого счетчик 6 слов уменьшает содержимое на единицу. Производится запись считанного слова в регистр 2 и сброс триггера 8, который в результате этого закрывает соответствующий элемент И 9. По заднему фронту сигнала на соответствующем выходе блока 5 приоритетов счетчик 4 адреса считывания увеличивает значение на единицу, принимая значение следующего адреса. Если очередное считывание из накопителя 1 не подлежит выдаче, на вьь ходе опрашиваемого селектора 7 сигнал не формируется и по следующему сигналу на входе 13 процесс повторяется до тех пор, пока не будет считано слово, выделяемое опрашиваемым селектором 7, или же содержимое соответствующего из счетчиков -6 слов не станет равным нулю. Затем процесс повторяется для следующего по приоритету входа блока 5 приоритетов. Запросы очередных информационных слов поступают асинхронно от блоков обработки по входим 14 и устанавливают в единицу соответствующие триггеры 8, открывая соответствующие им элементы И 9. Предлагаемое устройство может осуществлять выдачу любых наперед заданных наборов информационных слов на каждый из блоков обработки по мере поступления от них запросов за информацией.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1982 |

|

SU1075310A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1316050A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1288757A1 |

| Устройство для сопряжения | 1982 |

|

SU1022143A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1985 |

|

SU1290325A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Запоминающее устройство | 1982 |

|

SU1069000A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, информационные выходы которого подключены к одним из входов регистров и селекторов, а адресные входы подключены к выходам счетчика адреса записи и счетчиков адреса считывания, счетчики слов и триггеры, выходы которых подключены соответственно к первым и вторым входам элементов И, блок приоритетов, первый вход которого является первым управляющим входом устройства, другие входы блока приоритетов подключены к выходам элементов И, третьи входы которых объединены и являются вторым управляющим входом устройства. входами обращения которого являются первые входы триггеров, вторые входы триггеров подключены к выходам селекторов и входам записи регистров, выходы которых являются выходами устройства, входы опроса селекторов соединены с первыми входами счетчиков адреса считывания и выходами блока приоритетов, отличающееся тем, что, с целью повыщения быстродействия устройства, в него введены дополнительные селекторы и элемент ИЛИ, выход которого подключен к управляющему входу накопителя и входу счетчика адреса записи, а входы - к выходам дополнительных селекторов, соединенных также с первыми входами счетчиков слов, вторые входы которых подклю-. чены к выходам селекторов, одни из входов дополнительных селекторов соответственно объединены и подключены к информацион(rt ным входам накопителя, входы опроса дополнительных селекторов подключены к первому выходу блока приоритетов, выходы счетчиков слов соединены соответственно с вторыми входами счетчиков адреса считывания, разрядные входы которых соответственно объединены и подключены к выходам счетчика адреса записи. Oi оо оо о

| Буферное запоминающее устройство | 1980 |

|

SU888202A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1075310A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-06-23—Публикация

1984-05-03—Подача