элемент ИЛИ 11, блок 5 приоритетов, регистры 2, селекторы 7, счетчики 4 адреса считывания, счетчики 6 слов, группу 8 триггеров, группу элементов И 9. Повьппение быстродействия достигается за счет подготовки к выдаче информационных слов в моменты снижения интенсивности запросов на считьшание. Для этого в устройство

1

Изобретение относится к запоминающим устройствам и может быть использовано в вычислительной и измерительной технике для систем ввода информации многоканальных измерительных, комплексов.

Цель изобретения - повьшение быстродействия устройства.

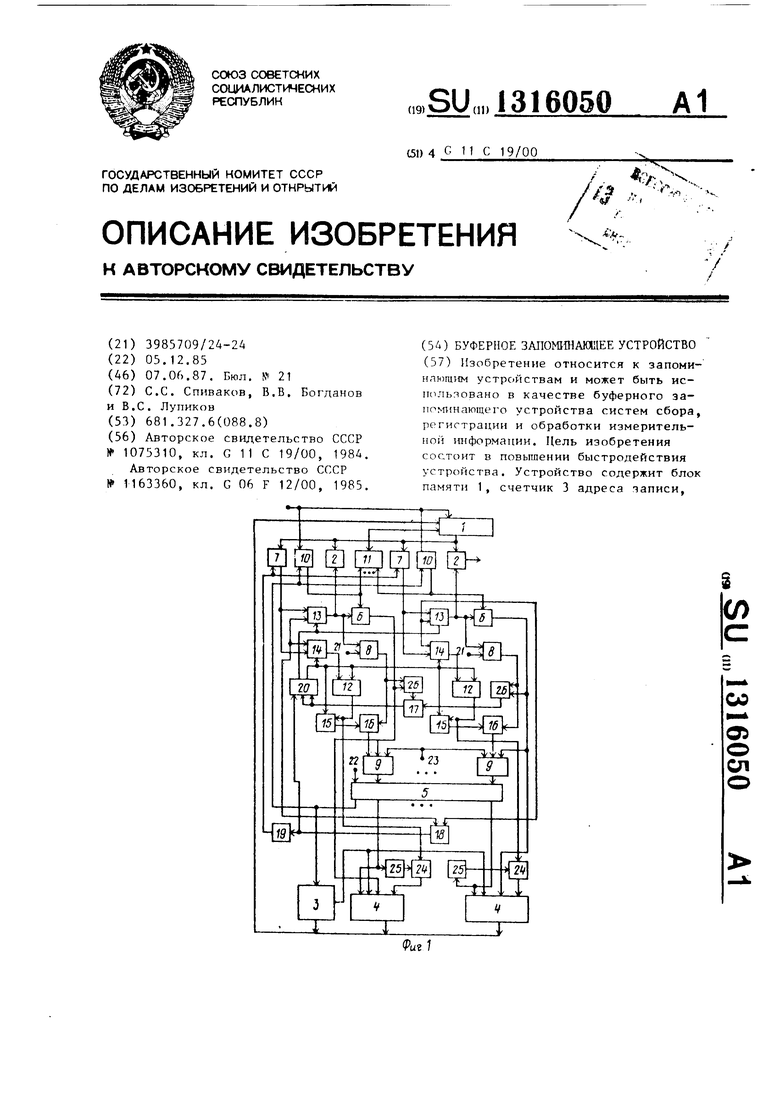

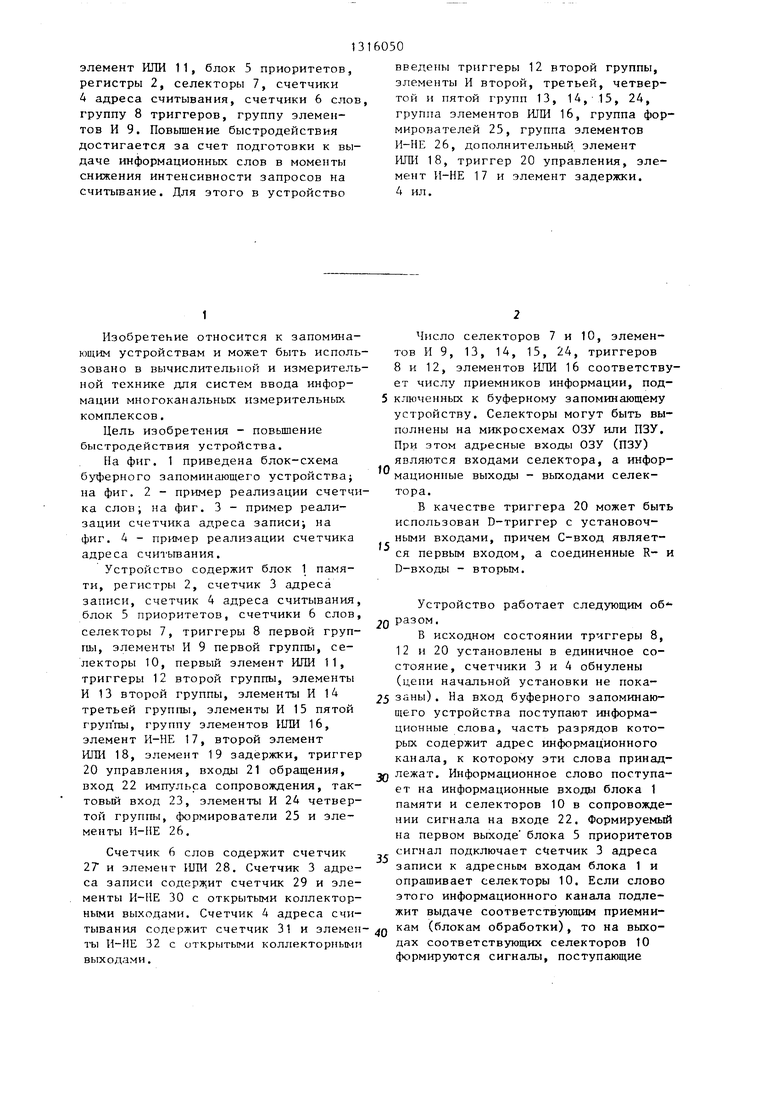

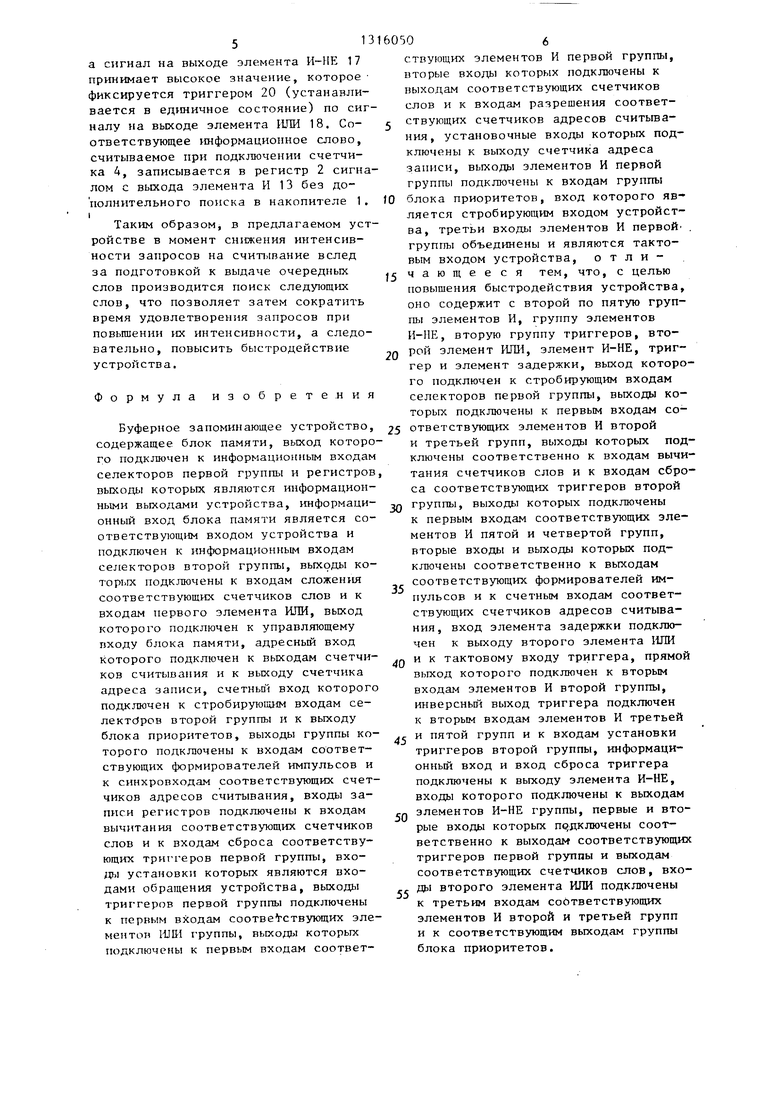

На фиг. 1 приведена блок-схема буферного запоминающего устройства на фиг. 2 - пример реализации счетчика слов; на фиг. 3 - пример реализации счетчика адреса записи; на фиг. 4 - пример реализации счетчика адреса считьтания.

Устройство содержит блок 1 памяти, регистры 2, счетчик 3 адреса записи, счетчик 4 адреса считывания, блок 5 приоритетов, счетчики 6 слов, селекторы 7, триггеры 8 первой группы, элементы И 9 первой группы, селекторы 10, первый элемент ИЛИ 11, триггеры 12 второй группы, элементы И 13 второй группы, элементы И 14 третьей группы, элементы И 15 пятой груп пы, группу элементов ИЛИ 16, элемент И-НЕ 17, второй элемент ИЛИ 18, элемент 19 задержки, триггер 20 управления, входы 21 обращения, вход 22 импульса сопровождения, тактовый вход 23, элементы И 24 четвертой группы, формирователи 25 и элементы И-НЕ 26.

Счетчик 6 слов содержит счетчик 27 и элемент ИЛИ 28. Счетчик 3 адреса записи содержит счетчик 29 и элементы И-НЕ 30 с открытыми коллекторными выходами. Счетчик 4 адреса считывания содержит счетчик 31 и элементы И-НЕ 32 с открытыми коллекторными выходами.

введены триггеры 12 второй группы, элементы И второй, третьей, четвертой и пятой групп 13, 14,-15, 24, группа элементов ШШ 16, группа формирователей 25, группа элементов Н-НЕ 26, дополнительный элемент ИЛИ 18, триггер 20 управления, элемент И-НЕ 17 и элемент задержки. 4 ил.

Число селекторов 7 и 10, элементов Р1 9, 13, 14, 15, 24, триггеров 8 и 12, элементов ИЛИ 16 соответствует числу приемников информации, под- 5 ключенных к буферному запоминающему устройству. Селекторы могут быть выполнены на микросхемах ОЗУ или ПЗУ. При этом адресные входы ОЗУ (ПЗУ) являются входами селектора, а информационные выходы - выходами селектора.

Б качестве триггера 20 может быть использован D-триггер с установочными входами, причем С-вход является первым входом, а соединенные R- и D-входы - вторым.

10

(5

Устройство работает следующим об2Q разом,

В исходном состоянии триггеры 8, 12 и 20 установлены в единичное состояние, счетчики 3 и 4 обнулены (цепи начальной установки не пока25 заны). На вход буферного запоминающего устройства поступают информационные слова, часть разрядов которых содержит адрес информационного канала, к которому эти слова принадJQ лежат. Информационное слово поступает на информационные входы блока 1 памяти и селекторов 10 в сопровождении сигнала на входе 22. Формируемый на первом выходе блока 5 приоритетов сигнал подключает с 1етчик 3 адреса записи к адресным входам блока 1 и опрашивает селекторы 10. Если слово этого информационного канала подлежит выдаче соответствующим приемни Q кам (блокам обработки), то на выходах соответствующих селекторов 10 формируются сигналы, поступающие

35

на первые (суммпретощие) входы соответствующих счетчиков 6 слов и входы элемента ИПИ 11, Сигнал с выхода элемента ИЛИ 11, поступая на управляющий вход блока 1, осуществляет запись входного слова по адресу, сфор- мированному счетчиком 3. Затем по заднему фронту сигнала на первом выходе с блока 5 счетчик 3 адреса записи увеличивает свое значение. Таким образом, производится запись информации в блок 1 по возрастающим адресам определяемым счетчиком 3. Счетчики 6 принимают значения, соответствующие числу слов, накопленных для выдачи по каждому выходу устройства. Если какой-либо счетчик 6 равен ну

лю, т.е. в накопителе 1 нет информации, подлежащей выдаче по этому выходу, то сигнал с выхода такого счетчика закрывает соответствующий элемент И 9 и разрешает перезапись значения счетчика 3 в соответствующий счетчик 4.

С выходов счетчиков 6, не равных нулю, сигналы разрешения поступают на входы соответствующих элементов И 9, которые открыты единичными сигналами с триггеров 8. При появлении тактового сигнала на входе 23 сигналы с выходов элементов И 9 поступают на входы блока 5 приоритетов, который выбирает из всех сигналов на его входах старший по приоритету и формирует сигнал на соответствующем ему выходе. При этом осуществляется подключение соответствующего счетчика А адреса считьшания к адресным входам блока 1 памяти, считьшание информационного слова, выбор соответствующего элемента И 13, а затем с задержкой на элементе 19 опрос селекторов 7. Если информационное слово должно быть выдано на выход устройства, то соответствующий селектор ,. вая элемент И 24, запрещая модифика7 формирует сигнал, который через открытый элемент И 13 осуществляет запись считанного слова в регистр 2,. уменьшение на единицу соответствующего счетчика 6 слов, сброс в нулевое состояние триггера 8 и закрытие соответствующего элемента И 9. По заднему фронту сигнала на соответствующем выходе блока 5 на выходе формирователя 25 формируется сигнал, который через открытый элемент И 24 увеличивает значение счетчика 4 адреса считывания на единицу. Если очередное считьшаемое из блока 1 ело-

50

55

цию соответствующего счетчика 4. При этом счетчик 4 сохраняет значение, соответствующее адресу найденного слова. Затем процесс повторяется для следующего по приоритету входа блока 5. В результате при отсутствии запросов в течение некоторого времени очередные информационные слова будут подготовлены к выдаче на регистрах 2, а адреса следующих найденных слов будут храниться счетчиками 4 адреса считывания. При поступлении на вход 21 запроса на считьшание устанавливается триггер 8,

1316050

- „

5

во не подлежит выдаче, то на пьгхоле соответствующего селектора 7 сигнал не формируется и по следуюп1ему сигналу на входе 23 процесс повторяется до тех пор, пока не будет считано слово, выде;1яемое соответств тощим селектором 7. Затем процесс повторяется для следующего по приоритету входа блока 5.

Запросы на считывание очередных информационных слов поступают асинхронно от приемников информации на входы 21 устройства. При неравномерном потоке запросов на считывание инфо1ТМационные слова могут быть подготовлены для выдачи всем приемникам т.е. записаны во все регистры 2, а все триггеры 8 сброшены в нулевое состояние. При этом во время ожидания прихода очередных запросов производится поиск следующих слов, подлежащих выдаче, но без записи их в регистры 2. Так как все триггеры 8 сброшены (или же некоторые счетчики 6 равны нулю), то сигнал с выхода элемента И-НЕ 17 сбрасывает триггер 20, который закрывает элементы И 13 и открывает элементы И 14 и 15. Сигналы с выходов элементов И 15 через элементы ИЛИ 16 поступают на входы элементов И 9. Блок 5 формирует сигнал на старшем по приоритету выходе, осуществляя подключение счетчика 4 к адресным входам блока 1, считыва0

0

ние слова, выбор соответствующего элемента И 14, а затем через элемент ИЛИ 18 и элемент 19 задержки опрос селекторов 7, Если информационное слово подлежит выдаче на соответствующий выход устройства, то соответствующий селектор 7 формирует сигнал, который через открытый элемент И 14 сбрасывает передним фронтом соответствующий триггер 12, закры0

5

цию соответствующего счетчика 4. При этом счетчик 4 сохраняет значение, соответствующее адресу найденного слова. Затем процесс повторяется для следующего по приоритету входа блока 5. В результате при отсутствии запросов в течение некоторого времени очередные информационные слова будут подготовлены к выдаче на регистрах 2, а адреса следующих найденных слов будут храниться счетчиками 4 адреса считывания. При поступлении на вход 21 запроса на считьшание устанавливается триггер 8,

а сигнал на выходе элемента И-ИЕ 17 принимает высокое значение, которое- фиксируется триггером 20 (устанавливается в едршичное состояние) по сигналу на выходе элемента ИЛИ 18. Соответствующее 1шформационное слово, считываемое при подключении счетчика 4, записывается в регистр 2 сигналом с выхода элемента И 13 без дополнительного поиска в накопителе 1. I

Таким образом, в предлагаемом устройстве в момент снижения интенсивности запросов на счит1,вание вслед за подготовкой к выдаче очередных слов производится поиск следующих

ствующих элементов И первой группы, вторые входы которых подключены к выходам соответствующих счетчиков слов и к входам разрешения соответс ствующих счетчиков адресов считьша- ния, установочные входы которых подключены к выходу счетчика адреса записи, выходы элементов И первой группы подключень; к входам группы

10 блока приоритетов, вход которого является стробирующим входом устройства, третьи входы элементов И первой , группы объединены и являются тактовым входом устройства, о т л и J5 чающееся тем, что, с целью

повышения быстродействия устройства, оно содержит с второй по пятую группы элементов И, группу элементов И-ПЕ, вторую группу триггеров, вто- 2Q рой элемент ИПИ, элемент И-НЕ, триггер и элемент задержки, выход которого подключен к стробирующим входам селекторов первой группы, выходы которых подключены к первым входам со- Буферное запоминающее устройство, 25 ответствующих элементов И второй

слов, что позволяет затем сократить время удовлетворения запросов при повышении их интенсивности, а следовательно, повысить быстродействие устройства.

Формула изобретения

содержащее блок памяти, выход которого подключен к информационным входам селекторов первой группы и регистров, выхода которых являются информационными выходами устройства, 1шформаци- онный вход блока памяти является соответствующим входом устройства и подключен к информационным входам селекторов второй группы, выходы ко- Topi.ix подключены к входам сложения соответствующих счетчиков слов и к входам первого элемента ИЛИ, выход которого подключен к управляющему входу блока памяти, адресный вход которого подключен к выходам счетчиков считывания и к выходу счетчика адреса записи, счетньп вход которого подключен к стробирующим входам се- лектс)ров второй группы и к выходу блока приоритетов, выходы группы которого подключены к входам соответствующих формирователей импульсов и к синхровходам соответствующих счетчиков адресов считывания, входы записи регистров подключены к входам вычитания соответствующих счетчиков слов и к входам сброса соответствующих триггеров первой группы, входа установки которьпс являются входами обра цения устройства, выходы триггеров первой группы подключены к первым входам соответствующих элементен ШШ группы, выходы которых подключены к первь м входам соответ30

35

40

и третьей групп, выходь которых подключены соответственно к входам вычитания счетчиков слов и к входам сброса соответствующих триггеров второй группы, выходы которых подключены к первь м входам соответствующих элементов И пятой и четвертой групп, вторые входы и выходь которых подключены соответственно к выходам соответствующих формирователей импульсов и к счетным входам соответствующих счетчиков адресов считывания, вход элемента задержки подключен к выходу второго элемента ИЛИ и к тактовому входу триггера, прямой которого подключен к вторым входам элементов И второй группы, инверсньп выход триггера подключен к вторым входам элементов И третьей и пятой групп и к входам установки триггеров второй группы, информационный вход и вход сброса триггера подключены к выходу элемента И-НЕ, входы которого подключены к выходам

гп элементов И-НЕ группы, первые и вторые входы которых подключены соответственно к выходам соответствующих триггеров первой группы и выходам соответствующих счетчиков слов, вхо,, ды второго элемента ИЛИ подключены к третьим входам соответствующих элементов И второй и третьей групп и к соответствующим выходам группы блока приоритетов.

45

ствующих элементов И первой группы, вторые входы которых подключены к выходам соответствующих счетчиков слов и к входам разрешения соответствующих счетчиков адресов считьша- ния, установочные входы которых подключены к выходу счетчика адреса записи, выходы элементов И первой группы подключень; к входам группы

блока приоритетов, вход которого является стробирующим входом устройства, третьи входы элементов И первой , группы объединены и являются тактовым входом устройства, о т л и чающееся тем, что, с целью

и третьей групп, выходь которых подключены соответственно к входам вычитания счетчиков слов и к входам сброса соответствующих триггеров второй группы, выходы которых подключены к первь м входам соответствующих элементов И пятой и четвертой групп, вторые входы и выходь которых подключены соответственно к выходам соответствующих формирователей импульсов и к счетным входам соответствующих счетчиков адресов считывания, вход элемента задержки подключен к выходу второго элемента ИЛИ и к тактовому входу триггера, прямой которого подключен к вторым входам элементов И второй группы, инверсньп выход триггера подключен к вторым входам элементов И третьей и пятой групп и к входам установки триггеров второй группы, информационный вход и вход сброса триггера подключены к выходу элемента И-НЕ, входы которого подключены к выходам

элементов И-НЕ группы, первые и вторые входы которых подключены соответственно к выходам соответствующих триггеров первой группы и выходам соответствующих счетчиков слов, входы второго элемента ИЛИ подключены к третьим входам соответствующих элементов И второй и третьей групп и к соответствующим выходам группы блока приоритетов.

Фиг. г

30

-

Фиг.З

Редактор Л.Ворович

Составитель С.ШустенКо Техред А.Кравчук

Заказ 2370/55 Тираж 589Подписное

ВНИИ1Ш Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

п

W W

Фиг. ч

Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1288757A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163360A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1075310A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1336118A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

Изобретение относится к запоминающим устройствам и может быть ис- пильяовано в качестве буферного за- помшающего устройства систем сбора, регистрации и обработки измерительной информации. Цель изобретения состоит в повышении быстродействия устройства. Устройство содержит блок памяти 1, счетчик 3 адреса записи. г kn СО а о ел

| Буферное запоминающее устройство | 1982 |

|

SU1075310A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163360A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-12-05—Подача