Изобретение относится к вычислительной технике и может быть использовано для построения блоков памяти с повышенным .быстродействием.

Известно запоминагадее устройство, содержащее блоки памяти, .блок связи, осуществляющий управление приемов с выдачей информации, блок приоритета и буферное запоминающее устройство, в котором каждому блоку памяти соот,ветствует один или несколько буферных регистров. В данном устройстве порядок выдачи информации осуществляется блоком приоритета. Причем при выдаче информации соблюдается следующее правило: ааявка на выдачу обрабатывается блоком связи только при условии выдачк информации по всем предыдущим обращениям.

Организация приоритетности обраще НИИ чаще всего осуществляется с помощью счетчика обращений и счетчика приоритетного признака. С каждым обращением в счетчик обращений добавляется единица, а обращению .присваивается показание счетчика, являющееся по приоритетным признакам и хранящееся в буфере, в случае выдачи информации в счетчик приоритетного признака добавляется единица, тем самым подготавливается вьодача информации на следующее по порядку обращение, приоритетный признак которого совпадает с текущим .значением счетчика приоритетного признака Г ЗНедостатком ус ройства является сложность, обусловленная необходимостью затрат большого количества оборудования и связей для организации управления.

Наиболее близким техническим реше нием к изобретению является запоминающее устройство, содержащее блоки памяти, блок управления, буферный регистр обращения, коммутатор, первы и второй входы блока .управления . подключены к соответствующим выходам буферного регистра обращения, третий и четвертый входы,: первый и второй выходы.- к соответствующим входам и выходам устройства. Управление выдачей информации в этом устройстве осу ществляется с помощью счетчиковобращения и приоритетного признака 2.

Недостатками известного устройств являются сложность, ограниченные надежность и быстродействие. Устройств имеет значительное количество оборудования (счетчики обращений и при.оритетного признака, регистры приоритетных признаков и схемы сравнения в каждом блоке памяти), большое число управляющих связей и, вследствие этого, сложные управляющие автоматы. Отсутствие очереди обращений к блокам памяти и необходимость ожидания освобождения их выходных регистрбв

числа от пре дыдущей информации снижает эффективное быстродействие данного устройства.

Цель изобретения - повышение быстродействия и- надежности устройства .

Указанная цель достигается тем, что запоминающее устройство, содержащее блоки памяти, коммутатор, блок управления и регистр, информационные входы которого.являются информационными входами устройства, управляющий вход регистра является первы управляющим входом устройства, первый и второй выходы регистра подключены соответственно к первому и второму входу блока управления, третий и четвертый входы которого являются соответственно вторым и третьим входами устройства, первый и второй выходы блока управления являются соответственно первым и вторым выходами устройства , выходы коммутатора являются информационными выходами устройства, включает блоки синхронизации, блоки регистров информации, -блок-буферных регистров и блок регистров адресов, выход которого подключен к пятому вх.оду блока управления, и к управляющему входу коммутатора,, первый вход блока регистров адресов подключен к первому входу олока управления, третий и четвертый .выходы которого подключены соответственно к второму и третьему входам блока регистров адресов, информационные входы коммутатора, подключены к информационным выходам блоков Пё1МЯ.ТИ, ИН -.

фоЕячационные входы которых подключены к информационным выходам соответствующих блоков буферных регистров, адресные входы блоков памяти подключены к адреснЬам выходам соотвествующих блоков буфернь1х региЬтров, первый управляющий выход котррых подключен к первьом входам соответствующих блоков синхронизации, вторые управляющие выходы блоков буферных регистров подключены к вторым входам соответствующих блоков синхронизации, первые выходы которых подключены к первым управляющим входам соответствующих блоков буферных регистров, вторые управляющие выходы блоков синхронизации подключены к управляющим . входам соответствукяцих блоков памяти, третьи выходы блоков синхрот низации подключены к первым управляющим входам соответствующих блоков регистров инфopv|aции, вторые управляющие входы которых подключены к пятому выходу блока управления, первые управляющие выходы блоков регистров информации подключены к шестому вход блока управления, седьмой вход и шестой выход которого подключены соответственно к третьим управляющим выходам и вторым управляющим входам

блоков буферных регистров, вторые, управляющие выходы блоков буферных регистров подключены к третьим входам соответствующих блоков синхронизации

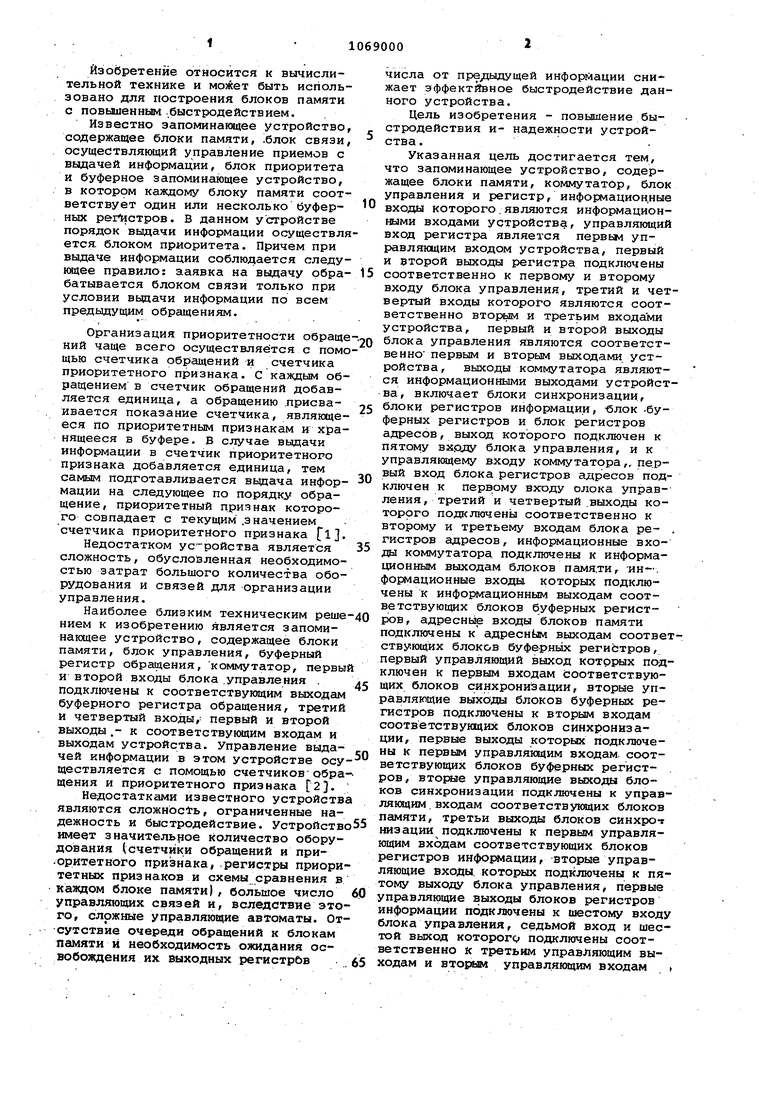

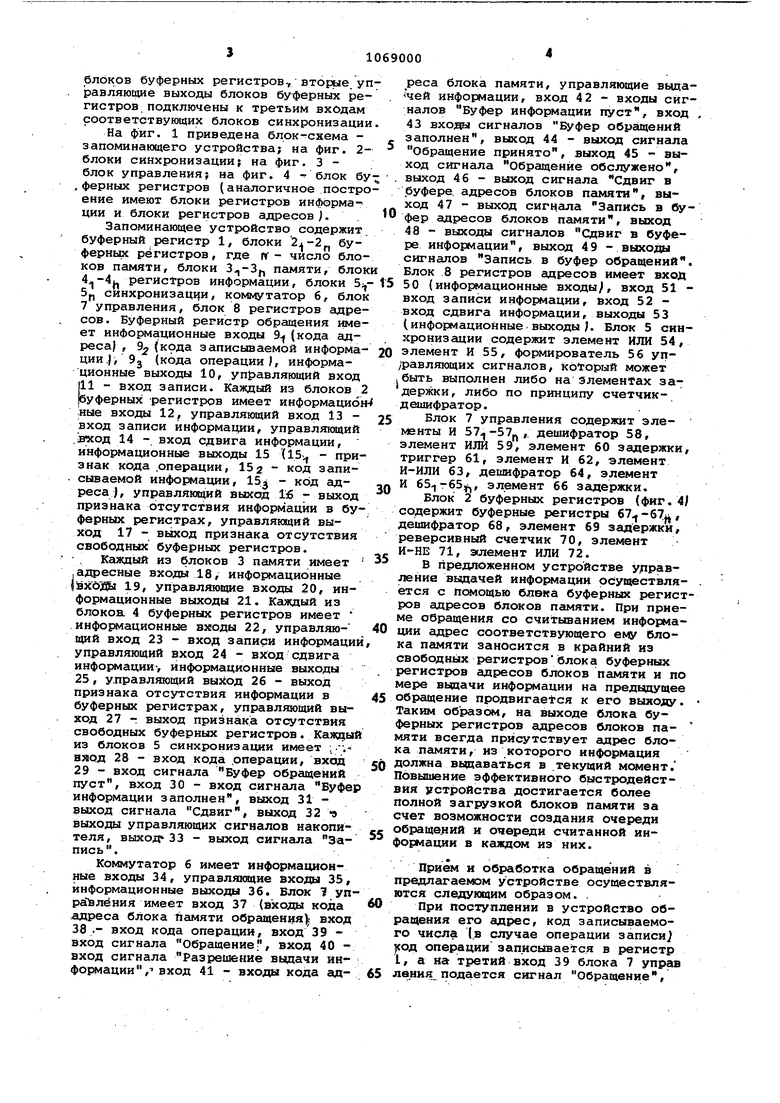

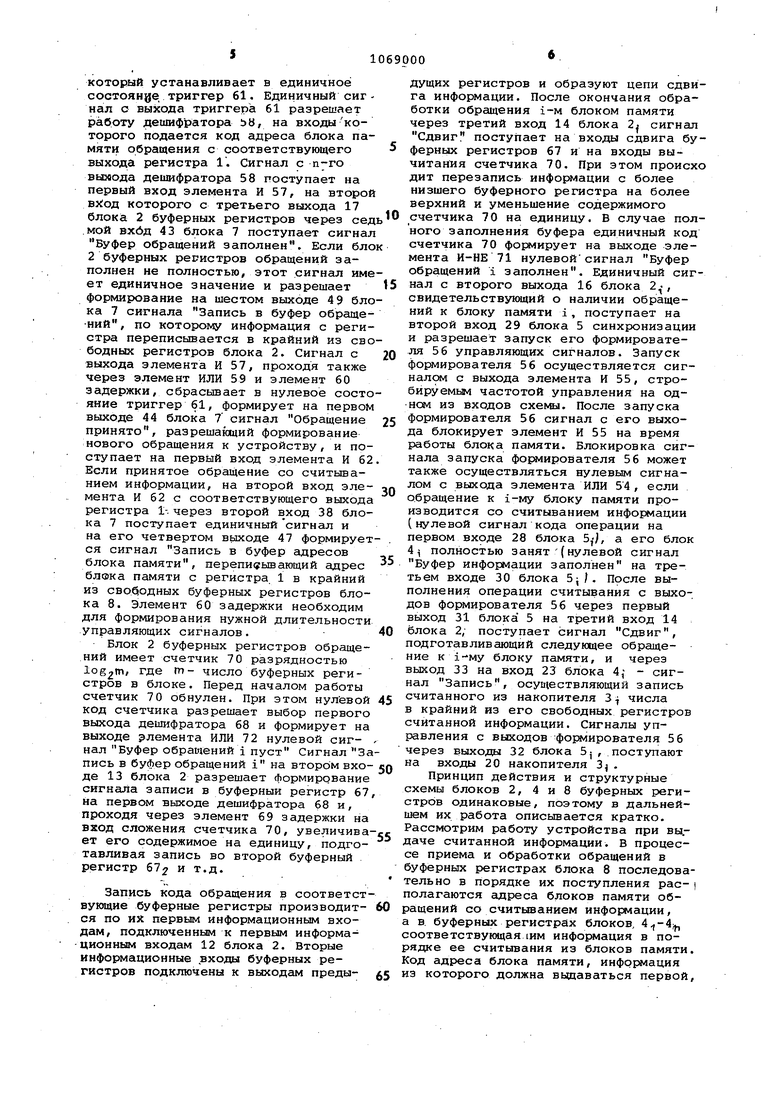

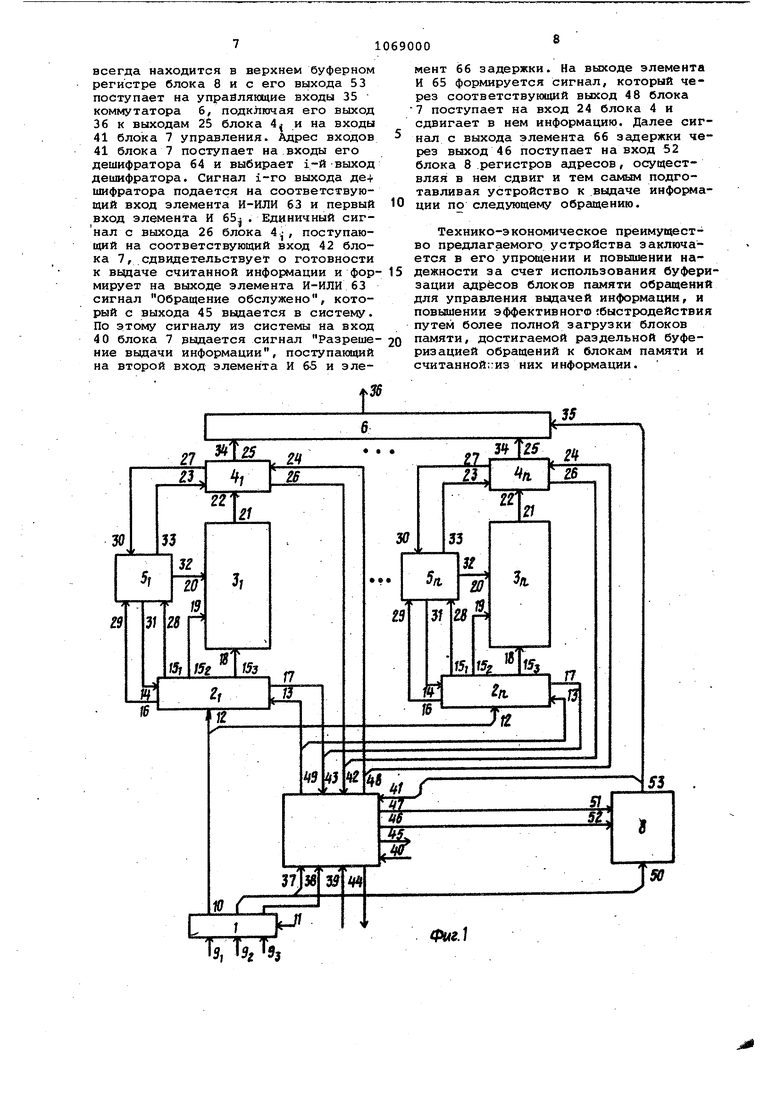

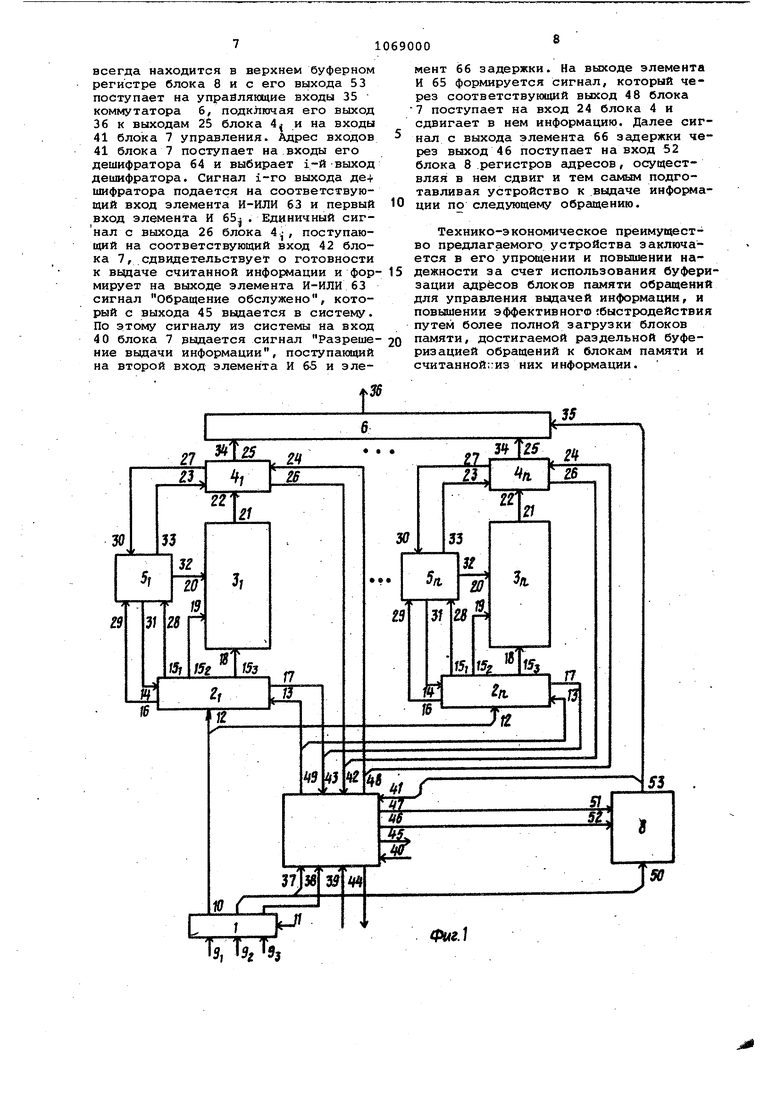

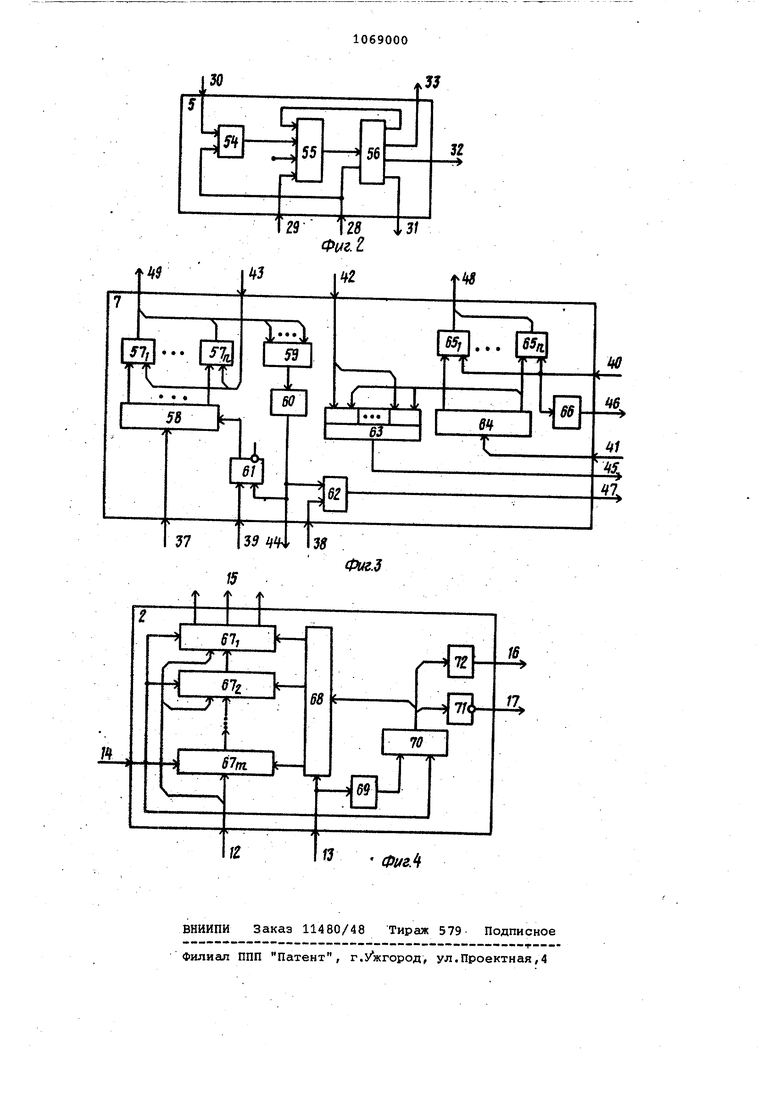

На фиг. 1 приведена блок-схема запоминающего устройства; на фиг. 2блоки синхронизации на фиг. 3 блок управления; на фиг. 4 блок бу, ферных регистров (аналогичное .построение имеют блоки регистров информации и блоки регистров адресов). .

Запоминающее устройство содержит буферный регистр 1, блоки буферных регистров, где rf - число блоков памяти, блоки , памяти, блок регистров информации, блоки 5;,Sf, синхронизац{;и, коммутатор 6, блок 7 управления, блок 8 регистров адресов. Буферный регистр обращения имеет информационные входы 9(кода адреса) , 9 (крда записываемой информации.|; 9з (кода операции J, информационные выходы 10, уп{ авляющий вход 11 - вход записи. Каждый из блоков 2 буферных регистров имеет информацией :ные входы 12, управляющий вход 13 вход записи информации, управлякиций

.;вчсод 14 -. вход сдвига информации, информационные выходы 15 (15. - признак кода .операции, 15г - код записываемой информации, 15з код адреса ), управляющий выход 16 - выход признака отсутствия информации в буферных регистрах, управляющий выход 17 - вьЬсод признака отсутствия свободных буферных регистров.

Каждый из блоков 3 памяти имеет

.адресные входы 18, информационные

|вх6йЬ1 19, управляющие входы 20, информационные выходы 21. Каждый из блокоа 4 буферных регистров имеет информационные входы 22, управляющий вход 23 - вход записи информации управляющий вход 24 - вход сдвига информации-, информационные выходы 25, улравляющий выход 26 - выход признака отсутствия информации в буферных регистрах, управляющий выход 27 т выход признака отсутствия свободных буферных регистров. Кажцый из блоков 5 синхронизации имеет :.. вход 28 - вход кода .операции, вхсщ 29 - вход сигнала Буфер обращений пуст, вход 30 - вход сигнала Буфер информации заполнен, выход 31 выход сигнала Сдвиг, выход 32 -э выходы управляющих сигналов накопителя, выход 33 - выход сигнала Запись.

Коммутатор 6 имеет информационные входы 34, управляющие входы 35, информационные выходы 36. Блок 1 упраЬлёния имеет вход 37 (входы кода адреса блока Памяти обращения) вход 38.- вход кода операции, вход 39 вход сигнала Обращение, вход 40 вход сигнала Разрешение выдачи инфОЕЯмации, вход 41 - входы кода адреса блока памяти, управляющие выда чей информации, вход 42 - входы сигналов Буфер информации пуст, вход 43 входы сигналов Буфер обращений заполнен, выход 44 - выход сигнала Обращение принято, выход 45 - выход сигнала Обращение обслужено, выход 46 - выход сигнала Сдвиг в буфере, адресов блоков памяти, выход 47 - выход сигнсша Запись в буфер адресов блоков памяти, выход 48 - выходы сигналов Сдвиг в буфере информации, выход 49 - выходы сигналов Запись в буфер обращений. Блок 8 регистров адресов имеет вход 50 (информационные входы/, вход 51 вход записи информации, вход 52 вход сдвига информации, выходы 53 (информационные выходы 7. Блок 5 синхронизации содержит элемент ИЛИ 54, элемент И 55, формирователь 56 упуравляющих сигналов, который может .быть выполнен либо на элементах задержки, либо по принципу счетчикдешифратор.

Блок 7 управления содержит элементы И ,, дешифратор 58, элемент ИЛИ 59, элемент 60 задержки, триггер 61, элемент И 62, элемент И-ИЛИ 63, дешифратор 64, элемент И ),1,, элемент 66 задержки.

Блок 2 буферных регистров (фиг. 4| содержит буферные регистры 67.|-67jj, дешифратор 68, элемент 69 задержки, реверсивный счетчик 70, элемент И-НЕ 71, зшемент ИЛИ 72.

В предложенном устройстве yjnpasление выдачей информации осуществляется с помощью блвка буферных регистров адресов блоков памяти. При приеме обращения со считыванием информации адрес соответствующего evy блока памяти заносится в крайний из свободных регистровблока буферных регистров адресов блоков памяти и по мере выдачи информации на предьздущее обращение пpoдвигaetcя к его выходу. Таким образом, на выходе блока буферных регистров адресов блоков памяти всегда присутствует адрес блока псшяти, из которого информация должна вьщаваться в .текущий момент. Повышение эффективного быстродействия }гстройства достигается более полной загрузкой блоков памяти за счет возможности создания очереди обращений и опереди считанной информации в каждом из них.

Прием и обраб.отка обращений в предлагаемом устройстве осуществляются следующим образом. .

При поступлении в устройство обращения его адрес, код записываемого числа I.B случае операции записи/ сод операции записывается в регистр I, а на третий вход 39 блока 7 управ лвния подается сигнал Обращение,

который устанавливает в единичное состояние, триггер 61. Единичный сиг нал с вызсода триггера 61 разрешает работу дешифратора ЬВ, на входыкоторого подается код адреса блока памяти обращения с соответствующего выхода регистра 1. Сигнал с выхода дешифратора 58 поступает на первый вход элемента И 57, на второй вх:од которого с третьего выхода 17 блока 2 буферных регистров через сед .мой вхбд 43 блока 7 поступает сигнал Буфер обращений заполнен. Если бло 2 буферных регистров обращений заполнен не полностью, этот сигнал имеет единичное значение и разрешает формирование на шестом выходе 49 блока 7 сигнала Запись в буфер обращений, по которому информация с регистра переписывается в крайний из свободных регистров блока 2. Сигнал с выхода элемента И 57, проходя также через элемент ИЛИ 59 и элемент 60 задержки, сбрасывает в нулевое состояние триггер 61, формирует на первом выходе 44 блока 7 сигнал Обращение принято, разрешающий формирование нового обращения к устройству, и поступает на первый вход элемента И 62 Если принятое обращение со считыванием информации, на второй вход элемента И 62 с соответствующего выхода регистра 1-. через второй вход 38 блока 7 поступает единичный сигнал и на его четвертом выходе 47 формирует СИ сигнал Запись в буфер адресов блока памяти, переписывающий адрес блока памяти с регистра. 1 в крайний из свободных буферных регистров блока 8. Элемент 60 задержки необходим для формирования нужной длительности управляющих сигналов.

Блок 2 буферных регистров обращений имеет счетчик 70 разрядностью , где гт7- число буферных регистров в блоке. Перед началом работы счетчик 70 обнулен. При этом нулевой код счетчика разрешает выбор первого выхода дешифратора 68 и формирует на выходе элемента ИЛИ 72 нулевой сигнал Буфер обращений i пуст Сигнал Запись в буфер обращений i на вторбм входе 13 блока 2 разрешает формирование сигнала записи в буферный регистр 67 на первом выходе дешифратора 68 и, проходя через элемент 69 задержки на вход сложения счетчика 70, увеличива ет его содержимое на единицу, подготавливая запись во второй буферный регистр 67 и т.д.

Запись кода обращения в соответствующие буферные регистры производится по их первым информационным входам, подключенным к первым информационным входам 12 блока 2. Вторые информационные входы буферных регистров подключены к выходам предыдущих регистров и образуют цепи сдвига информации. После окончания обработки обращения i-м блоком памяти через третий вход 14 блока 2 сигнал Сдвиг поступает на входы сдвига буферных регистров 67 и на входы вычитания счетчика 70. При этом происх дит перезапись информации с более низшего буферного регистра на более верхний и уменьшение содержимого счетчика 70 на единицу. В случае полного заполнения буфера единичный код счетчика 70 формирует на выходе элемента И-НЕ 71 нулевойсигнал Буфер обращений i заполнен. Единичный сигнал с второго выхода 16 блока , свидетельствующий о наличии обращений к блоку памяти i, поступает на второй вход 29 блока 5 синхронизации и разрешает запуск его формирователя 56 управляющих сигналов. Запуск фОЕЯлирователя 56 осуществляется сигналом с выхода элемента И 55, стробируемым частотой управления на одном из входов схемы. После запуска формирователя 56 сигнал с его выхода блокирует элемент И 55 на время работы блока памяти. Блокировка сигнала запуска формирователя 56 может также осуществляться нулевым сигналом с выхода элемента ИЛИ 54, если обращение к i-му блоку памяти производится со считыванием информации (нулевой сигнал кода операции на первом вхрде 28 блока , а его блок 4 полностью занят(нулевой сигнал Буфер информации заполнен на третьем входе 30 блока 5;I. После выполнения операции считывания с выходов формирователя 56 через первый выход 31 блока 5 на третий вход 14 блока 2/ поступает сигнал Сдвиг, подготавливающий следующее обращение к i-му блоку памяти, и через выход 33 на вход 23 блока 4,- - сигнал Запись, осуществляющий запись считанного из накопителя 3 -j числа в крайний из его свободных регистров считанной информации. Сигналы управления с выходов -формирователя 56 через выходы 32 блока 5j, поступают на входы 20 накопителя 3 .

Принцип действия и структурные схемы блоков 2, 4 и 8 буферных регистров одинаковые, поэтому в дальнейшем их работа описывается кратко. Рассмотрим работу устройства при выдаче считанной информации. В процессе приема и обработки обращений в буферных регистрах блока 8 последовательно в порядке их поступления располагаются адреса блоков памяти обращений со считыванием информации, а в. буферных регистрах блоков, соответствующаялим информация в порядке ее считывания из блоков памяти Код адреса блока памяти, информация из которого должна вьщаваться первой

всегда находится в верхнем буферном регистре блока 8 и с его выхода 53 поступает на упрайлягадие входы 35 коммутатора б, подключая его выход 36 к выходам 25 блока 4 и на входы 41 блока 7 управления. Адрес входов 41 блока 7 поступает на входы его дешифратора 64 и выбирает i-и выход дешифратора. Сигнал i-ro выхода де4 шифратора подается на соответствующий вход элемента И-ИЛИ 63 и первый вход элемента И 65 .Единичный сигнал с выхода 26 блока 4 поступающий на соответствующий вход 42 блока 7, сдвидетельствует о готовности к вьщаче считанной инфО 1ации и формирует на выходе элемента И-ИЛИ 63 сигнал Обращение обслужено, который с выхода 45 вьщается в систему. По этому сигналу из системы на вход 40 блока 7 эыдается сигнал Разрешение выдачи информации, поступакмций на второй вход элемента И 6-5 и элемент 66 задержки. На выходе элемента И 65 формируется сигнал, который через соответствующий выход 48 блока 7 поступает на вход 24 блока 4 и сдвигает в нем информацию. Далее сигнал с выхода элемента 66 задержки через выход 46 поступает на вход 52 блока 8 регистров адресов, осуществляя в нем сдвиг и тем самым подготавливая устройство к выдаче информации по следующему обращению.

Технико-экономическое преимущество предлагаемого устройства заключается в его упрощении и повышении надежности за счет использования буферизации адресов блоков памяти обращений для управления вьадачей информации, и повышении эффективного :быстродействия путем более полной загрузки блоков памяти, достигаемой раздельной буферизацией обращений к блокам памяти и считанной;:из них информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для адресации буферной памяти | 1988 |

|

SU1587517A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для сопряжения | 1980 |

|

SU903853A1 |

ЗАПОМИНАКЯЦЕЕ УСТРОЙСТВО, содержащее блоки памяти, коммутатор, блок управления и регистр, информационные входы которого являются ин- . формационными входами устройства, управляющий вход регистра, является первым управляющим входом устройства, первый и второй выходы регистра подключены соответственно к первому и второму входу блока уйравления, третий и четвертый входы которого являются соответственно вторым и третьим входами устройства, первый и второй выходы блока управления являются соответственно первым и вторым выходами устройства, выходы коммутатора являются информационными выходами устройства, отличающе. вся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит блоки синхронизации, блоки регистров информации, блок буферных регистров и блок регистров адресов, выход которого подключен к пятому входу блока управления и к управляющему входу коммутатора, первый вход блока регистров адресов подклю1чен к первому входу блока управления, третий и четвертый выходы которого под- . ключёны соответственно к второму и третьему входам блока регистров адресов , информационные входы комму1гато- , ра подключены к информационным выходам блоков памяти, информационные входы которых подключены к информационным выходам соответствующих блоков буферных регистров, адресные входы блоков памяти подключены к адресные выходам соответствующих бло- ; ков буферных регистров, первый управляющий выхси которых подключен к первьм входам соответствующих блоков синхронизации, вторые управляющие выходы блоков буферных регистров под-); ключёны к вторым входам соответствующих блоков синхронизации, первые вы(Л ходы которых подключены к первым управляющим входам соответствующих блоков буферных регистров, вторые I управляющие выходысинхронизации подключены к управляющим входам соответствующих блоков памяти, третьи выходы блоков синхронизации подклю чены к первым управляющим входам соответствующих блоков регистров инл со формации, вторые управлягацие входы которых подкл|очены к пятому выходу блока управления, первые управляющие выходы блоков регистров информации подключены к шестому входу блока управления, седьмой вход и шестой выход которого подключены соответственно к третьим управляющим выxoдJuл и BTojxaM управляющим входам блоков буферных регистров, вторые управляюсгшё выходы блоков буферных регистров подключены к третьим входам соответству кцих блоков синхронизации.

30

33

55

32

29 28 .2

1$

31

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Огнев И | |||

| В.,и Шамаев Ю | |||

| М | |||

| Проектирование эапоминагадих устройств | |||

| М., Высшая школа, 1979, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления обменом информации из блоков памяти | 1977 |

|

SU642771A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-01-23—Публикация

1982-10-12—Подача