третьего блоков памяти являются соот ветственно вторым и выходами гфеобразователя кода и подключены к соответствующим входам формирователя информационных разрядов, выход элемента ИЛИ является четвег)тым выходом преобразователя кода и подкл1о .чен к первому управляющему входу блока перераспределения разрядив, второму управляющему входу формирова теля разрядов признака режима и к третьему управляклцему входу формирователя информационных разрядов, вы87ход элемента ИЛИ подключен к входу инвертора, выход которого является пятым вых.одом формирователя кода и подключен к второму управляющему входу блока перераспределения разрядов, к третьему управляющему входу формирователя разрядов признака режима и к четвертому управляющему входу формирователя информационных разрядов, первый вход элемента ИЛИ является вторым входом преобразователя кода, а в то рой вход элемента ИПИ-третьим входом преобразователя кода .

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Преобразователь телевизионного стандарта | 1981 |

|

SU1016850A1 |

| Способ формирования цифрового телевизионного сигнала | 1978 |

|

SU902321A1 |

| Система передачи телевизионного сигнала с помощью дифференциальной импульсно-кодовой модуляции | 1983 |

|

SU1107342A2 |

| ШИФРАТОР | 1989 |

|

RU2033691C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

1. ФОРМИРОВАТЕЛЬ ЦИФРОВОГО ТЕЛЕВИЗИОННОГО СИГНАЛА, содержащий аналого-цифровой преобразователь, вход которого объединен с входами обнаружителя одноэлементных деталей, обнаружителя фронтов и обнаружителя групповых структур и является входом формирователя цифрового телевизионного сигнала, элемент ИЛИ, первый и второй входы которого подключены к выходам соответственно обнаружителя одноэлементных деталей и обнаружителя фронтов, и формирователь разрядов признака режима, выход которого подключен к первому информационному входу коммутатора,- о т л и ч а ю щ и и с я тем, что, с целью повьшения точности формирования цифрового телевизионного сигнала, в него введены преобразователь кода, формирователь информационных разрядов, блок запрета и счетчик импульсов, вход которого является входом сигнала управления, а выходы подключены к управляющим входам коммутатора, второй информационный вход которого соединен с выходом формирователя информационных разрядов, первьш вход преобразователя кода подключен к выходу аналого-цифрового преобразова теля, пять входов - к соответствующим входам формирователя разрядов признака режима и формирователя инт формационных разрядов, информационный вход блока запрета соединен с выходом элемента ИЛИ, управляющий вход объединен с вторым входом преобразователя кода, с первыми управляющими входами формирователя разрядов признака режима и формирователя информационных разрядов и подключен к выходу обнаружителя группо- вьпс структур, а выход подключен к (Л третьему входу преобразователя кода и к второму управляющему входу формирователя информационных разрядов. 2. Фop иpoвaтeль по п. 1, о т личающийся тем, что преоб- разователь кода содержит линию заа держки, входы которой объединены и являются первым входом преобразова00 Jiik теля кода,а выходы подключены к информационным входам блока пере00 распределения разрядов, информацион ч1 ные выходы которого соединены с соответствующими информа1р1онными входами первого, второго и третьего блоков памяти, управляющие входы которых соединены с соответствующими выходами распределителя импульсов, выходы первого блока памяти являются первым выходом преобразователя кода и подключены к соответствую1цим входам формирователя разрядов признака режима и формирователя информационных разрядов, выходы второго и

Изобретение относится к телевизионной технике и может использоваться в вещательном и прикладном телевидении для передачи сигналов в цифровой форме.

Цель изобретения - повышение точности формирования цифрового телевизионного сигнала.

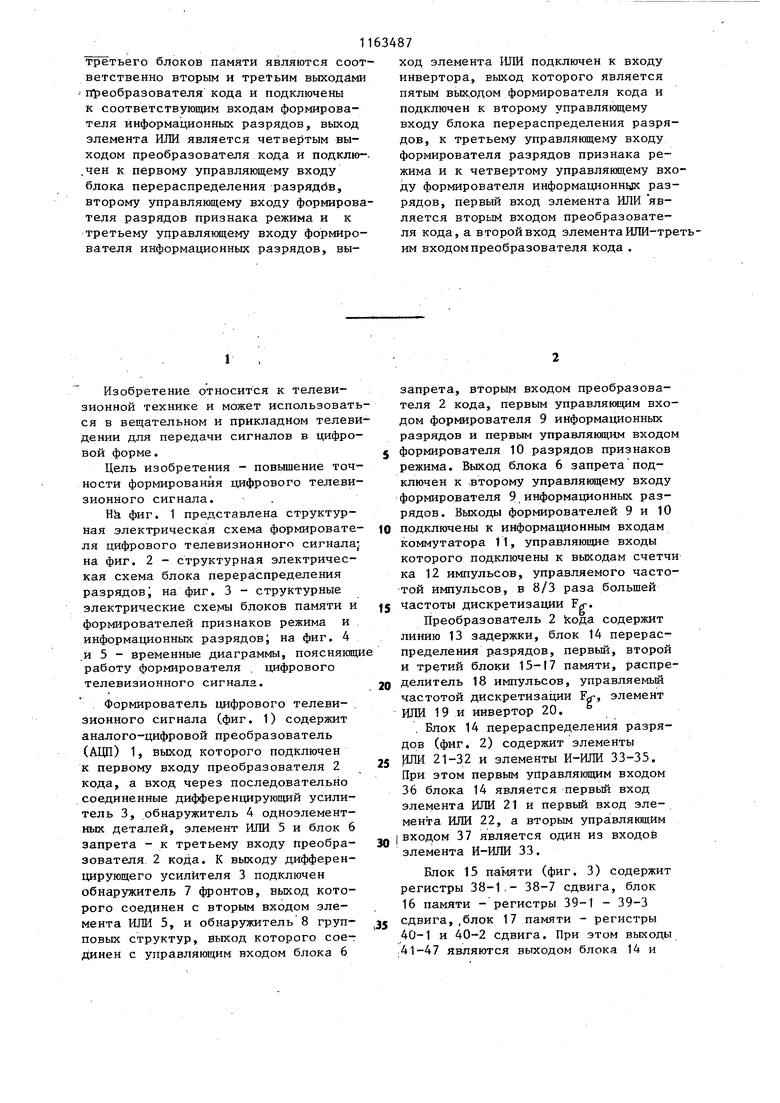

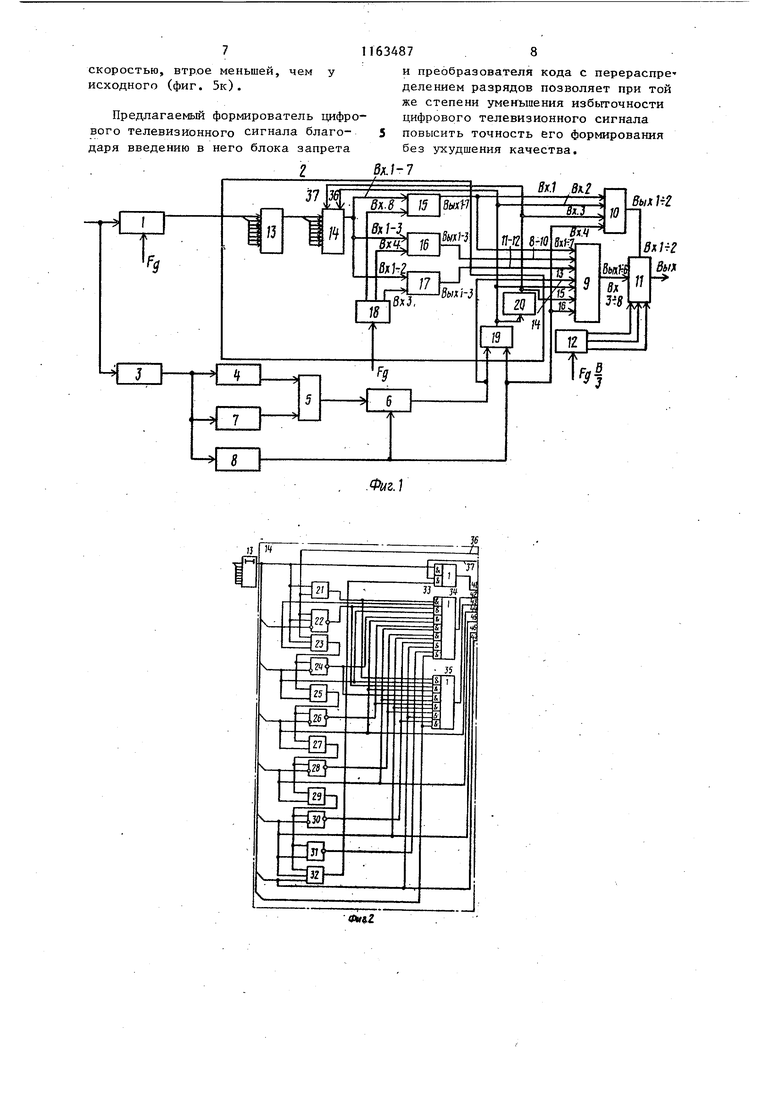

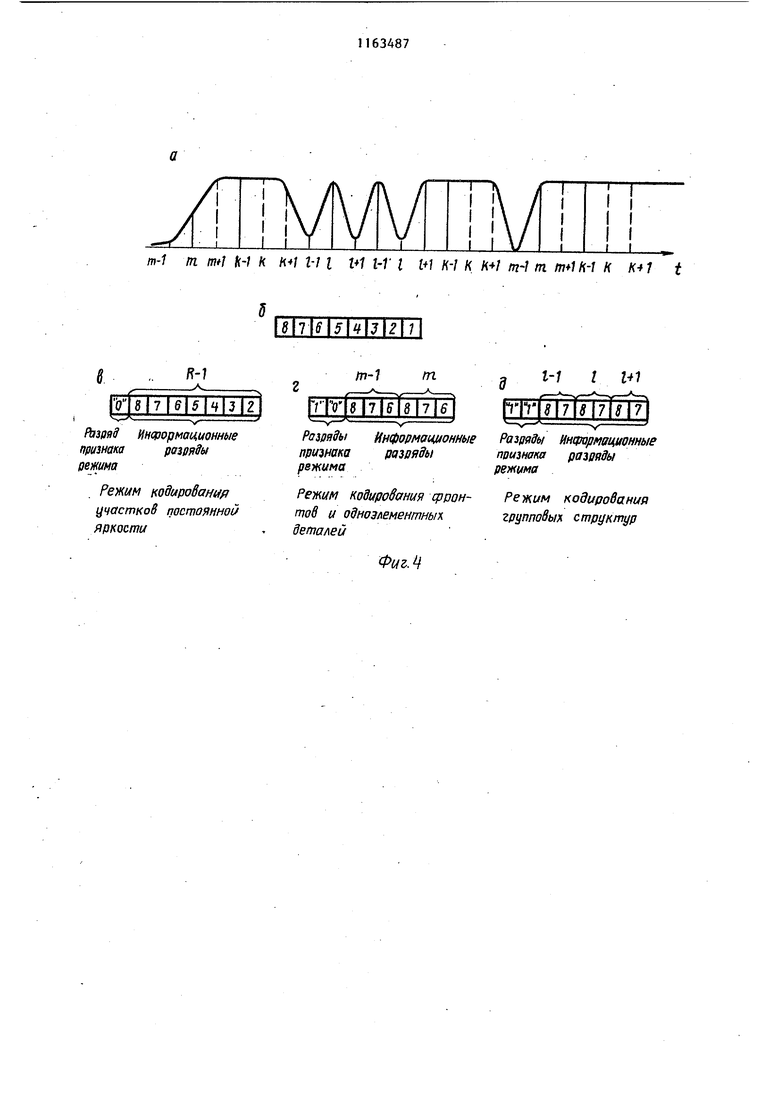

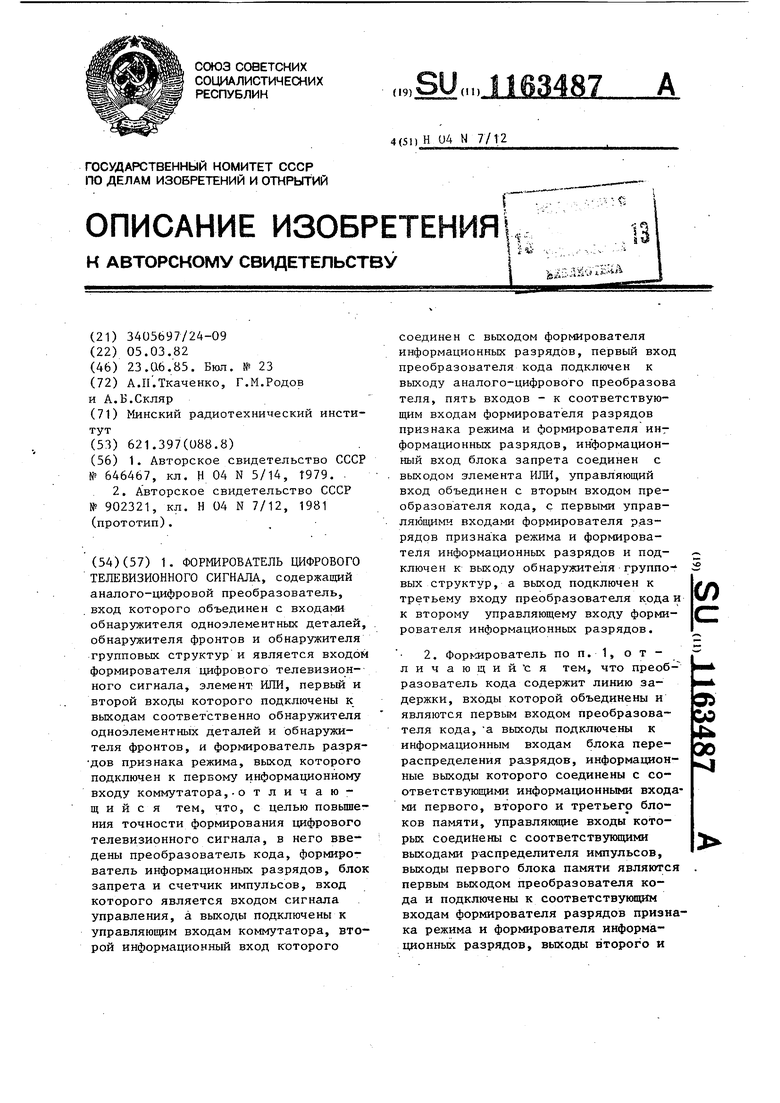

Hk фиг. 1 представлена структурная электрическая схема формирователя цифрового телевизионного сигнала;, на фиг. 2 - структурная электрическая схема блока перераспределения разрядовi на фиг. 3 - структурные электрические схемы блоков памяти и формирователей признаков режима и информационней разрядов; на фиг. 4 и 5 - временные диаграммы, пояснякяци работу формирователя . цифрового телевизионного сигнала.

Формирователь цифрового телевизионного сигнала (фиг. 1) содержит аналого-цифровой преобразователь (АЩ1) 1, выход которого подключен к первому входу преобразователя 2 кода, а вход через последовательно соединенные дифференцирующий усилитель 3, обнаружитель 4 одноэлементных деталей, элемент ИЛИ 5 и блок 6 запрета - к третьему входу преобразователя. 2 кода. К выходу дифференцирующего усилителя 3 подключен обнаружитель 7 фронтов, выход которого соединен с вторым входом элемента ИЛИ 5, и обнаружитель 8 групповых структур, выход которого сое-г динен с управляющим входом блока 6

запрета, вторым входом преобразователя 2 кода, первым управля1«дим входом формирователя 9 информационных разрядов и первым управлякщим входо формирователя 10 разрядов признаков режима. Выход блока 6 запрета подключен к второму управляняцему входу формирователя 9 информационных разрядов. Выходы формирователей 9 и Ю подключены к информационным входам коммутатора 11, управляющие входы которого подключены к выходам счетч ка 12 импульсов, управляемого частотой импульсов, в 8/3 раза большей Частоты дискретизации Fg-.

Преобразователь 2 1кода содержит линию 13 задержки, блок 14 перераспределения разрядов, первый, второй и третий блоки 15-17 памяти, распределитель 18 импульсов, управляемый частотой дискретизации , элемент ИЛИ 19 и инвертор 20.

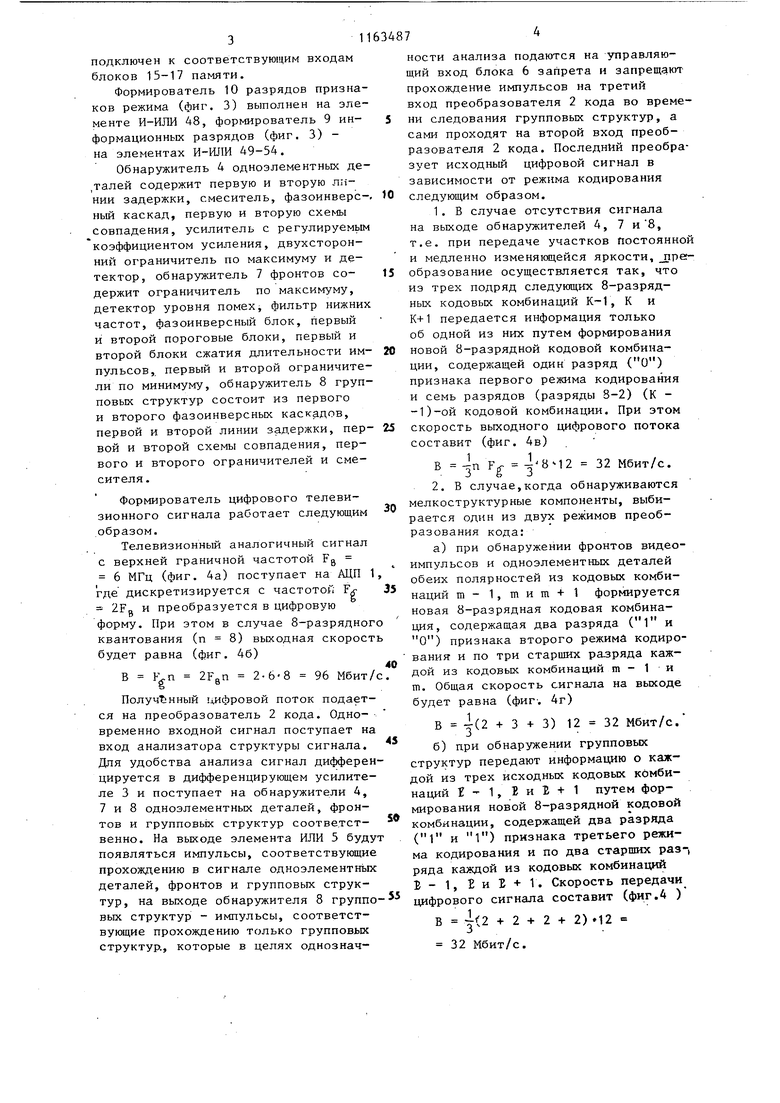

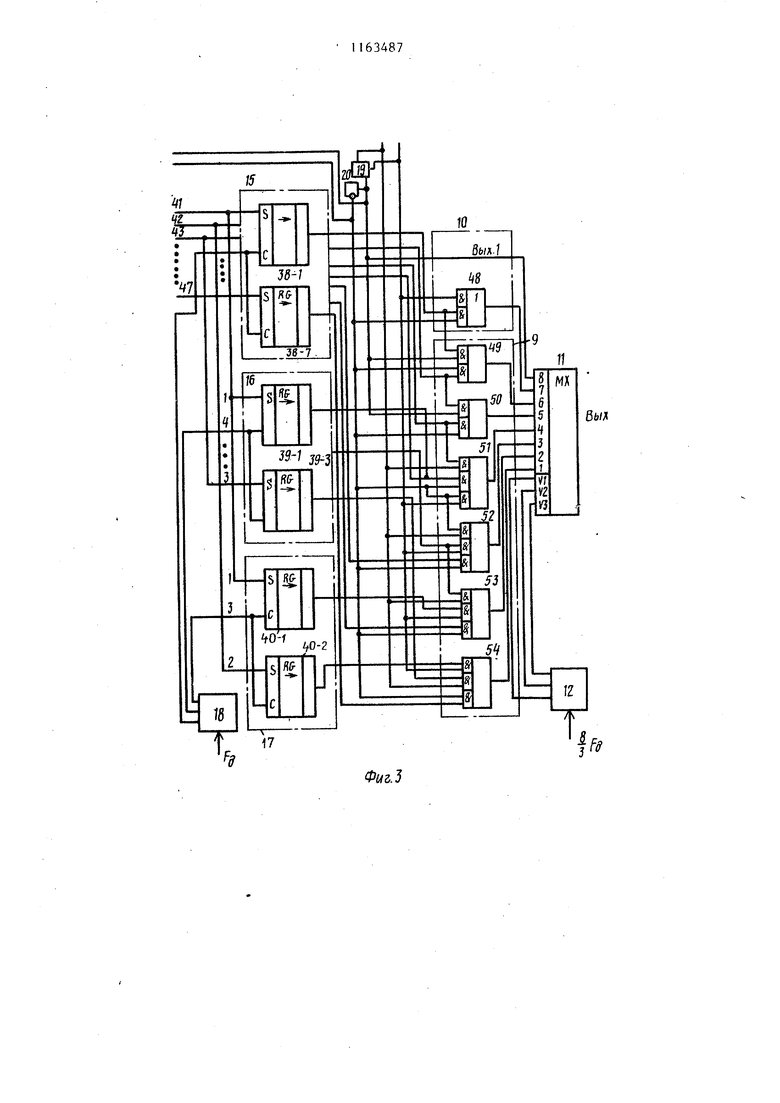

. Блок 14 перераспределения разрядов (фиг. 2) содержит элементы ЩЖ 21-32 и элементы И-ИЛИ 33-35. При этом первым управляющим входом 36 блока 14 является первый вход элемента ИЛИ 21 и первый вход элемента ИЛИ 22, а вторым управляющим I входом 37 является один из входоб элемента И-ИЛИ 33.

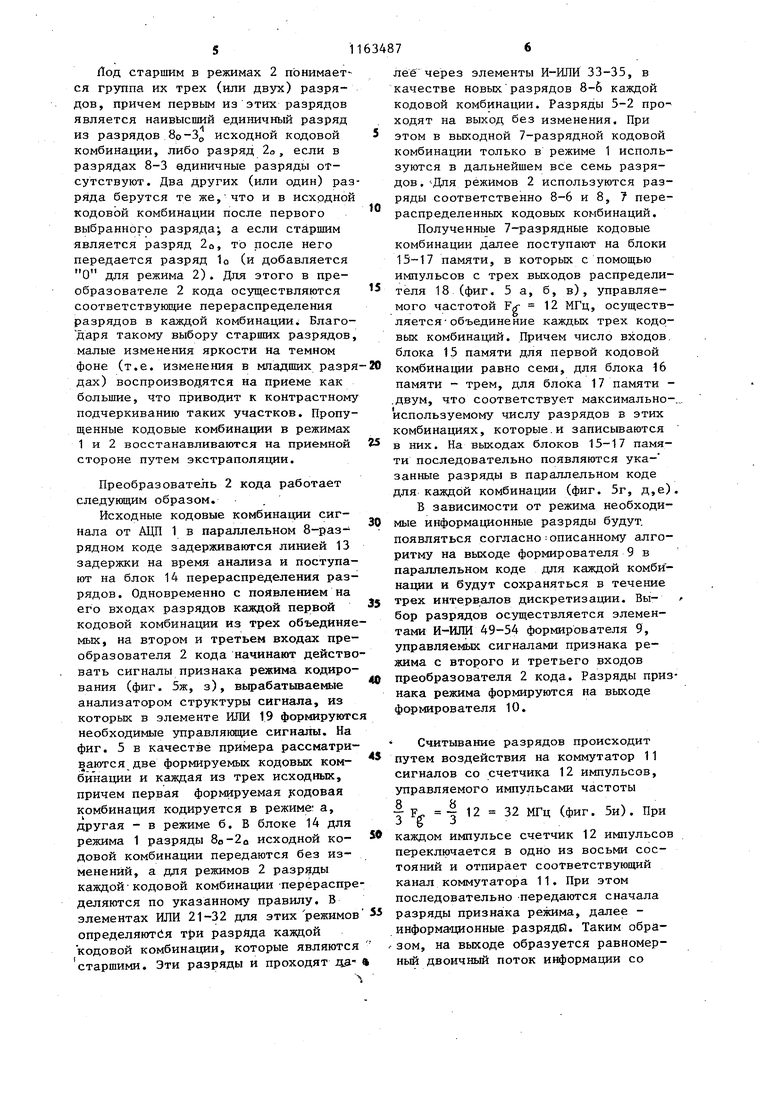

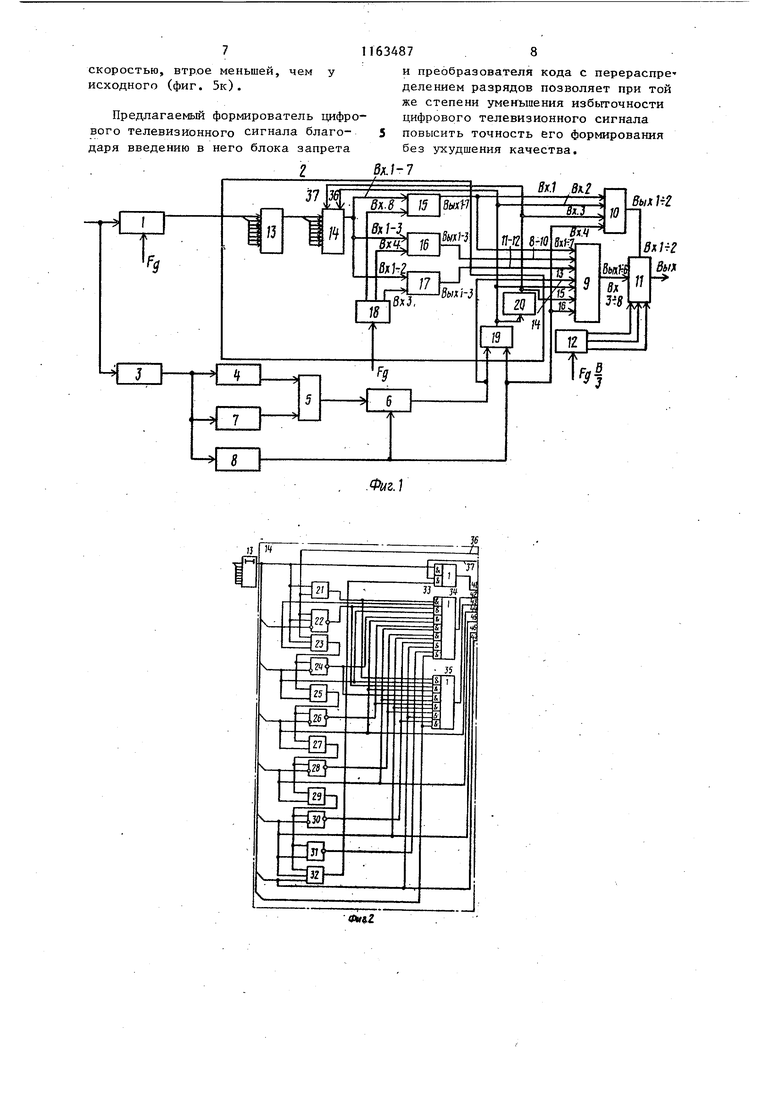

Блок 15 памяти (фиг. 3) содержит регистры 38-1.- 38-7 сдвига, блок 16 памяти - регистры 39-1 - 39-3 сдвига,,блок 17 памяти - регистры 40-1 и 40-2 сдвига. При этом выходы 41-47 являются выходом блока 14 и подключен к соответствующим входам блоков 15-17 памяти. Формирователь 10 разрядов призна ков режима (фиг. 3) выполнен на эле менте И-ИЛИ 48, формирователь 9 информационных разрядов (фиг. 3) на элементах И-Ш1И 49-54. Обнаружитель 4 одноэлементных де далей содержит первую и вторую линии задержки, смеситель, фазоинверсный каскад, первую и вторую схемы совпадения, усилитель с регулируемь1м коэффициентом усиления, двухсторонний ограничитель по максимуму и детектор, обнаружитель 7 фронтов содержит ограничитель по максимуму, детектор уровня помех фильтр нижних частот, фазоинверсный блок, первый и второй пороговые блоки, первый и второй блоки сжатия длительности импульсов, первый и второй ограничите ли по минимуму, обнаружитель 8 груп повых структур состоит из первого и второго фазоинверсных каскадов, первой и второй линии задержки, пер вой и второй схемы совпадения, первого и второго ограничителей и смесителя. Формирователь цифрового телевизионного сигнала работает следующим образом. Телевизионный аналогичный сигнал с верхней граничной частотой Fg 6 МГц (фиг. 4а) поступает на АЦП где дискретизируется с частотой F 2F,, и преобразуется в цифровую форму. При этом в случае 8-разрядно квантования (п В) выходная скорост будет равна (фиг. 46) В ZFgO 2-б-8 96 Мбит Полученный цифровой поток подается на преобразователь 2 кода. Одновременно входной сигнал поступает на вход анализатора структуры сигнала. Для удобства анализа сигнал дифферен цируется в дифференцирующем усилителе 3 и поступает на обнаружители 4, 7 и 8 одноэлементных деталей, фронтов и rpynnoBbix структур соответственно. На выходе элемента ИЛИ 5 буду появляться импульсы, соответствующие прохождению в сигнале одноэлементньк деталей, фронтов и групповых структур, на выходе обнаружителя 8 группе вых структур - импульсы, соответствующие прохождению только групповых структур., которые в целях однозначности анализа подаются на управляющий вход блока 6 запрета и запрещают прохождение импульсов на третий вход преобразователя 2 кода во времени следования групповых структур, а сами проходят на второй вход преобразователя 2 кода. Последний преобразует исходный цифровой сигнал в зависимости от режима кодирования следующим образом. 1 . В случае отсутствия сигнала на выходе обнаружителей 4, 7 и8, т.е. при передаче участков постоянной и медленно изменякяцейся яркости, jjpe;образование осуществляется так, что из трех подряд следующих 8-разрядных кодовых комбинаций К-Г, К и К+1 передается информация только об одной из них путем формирования новой 8-разрядной кодовой комбинации, содержащей один разряд (О) признака первого режима кодирования и семь разрядов (разряды 8-2) (К -1)-ой кодовой комбинации. При этом скорость выходного цифрового потока составит (фиг. 4в) В -jn Fg- 842 32 Мбит/с. 2. В случае,когда обнаруживаются мелкоструктурные компоненты, выбирается один из двух режимов преобразования кода: а)при обнаружении фронтов видеоимпульсов и одноэлементных деталей обеих полярностей из кодовых комбинаций m - 1, m и m + 1 формируется новая 8-разрядная кодовая комбинация, содержащая два разряда (1 и О) признака второго режимй кодирования и по три старших разряда каждой из кодовых комбинаций m - 1 и т. Общая скорость сигнала на выходе будет равна (фиг-. 4г) В (2 +3+3) 12 32 Мбит/с. б)при обнаружении групповых труктур передают информацию о кажой из трех исходных кодовых комбинаций X - 1, Б и Ь + 1 путем формирования новой 8-разрядной кодовой комбинации, содержащей два разряда (1 и 1) признака третьего реткима кодирования и по два старших раз-, ряда каждой из кодовых комбинаций 1 - 1, и Б + 1. Скорость передачи цифрового сигнала составит (фиг.А ) В (2 + 2+2 + 2) «12 32 Мбит/с. Лод старшим в режимах 2 понимается группа их трех (или двух) разрядов, причем первым из этих разрядов является наивысший единичный разряд из разрядов вр-Зр исходной кодовой комбинации, либо разряд 2о, если в разрядах 8-3 единичные разряды отсутствуют. Два других (или один) раз ряда берутся те же,что и в исхрдной кодовой комбинации после первого выбранного разряда-, а если старшим является разряд 2о, то после него передается разряд 1о (и добавляется О для режима 2). Для этого в преобразователе 2 кода осуществляются соответствующие перераспределения разрядов в каждой комбинации; Благодаря такому выбору старших разрядов малые изменения яркости на темном фоне (т.е. изменения в младших разря дах) воспроизводятся на приеме как большие, что приводит к контрастному подчеркиванию таких участков. Пропущенные кодовые комбинации в режимах 1 и 2 восстанавливаются на приемной стороне путем экстраполяции. Преобразователь 2 кода работает следующим образом. Исходные кодовые комбинации сигнала от АЦП 1 в параллельном 8-разрядном коде задерживаются линией 13 задержки на время анализа и поступают на блок 14 перераспределения разрядов . Одновременно с появлением на его входах разрядов каждой первой кодовой комбинации из трех объединяе мых, на втором и третьем входах преобразователя 2 кода начинают действо вать сигналы признака режима кодирования (фиг. 5ж, з), вырабатываемые анализатором структуры сигнала, из которых в элементе ИЛИ 19 формируютс необходимые управлякнцие сигналы. На фиг. 5 в качестве примера рассматриваются две формируемых кодовых комбинации и каждая из трех исходных, причем первая формируемая содовая комбинация кодируется в режиме: а, другая - в режиме б. В блоке 14 для режима 1 разряды 8о-2а исходной кодовой комбинации передаются без изменений, а для режимов 2 разряды каждойкодовой комбинации перераспре деляются по указанному правилу. В элементах ИЛИ 21-32 для этих режимов определяются три разряда каждой кодовой комбинации, которые являются старшими. Эти разряды и проходят д.алее через элементы И-Ш1И 33-35, в качестве новыхразрядов 8-6 каждой кодовой комбинации. Разряды 5-2 про ходят на выход без изменения. При этом в выходной 7-разрядной кодовой комбинации только в режиме 1 используются в дальнейшем все семь разрядов. Для режимов 2 используются разряды соответственно 8-6 и 8, 7 перераспределенных кодовых комбинаций. Полученные 7-разрядные кодовые комбинации далее поступают на блоки 15-17 памяти, в которьк с помощью импульсов с трех выходов распределителя 18 (фиг. 5 а, б, в), управляемого частотой Frf- 12 МГц, осуществляется- объединение каждых трех кодовых комбинаций. Причем число входов, блока 15 памяти для первой кодовой комбинации равно семи, для блока 16 памяти - трем, для блока 17 памяти .двум, что соответствует максимально-.,, используемому числу разрядов в этих комбинациях, которые.и записьгеаются в них. На выходах блоков 15-17 памяти последовательно появляются укаванные разряды в параллельном коде для каждой комбинации (фиг. 5г, д,е). В зависимости от режима необходимые информационные разряды будут, появляться согласноописанному алгоритму на выходе формирователя 9 в параллельном коде для каждой комбинации и будут сохраняться в течение трех интервалов дискретизации. Вы- бор разрядов осуществляется элементами И-ИШ 49-54 формирователя 9, управляемых сигналами признака режима с второго и третьего входов преобразователя 2 кода. Разряды признака режима формируются на выходе формирователя 10. Считывание разрядов происходит путем воздействия на коммутатор 11 сигналов со счетчика 12 импульсов, управляемого импульсами частоты | Fg. I 12 32 МГц (фиг. 5и). При каждом импульсе счетчик 12 импульсов переклнэчается в одно из восьми состояний и отпирает соответствующий канал коммутатора 11. При этом последовательно передаются сначала разряды признака режима, далее информаодаонные разряди. Таким образом, на выходе образуется равномерный двоичньй поток информации со скоростью, втр.ое меньшей, чем исходного (фиг. 5к). Предлагаемьй формирователь цифро вого телевизионного сигнала благодаря введению в него блока запрета

5Х/-7 1634878 и преобразователя кода с перераспре делением разрядов позволяет при той же степени уменьшения избыточности цифрового телевизионного сигнала повысить точность его формирования 5 без ухудшения качества.

ti

g ,: , I0f8i7|g|5i |3|2 I Ч-Л.-1 .V /Ъз/ Информационнб/е признака разоя9ы оежима Режим кодирована (участков постоянной яркости

Фиг.Ц РазояЗы Ниформаи 4онные признака разоядь режима Режим кодиробсгния срронтов и одноэлементные еталей I 1-И РагддЗы Информационные пдизнака развяды ре}кима Режим иодироВаHUP групповых структур

ж .t

пппппп

м m г

Фиг,.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для формирования цифрового телевизионного сигнала | 1977 |

|

SU646467A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ формирования цифрового телевизионного сигнала | 1978 |

|

SU902321A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-06-23—Публикация

1982-03-05—Подача