Изобретение относится к микроэлектронике и импульсной технике и предназначено для использования в качестве электронного коммутатора и универсального логического модуля.

Известен восьмиканальный мультиплексор, содержащий три элемента НЕ, четыре элемента 2-2ИЛИ-4И-НЕ и элемент ,

Недостатком мультиплексора являются ограниченные функциональные возможности.

Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является универсальный логический модуль, который при выполняет функции тридцатидвух- канального мультиплексора и содержит пять элементов НЕ и тридцать один блок разложения, каждый из которых состоит из двух элементов И и одного элемента ИЛИ (реализует функцию 2-2И-2ИЛИ) 2.

Недостатком известного мультиплексора является высокая конструктивная сложность.

«Цель изобретения - упрощение конструкции мультиплексора.

Цель достигается тем, что в мультиплексор, содержащий пять элементов НЕ, вход

1-го из которых (, 2 5) соединен с 1-й

адресной шиной мультиплексора, введены восемь элементов 4-2И-5ИЛИ-НЕ, элемент 2-ЗИЛИ-2И, четыре элемента ЗИЛИ-НЕ и четыре элемента 2ИЛИ-НЕ, первый вход первого из которых соединен с выходом первого элемента НЕ и первым входом второго элемента 2ИЛИ-НЕ, второй вход которого соединен с входом второго элемента НЕ, выход которого соединен с вторым входом первого элемента 2ИЛИ-НЕ и первым входом третьего элемента 2ИЛИ-НЕ, второй вход которого соединен с входом первого элемента НЕ и первым входом четвертого элемента 2ИЛИ-НЕ, второй вход которого соединен с входом второго элемента НЕ, выход k-ro элемента 2ИЛИ-НЕ (, 2, 3, 4) соединен с k-м входом j-ro элемента 4-2И5ИЛИ-НЕ fJ-1,28), (k+4)-u вход которого

соединен с (4j+k-4)-u информационной шиной мультиплексора, третья адресная шина которого соединена с девятым входом (2kСЛ

С

VI

4 Ь. Ч)

1}-го элемента 4-2И-5ИЛИ-НЕ, выход которого соединен с первым входом k-ro элемен- та ЗИЛИ-НЕ, второй вход которого соединен с выходом 2k-ro элемента 4-2И- 5ИЛ И-НЕ, девятый вход которого соединен с выходом третьего элемента НЕ, четвертая адресная шина мультиплексора соединена с третьим входом(2т-1)-го элемента ЗИЛИ- НЕ (, 2), выход которого соединен с т-м входом элемента 2-ЗИЛИ-2И, (т+2)-й вход которого соединен с выходом 2m-ro элемента ЗИЛИ-НЕ, третий вход которого соединен с выходом четвертого элемента НЕ, пятая адресная шина мультиплексора соединена с пятым входом элемента 2-ЗИЛИ- 2И, шестой вход которого соединен с выходом пятого элемента НЕ, а выход соединен с выходной шиной мультиплексора, причем элемент НЕ содержит два МОП- транзистора, затвор первого из которых соединен с входной шиной элемента, первая шина питания которого соединена с истоком первого транзистора, сток которого соединен с выходной шиной элемента и истоком второго транзистора, сток которого соединен с затвором и второй шиной питания, элемент 2ИЛИ-НЕ содержит три МОП- транзистора, затвор m-ro (, 2) из которых соединен с m-й входной шиной элемента, первая шина питания крторого соединена с истоком m-ro транзистора, сток которого соединен с выходной шиной элемента и истоком третьего транзистора, сток которого соединен с затвором и второй шиной питания, элемент ЗИЛИ-НЕ содержит четыре МОП-транзистора, затвор v-ro из которых (, 2, 3) соединен с v-й входной шиной элемента, первая шина питания которого соединена с истоком v-ro транзистора, сток которого соединен с выходной шиной элемента и истоком четвертого транзистора, сток которого соединен с затвором и второй шиной питания, элемент 4-2И- 5ИЛИ-НЕ содержит десять МОП-транзисторов, затвор j-ro из которых (, 28)

соединен с J-й входной шиной элемента, первая шина питания которого соединена с истоком (k+4}-ro транзистора (, 2, 3, 4) и истоком девятого транзистора, затвор которого соединен с девятой входной шиной элемента, а сток соединен со стоком k-ro транзистора, выходной шиной элемента и истоком десятого транзистора, сток которого соединен с затвором и второй шиной питания элемента, исток k-ro транзистора соединен со стоком (k+4}-ro транзистора, элемент 2-ЗИЛИ-2И содержит семь МОП- транзисторов, затвор р-го из которых (, 26) соединен с р-й входной шиной элемента, первая шина питания которого соединена с истоком седьмого транзистора, сток которого соединен с затвором, выходной шиной элемента и истоком (2г-1)-го транзистора (, 2, 3), сток которого соединен с истоком 2г-го транзистора, сток которого соединен с второй шиной питания элемента.

Мультиплексор содержит восемь элементов 4-2И-5ИЛИ-НЕ, четыре элемента

0 2ИЛИ-НЕ, четыре элемента ЗИЛИ-НЕ, элемент 2-ЗИЛИ-2И и пять элементов НЕ, вход

1-го из которых (, 25) соединен с 1-й

адресной шиной мультиплексора. Первый вход первого элемента 2ИЛИ-НЕ соеднен с

5 эыходом первого элемента НЕ и первым входом второго элемента 2ИЛИ-НЕ. Второй вход второго элемента 2ИЛИ-НЕ соединен с входом второго элемента НЕ , выход которого соединен с вторым входом первого эле0 мента 2ИЛИ-НЕ и первым входом третьего элемента 2ИЛИ-НЕ, второй вход которого соединен с входом первого элемента НЕ и первым входом четвертого элемента 2ИЛИ- НЕ, второй вход которого соединен с вхо5 дом второго элемента НЕ. Выход k-ro элемента 2ИЛИ-НЕ (, 2, 3, 4) соединен с k-м входом j-ro элемента 4-2И-5ИЛИ-НЕ

(, 28), (k+4)-H вход которого соединен

с (4j+k-4)-tf информационной шиной мульти0 плексора. Третья адресная шина мультиплексора соединена с девятым входом (2k-1)-ro элемента 4-2И-5ИЛИ-НЕ, выход которого соединен с первым входом k-ro элемента ЗИЛИ-НЕ, Второй вход k-ro эле5 мента ЗИЛИ-НЕ соединен с выходом 2k-ro элемента 4-2И-5ИЛИ-НЕ, девятый вход которого соединен с выходом третьего элемента НЕ. Четвертая адресная шина мультиплексора соединена с третьим вхо0 дом (2т-1)-го элемента ЗИЛИ-НЕ (, 2), выход которого соединен с m-м входом элемента 2-ЗИЛИ-2И, (гтИ-2)-й вход которого соединен с выходом 2m-ro элемента ЗИЛИ- НЕ, третий вход которого соединен с выхо5 дом четвертого элемента НЕ, Пятая адресная шина мультиплексора соединена с пятым входом элемента 2-ЗИЛИ-2И, шестой вход которого соединен с выходом пятого элемента НЕ, а выход соединен с

0 выходной шиной мультиплексора.

На фиг. 1 представлена функциональная схема мультиплексора, на фиг. 2, 3, 4, 5 и 6 - принципиальные схемы на МОП-транзисторах элементов НЕ, 2ИЛИ-НЕ, ЗИЛИ5 НЕ, 4-2И-5ИЛИ-НЕ и 2-ЗИЛИ-2И соответственно.

Мультиплексор содержит восемь элементов 4-2И-5ИЛИ-НЕ 1...8, четыре элемента 2ИЛИ-НЕ 9,..12, четыре элемента ЗИЛИ-НЕ 13...16, элемент 2-ЗИЛИ-2И 17 и

пять элементов НЕ 18...22, пять адресных шин 23...27, тридцать две информационные шины 28...59, выходную шину 60.

Отметим, что элемент 4-2И-5ИЛИ-НЕ реализует логическую функцию

f ai as v 32 ае v аз a v 34 ав v ag, где at - значение сигнала на t-м входе элемента, 29).

Элемент 2-ЗИЛИ-2И реализует логическую функцию

g(bi v Ьз v bsXb2 v ЬА v be), где br - значение сигнала на r-м входе элемента. 26).

Элемент НЕ (фиг. 2) выполнен на одном переключательном 61 и одном нагрузочном 62 МОП-транзисторах, включенных между шинакм питания 63 и 64 Вход 65 элемента соединен с затвором транзистора 61, а выход 66 элемента - со стоком транзистора 61 (истоком транзистора 62).

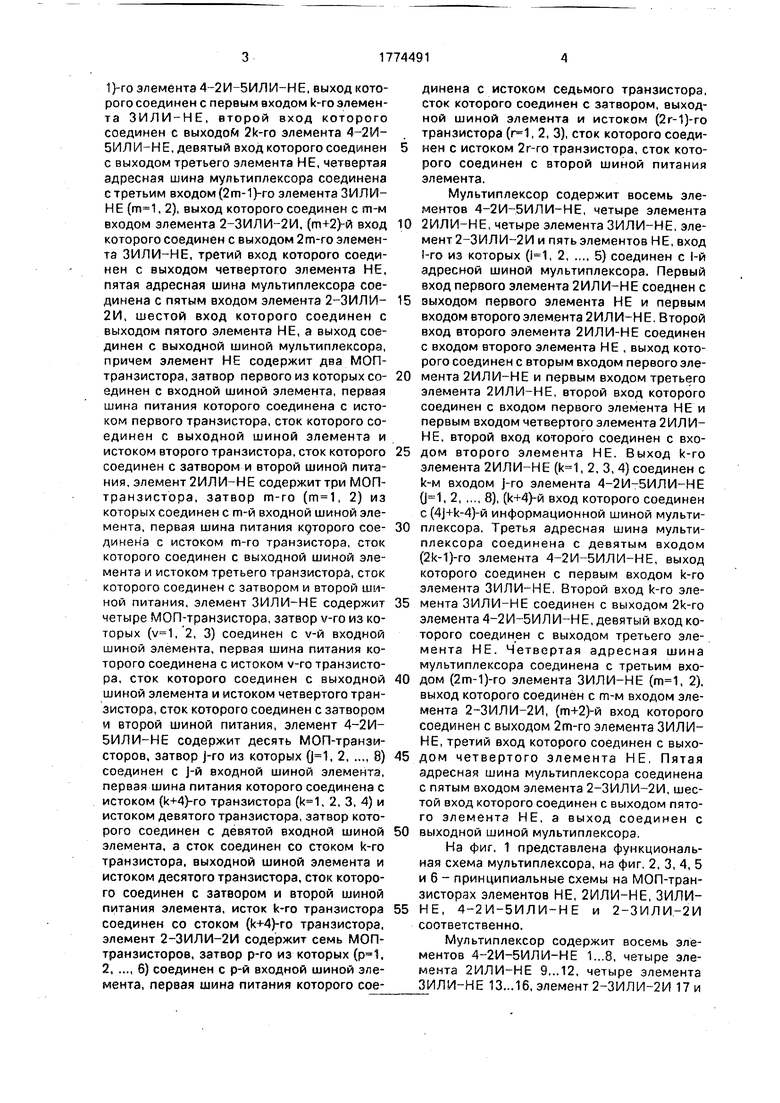

Элемент 2ИЛИ-НЕ (фиг. 3) выполнен на двух переключательных 67 и 68 и одном нагрузочном 69 МОП-транзисторах, включенных между шинами питания 70 и 71. Вхо- ды 72 и 73 элемента соединены соответственно с затворами транзисторов 67 и 68, а выход 74 элемента - со стоками транзисторов 67 и 68 (истоком транзистора 69).

Элемент ЗИЛИ-НЕ (фиг. 4) выполнен на трех переключательных 75, 76 и 77 и одном нагрузочном 78 МОП-транзисторах, включенных между шинами питания 79 и 80. Входы 81, 82 и 83 элемента соединены соответственно с затворами транзисторов 75,76 и 77, в выход 84 элемента - со стоками транзисторов 75, 76 и 77 (истоком транзистора 78).

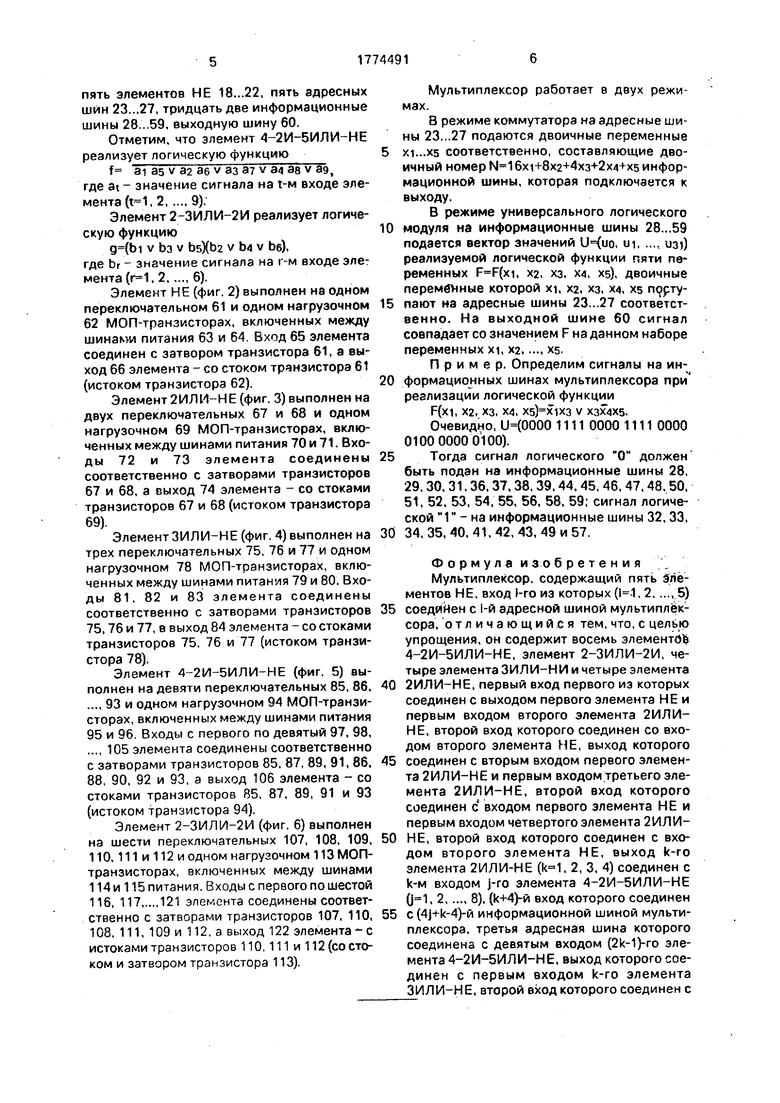

Элемент 4-2И-5ИЛИ-НЕ (фиг. 5) выполнен на девяти переключательных 85, 86, ..., 93 и одном нагрузочном 94 МОП-транзисторах, включенных между шинами питания 95 и 96. Входы с первого по девятый 97, 98, ..., 105 элемента соединены соответственно с затворами транзисторов 85, 87, 89, 91, 86, 88, 90, 92 и 93, а выход 106 элемента - со стоками транзисторов 85, 87, 89, 91 и 93 (истоком транзистора 94).

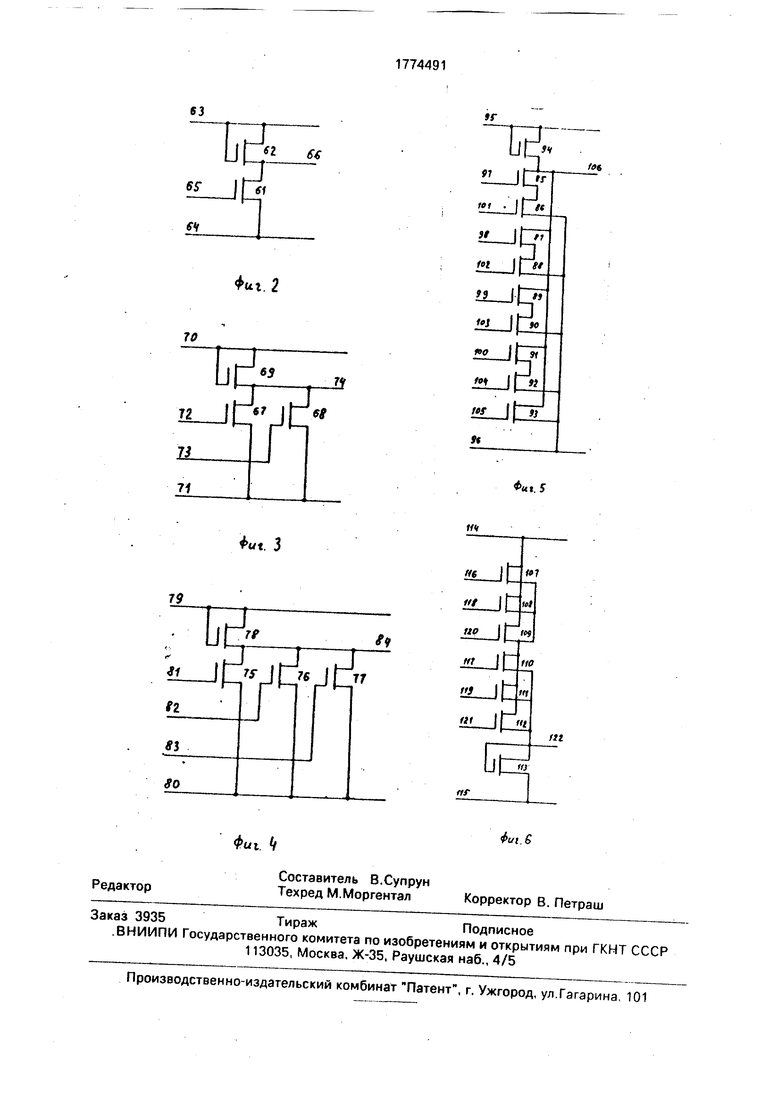

Элемент 2-ЗИЛИ-2И (фиг. 6) выполнен на шести переключательных 107, 108, 109, 110,111и112и одном нагрузочном 113 МОП- транзисторах, включенных между шинами 114 и 115 питания. Входы с первого по шестой 116, 117121 элемента соединены соответственно с затворами транзисторов 107, 110, 108, 111, 109 и 112, а выход 122 элемента - с истоками транзисторов 110,111 и 112 (со стоком и затвором транзистора 113).

Мультиплексор работает в двух режимах.

В режиме коммутатора на адресные шины 23...27 подаются двоичные переменные

XL..XS соответственно, составляющие двоичный номер N 16xi+8х2+4хз+2Х4+Х5 информационной шины, которая подключается к выходу.

В режиме универсального логического

модуля на информационные шины 28...59

подается вектор значений U(uo, uiuai)

реализуемой логической функции пяти переменных (xi, Х2, хз, Х4, xs), двоичные переменные которой xi, ха, хз, x/i, xs поступают на адресные шины 23...27 соответственно. На выходной шине 60 сигнал совпадает со значением F на данном наборе

переменных xi, X2xs.

Пример. Определим сигналы на информационных шинах мультиплексора при реализации логической функции

F(X1, Х2г ХЗ, Х4, Х5)Х1ХЗ V ХЗХ4Х5.

Очевидно, 1НОООО 1111 0000 1111 0000 010000000100).

Тогда сигнал логического О должен быть подан на информационные шины 28, 29.30, 31,36,37.38, 39,44. 45, 46, 47,48,50, 51, 52, 53, 54, 55, 56, 58, 59; сигнал логической 1 - на информационные шины 32,33,

34, 35, 40, 41,42, 43, 49 и 57.

Ф о р м у л а и з о б р е т е н и я Мультиплексор, содержащий пять Элементов НЕ, вход 1-го из которых (, 25)

соединен с 1-й адресной шиной мультиплексора, отличающийся тем, что, с целью упрощения, он содержит восемь элементов 4-2И-5ИЛИ-НЕ, элемент 2-ЗИЛИ-2И, четыре элемента ЗИЛИ-НИ и четыре элемента

2ИЛИ-НЕ. первый вход первого из которых соединен с выходом первого элемента НЕ и первым входом второго элемента 2ИЛИ- НЕ, второй вход которого соединен со входом второго элемента НЕ, выход которого

соединен с вторым входом первого элемента 2ИЛИ-НЕ и первым входом третьего элемента 2ИЛИ-НЕ, второй вход которого соединен с4 входом первого элемента НЕ и первым входом четвертого элемента 2ИЛИНЕ, второй вход которого соединен с входом второго элемента НЕ, выход к-го элемента 2ИЛИ-НЕ (, 2, 3, 4) соединен с к-м входом j-ro элемента 4-2И-5ИЛИ-НЕ (, 28), (к+4)-й вход которого соединен

с (4j+k-4)-n информационной шиной мультиплексора, третья адресная шина которого соединена с девятым входом (2к-1)-го элемента 4-2И-5ИЛИ-НЕ. выход которого соединен с первым входом k-го элемента ЗИЛИ-НЕ, второй вход которого соединен с

выходом 2k-ro элемента 4-2И-5ИЛИ-НЬ, девятый вход которого соединен с выходом третьего элемента НЕ, четвертая адресная шина мультиплексора соединена с третьим входом (2т-1)-го элемента ЗИЛИ-НЕ (, 2), выход которого соединен с m-м входом элемента 2-ЗИЛИ-2И, (т+2)-й вход которого соединен с выходом 2пгт-го элемента ЗИЛИ-НЕ, третий вход которого соединен с выходом четвертого элемента НЕ, пятая адресная шина мультиплексора соединена с пятым входом элемента 2-ЗИЛИ-2И, шестой вход которого соединен с выходом пятого элемента НЕ, а выход соединен с выходной шиной мультиплексора, причем элемент НЕ содержит два МОП-транзистора, затвор первого из которых соединен с входной шиной элемента, первая шина питания которого соединена с истоком первого транзистора, сток которого соединен с выходной шиной элемента и истоком второго транзистора, сток которого соединен с затвором и второй шиной питания, элемент 2ИЛИ-НЕ содержит три МОП-транзистора, затвор м-го (, 2) из которых соединен с м-й входной шиной элемента, первая шина питания которого соединена с истоком м-го транзистора, сток которого соединен с выходной шиной элемента и истоком третьего транзистора, сток которого соединен с затвором и второй шиной питания, элемент ЗИЛИ-НЕ содержит четыре МОП-транзистора, затвор у-го из которых (, 2, 3) соединен с у-й входной шиной элемента, первая шина питания которого соединена с истоком у-го транзистора, сток которого соединен с выходной шиной элемента и истоком четвертого транзистора, сток которого соединен с затвором и второй шиной питания, элемент 4-2И-5ИЛИ-НЕ содержит десять МОП-транзисторов, затвор j-ro из которых

, 28) соединен с J-й входной шиной

элемента, первая шина питания которого соединена с истоком (k+4)-ro транзистора (, 2, 3, 4) транзистора и истоком девятого транзистора, затвор которого соединен с

девятой входной шиной элемента, а сток соединен со стоком k-ro транзистора, выходной шиной элемента и истоком десятого транзистора, сток которого соединен с затвором и второй шиной питания элемента, исток k-ro транзистора соединен со сто- ком (k+4)-ro транзистора, элемент 2-ЗИЛИ-2И содержит семь МОП-транзисторов, затвор р-го из которых (, 2

6) соединен с р-й входной шиной элемента,

первая шина питания которого соединена с истоком седьмого транзистора, сток которого соединен с затвором, выходной шиной элемента и истоком (2г-1)-го транзистора (, 2, 3), сток которого соединен с истоком 2г-го транзистора, сток которого соединен с второй шиной питания элемента.

-J -ч л. Jb

(О

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексор | 1990 |

|

SU1780185A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ | 1991 |

|

SU1811002A1 |

| Многовходовый логический модуль | 1990 |

|

SU1793547A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 32-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2023 |

|

RU2800768C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ВОССТАНОВЛЕНИЯ МОДИФИЦИРОВАННОГО КОДА ХЕММИНГА ДЛЯ 16-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 2024 |

|

RU2824472C1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2021 |

|

RU2762061C1 |

Изобретение относится к микроэлектронике и импульсной технике и предназначено для использования в качестве электронного коммутатора и универсального логического модуля. Сущность изобретения: мультиплексор содержит восемь элементов 4-2И-5ИЛИ-НЕ, восемь элементов ИЛИ-НЕ, элемент 2-ЗИЛИ-2И, пять элементов НЕ, пять.адресных шин, тридцать две информационные шины и выходную шину. Для реализации мультиплексора требуется 125 МОП-транзисторов, 6 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мультиплексор | 1988 |

|

SU1538248A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Универсальный логический модуль | 1983 |

|

SU1119003A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-11-07—Публикация

1990-09-27—Подача