которых подключены соответственно к третьему и четвертому входам блок входы задания режимов четырех счетчиков подключены соответственно к первой, второй, третьей и четвертой группам выходов дешифратора, вход которого и управляющие входы первого и второго коммутаторов объедин ны и подключены к второму входу бло формирования управляющего слова, выходы четырех счетчиков подключены к соответствующим информационным входам второго коммутатора, первый вход блока подключен к информационному входу первого коммутатора, выход которого объединен с выходом втЬрого коммутатора и подключен к выходу блока формирования управляющего слова.

2.Устройство по п. 1, о т л ич а ющее с я тем, что блок задания числа циклов содержит дешифратор , два счетчика и сумматор, выход которого подключен к первому выходу блока и к информационным входам первого и второго счетчиков, выходы старщих разрядов которых объединены и подключены к второму выходу блока а входы задания режимов - к первой

и второй группам выходов дешифратора, вход которого и вход задания режимов сумматора подключены к первому входу блока, входы первого и второго операндов сумматора соединены соответственно с информационными входами устройства,

3.Устройство по п. 1, о т л ичающееся тем, что блок формирования адреса содержит три коммутатора, два регистра адреса, триггер, три элемента ИЛИ, два злемента И и элемент НЕ, причем управляющие входы первого и второго коммутаторов объединены и подключены

к второму входу блока, первый и третий входы которого соответственно подключены к первому и второму информационным входам первого коммутатора, третий и четвертый информационные входы первого коммутатора объет динены и подключены к выходу второго коммутатора, выходы младших двух разрядов второго коммутатора подключены к первым входам первого и второго элементов ИЛИ, выходы которых подключены к входам младших разрядов третьего входа первого коммутатора, младший разряд четвертого входа первого коммутатора соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с выходом младшего разряда второго коммутатора, выход первого коммутатора является выходом блока, третий коммутатор управляющим входом соединен с первым входом первого элемента И и подключен к прямому выходу триггера , первый и второй информационные входы второго коммутатора подключен соответственно к выходам первого ивторого регистров адреса, информационные входы которых объединены и подключены к четвертому входу блока, синхровходы регистров адреса подключены соответственно к выходам первого и второго элементов И, вторые входы которых соединены с входом элемента НЕ и подключены к шестому входу блока, выход элемента НЕ соединен с входом триггера, инверсный выход которого подключен к первому входу второго элемента И, вторые входы первого и второго элементов ИЛИ соединены с соответствукицими информационными входами третьего коммутатора и подключены к пятому входу блока, выход третьего коммутатора соединен с вторым входом третьего элемента 1И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU959078A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство микропрограммного управления | 1985 |

|

SU1293730A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

1. МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок формирования адреса, память микрокоманд, выход микрокоманды которой подключен к информационному входу регистра микрокоманд, отличающееся тем, что, с целью повышения быстродействия, оно содержит блок формирования управляющего слова, блок задания числа циклов, регистр управляющего слова,, регистр возврата и регистр команд, выход кода операции которого подключен к первому входу блока формирования адреса, а адресный выход - к первому входу блока формирования управляющего слова, второй и третий входы которого подключены соответственно к выходу первого управляющего поля регистра микрокоманд и первому выходу блока задания числа циклов, nepBbtii и второй входы которого подключены соответственно к первому синхровходу устройства и выходу второго управляющего поля регистра микрокоманд, выходы третьего управляющего поля и адреса возврата которого подключены соответственно к второму входу блока формирования адреса и информационному входу регистра возврата, синхровход которого соединен с вторым синхровходом устройства, выход регистра возврата подключен к третьему входу блока формирования адреса, четвертый и пятый входы и выход которого соединены соответственно -с адресным выходом памяти микрокоманд, вторым выходом блока задания числа циклов и с адресным входом памяти микро.команд, третий синхровход устройства соединен с шестым входом блока формирования адреса и синхровходом регистра микрокоманд, выход признака окончания микропрограммы которого ю подключен к первому управляющему выходу устройства, вход команды устройства соединен с входом регистго ра команды, первый синхровход уст00 00 ройства соединен с четвертым входом блока формирования управляющего слова, выход которого и выход операционного поля регистра микрокоманд объединены и подключены к информационному входу регистра управляющего слова, синхровход и выход которого соединены соответственно с четвертым синхровходом устройства и вторьм управляющим выходом устройства, причем блок формирования управляющего слова содержит два коммутатора, дешифратор и четыре счетчика, информационные и синхровходы

Г :

Изобретение относится к вычислительной технике и может быть использовано в ассоциативных процессорах, позволяющих осуществлять параллельную обработка больших массивов данных.

Цель изобретения - повьш1ение быстродействия.

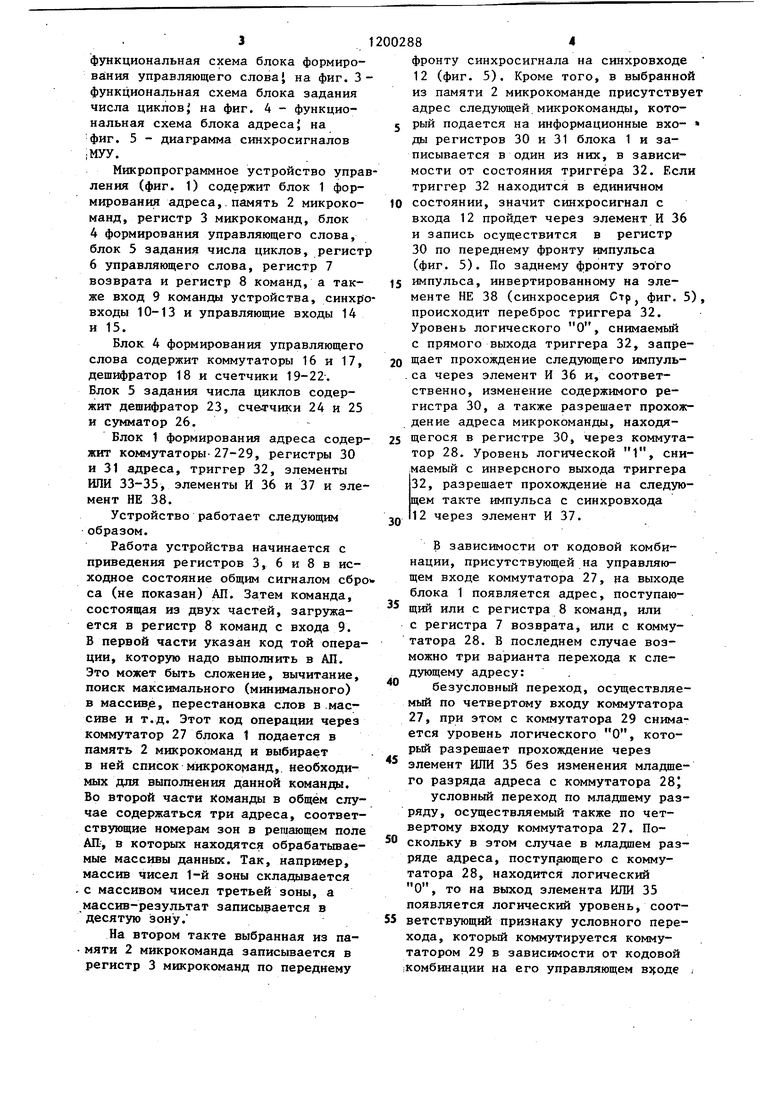

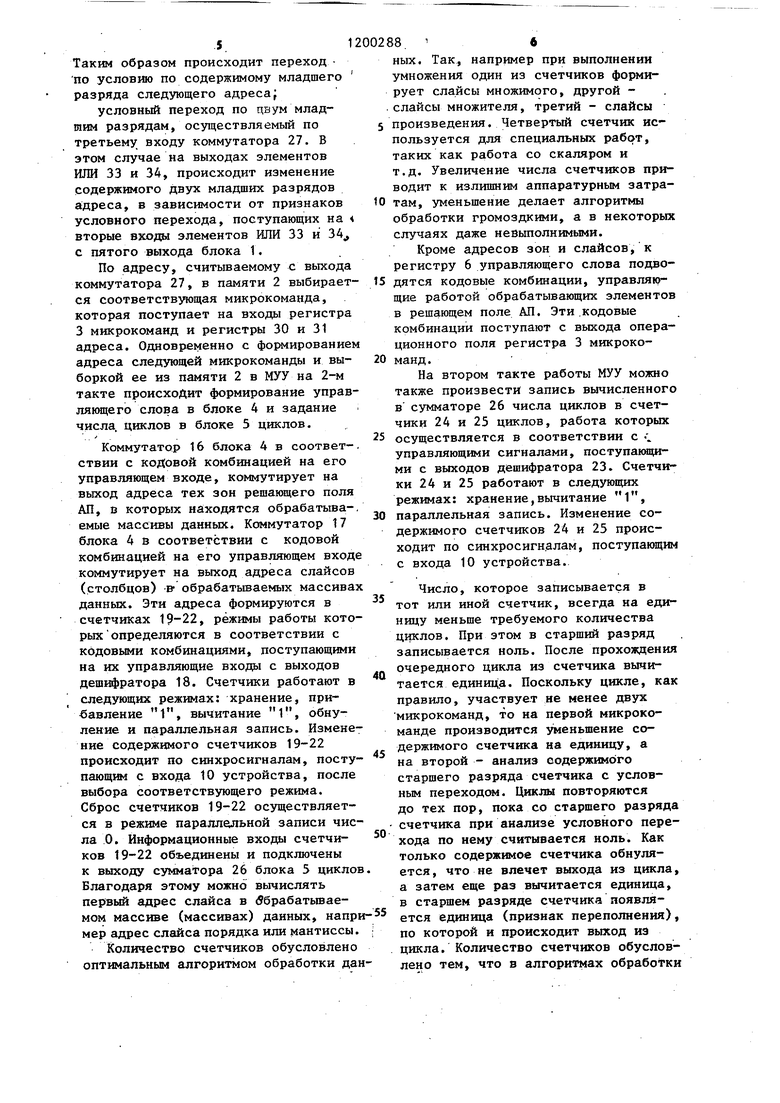

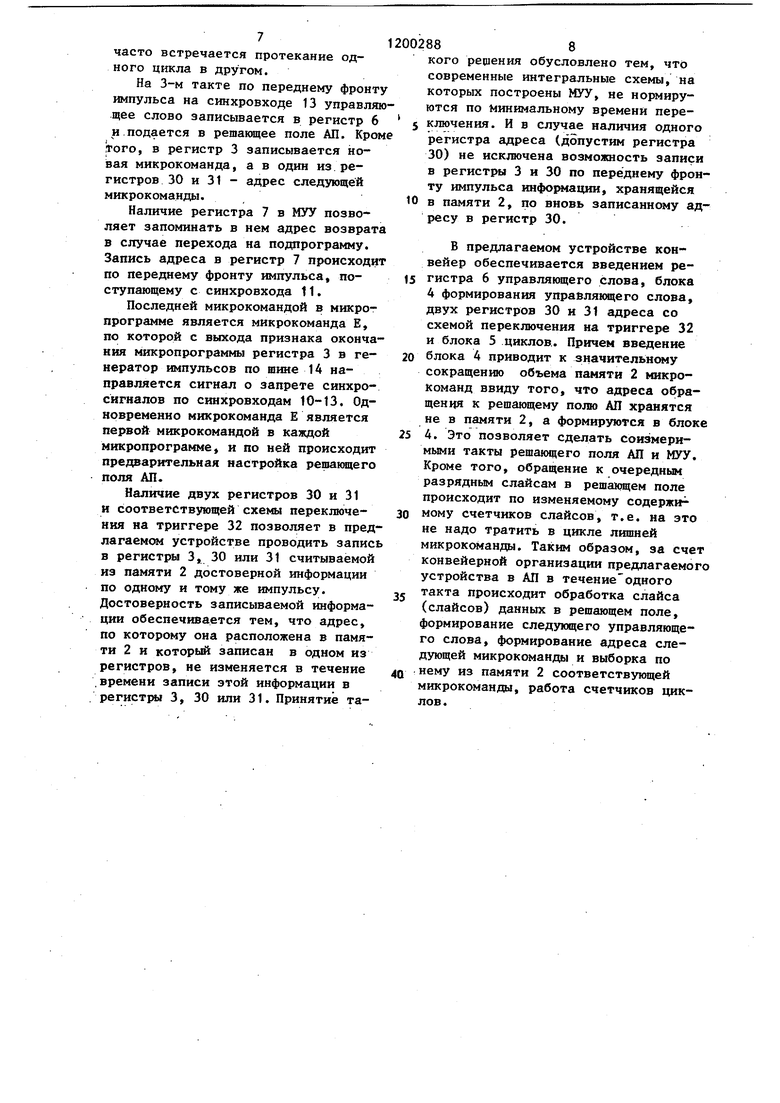

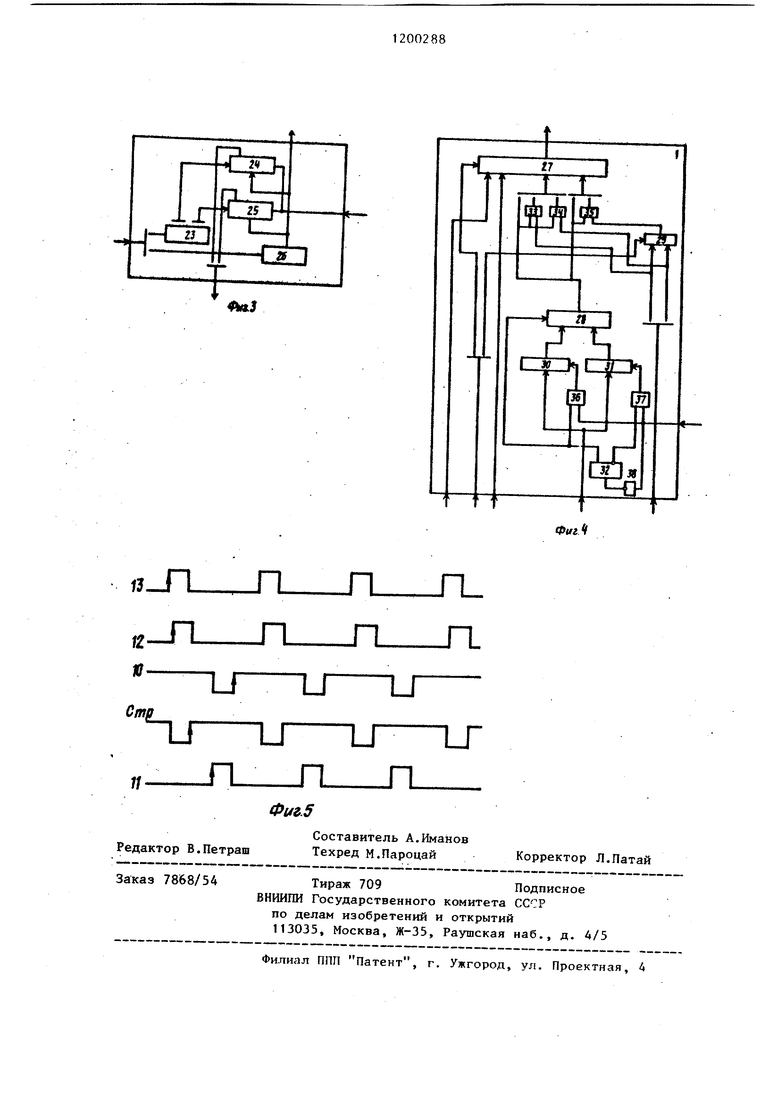

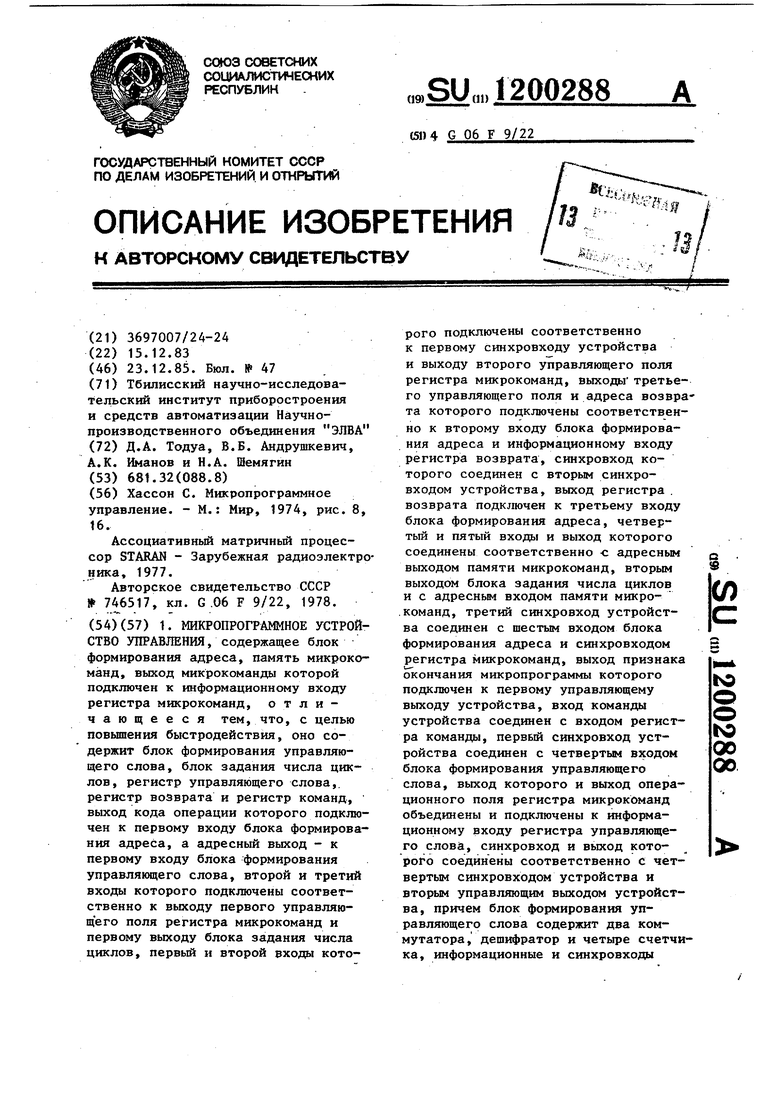

На фиг. 1 показана блок-схема предлагаемого микропрограммного устройства управления (МУУ)J на фиг. 231

функциональная схема блока формирования управляющего словаJ на фиг. 3функциональная схема блока задания числа цикловJ на фиг. 4 - функциональная схема блока адреса} на фиг. 5 - диаграмма синхросигналов

МУУ.

Микропрограммное устройство управ ления (фиг. 1) содержит блок 1 формирования адреса,.память 2 микрокоманд, регистр 3 микрокоманд, блок 4 формирования управляющего слова, блок 5 задания числа циклов, регистр 6 управляющего слова, регистр 7 возврата и регистр 8 команд, а также вход 9 команды устройства, синхрО входы 10-13 и управляющие входы 14 и 15.

Блок 4 формирования управляющего слова содержит коммутаторы 16 и 17, дешифратор 18 и счетчики 19-22. Блок 5 задания числа циклов содержит дешифратор 23, счел-чики 24 и 25 и сумматор 26.

Блок 1 формирования адреса содержит коммутаторы27-29, регистры 30 и 31 адреса, триггер 32, элементы ИЛИ 33-35, элементы И 36 и 37 и элемент НЕ 38.

Устройство работает следующим

образом.

Работа устройства начинается с приведения регистров 3, 6 и 8 в исходное состояние общим сигналом сбро са (не показан) АЛ. Затем команда, состоящая из двух частей, загружается в регистр 8 команд с входа 9. В первой части указан код той операции, которую надо вьшолнить в АЛ. Это может быть сложение, вычитание, поиск максимального (минш ального) в массиву, перестановка слов в .массиве и т.д. Этот код операции через коммутатор 27 блока 1 подается в память 2 микрокоманд и выбирает в ней список микрокоманд, необходиых для выполнения данной команды. о второй части команды в общем случае содержаться три адреса, соответствующие номерам зон в решающем поле И, в которых находятся обрабатываеые массивы данных. Так, например, ассив чисел 1-й зоны складывается с массивом чисел третьей зоны, а ассив-результат записывается в десятую зону.

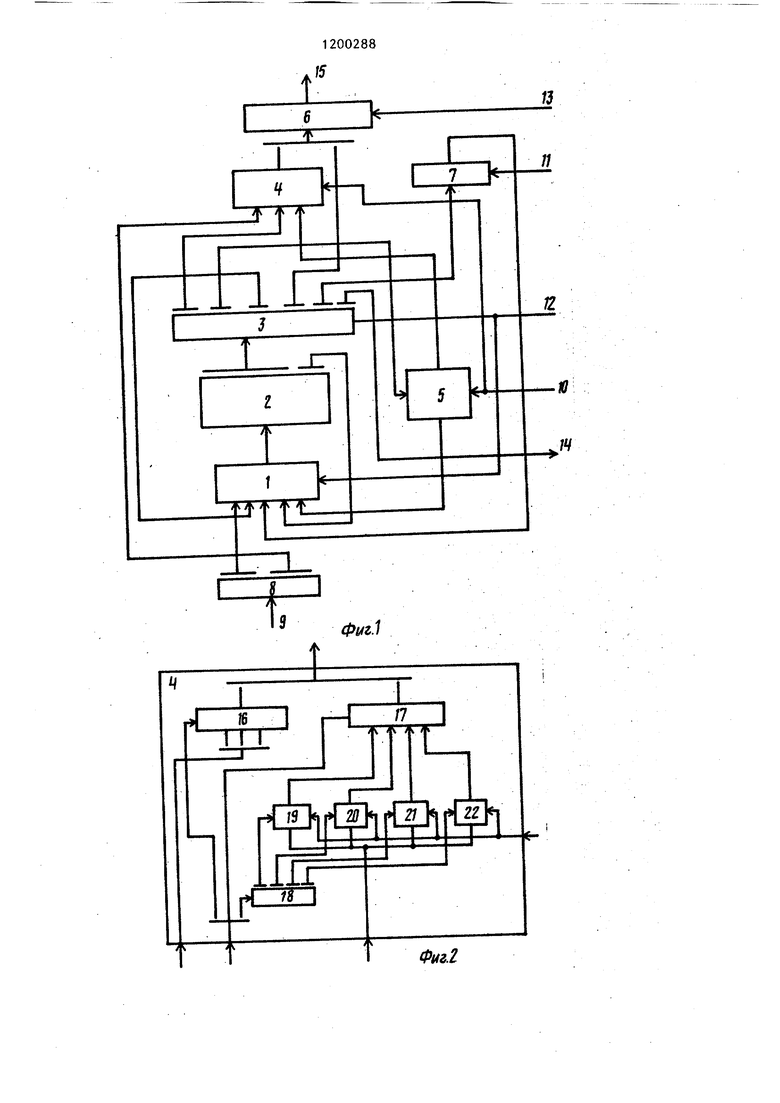

На втором такте выбранная из памяти 2 микрокоманда записывается в регистр 3 микрокоманд по переднему

00288

фронту синхросигнала на синхровходе 12 (фиг. 5). Кроме того, в выбранной из памяти 2 микрокоманде присутствует адрес следующей микрокоманды, который подается на информационные вхо- ды регистров 30 и 31 блока 1 и записывается в один из них, в зависимости от состояния триггера 32. Если триггер 32 находится в единичном

10 состоянии, значит синхросигнал с входа 12 пройдет через элемент И 36 и запись осуществится в регистр 30 по переднему фронту импульса (фиг. 5). По заднему фронту этого

5 импульса, инвертированному на элементе НЕ 38 (синхросерия Стр фиг. 5), происходит переброс триггера 32. Уровень логического О, снимаемый с прямого выхода триггера 32, запрещает прохождение следующего импуль.са через элемент И 36 и, соответственно, изменение содержимого регистра 30, а также разрешает прохождение адреса микрокоманды, находящегося в регистре 30, через коммутатор 28. Уровень логической 1, снимаемый с инверсного выхода триггера 32, разрешает прохождение на следующем такте импульса с синхровхода

jjj 12 через элемент И 37.

В зависимости от кодовой комбинации, присутствующей на управляющем входе коммутатора 27, на выходе блока 1 появляется адрес, поступающий или с регистра 8 команд, или с регистра 7 возврата, или с коммутатора 28. В последнем случае возможно три варианта перехода к следующему адресу:

безусловньй переход, осуществляемый по четвертому входу коммутатора 27, при этом с коммутатора 29 снимается уровень логического О, которьй разрешает прохождение через

элемент ИЛИ 35 без изменения младшего разряда адреса с коммутатора 28J

условный переход по младшему разряду, осуществляемый также по четвертому входу коммутатора 27. Ло50 скольку в этом случае в младшем разряде адреса, поступ.ающего с коммутатора 28, находится логический О, то на выход элемента ИЛИ 35 появляется логический уровень, соответствующий признаку условного перехода, который коммутируется коммутатором 29 в зависимости от кодовой ;КОмбинации на его управляющем взводе , Таким образом происходит переход по условию по содержимому младшего разряда следующего адреса; условный переход по двум младшим разрядам, осуществляемый по третьему входу коммутатора 27. В этом случае на выходах элементов ИЛИ 33 и 34, происходит изменение содержимого двух младших разрядов адреса, в зависимости от признаков условного перехода, поступающих на вторые входы элементов ИЛИ 33 и 34 с пятого выхода блока 1. По адресу, считываемому с выхода коммутатора 27, в памяти 2 выбирается соответствующая микрокоманда, которая поступает на входы регистра 3 микрокоманд и регистры 30 и 31 адреса. Одновременно с формированием адреса следующей микрокоманды и выборкой ее из памяти 2 в МУУ на 2-м такте происходит формирование управляющего слова в блоке 4 и задание числа, циклов в блоке 5 циклов. Коммутатор 16 блока 4 в соответствии с кодовой комбинацией на его управляющем входе, коммутирует на выход адреса тех зон решающего поля АЛ, в которых на ходятся обрабатываемые массивы данных. Коммутатор 17 блока 4 в соответствии с кодовой комбинацией на его управляющем входе коммутирует на выход адреса слайсов (столбцов) в- обрабатьшаемых массивах данных. Эти адреса формируются в счетчиках 19-22, режимы работы которых определяются в соответствии с кодовыми комбинациями, поступающими на их управляющие входы с выходов дешифратора 18. Счетчики работают в следующих режимах: хранение, прибавление 1, вычитание 1, обнуление и параллельная запись. Изменение содержимого счетчиков 19-22 происходит по синхросигналам, поступающим с входа 10 устройства, после выбора соответствующего режима. Сброс счетчиков 19-22 осуществляется в режиме параял ьной записи числа 0. Информационные входы счетчиков 19-22 объединены и подключены к выходу сумматора 26 блока 5 циклов Благодаря этому можно вычислять первый адрес слайса в брабатываемом массиве (массивах) данных, напри мер адрес слайса порядка или мантиссы. Количество счетчиков обусловлено оптимальным алгоритмом обработки дан 1 8. Так, например при выполнении ных умножения один из счетчиков формирует слайсы множимого, другой слайсы множителя, третий - слайсы произведения. Четвертый счетчик используется для специальных работ, таких как работа со скаляром и т.д. Увеличение числа счетчиков приводит к излишним аппаратурным затратам, уменьшение делает алгоритмы обработки громоздкими, а в некоторых случаях даже невыполнимыми. Кроме адресов зон и слайсов, к регистру 6 управляющего слова подводятся кодовые комбинации, управляющие работой обрабатывающих элементов в решающем поле АЛ. Эти .кодовые комбинации поступают с выхода операционного поля регистра 3 микрокоманд. На втором такте работы МУУ можно также произвести запись вычисленного в сумматоре 26 числа циклов в счетчики 24 и 25 циклов, работа которых осуществляется в соответствии с , управляющими сигналами, поступающими с выходов дешифратора 23. Счетчюки 24 и 25 работают в следующих режимах: хранение,вычитание 1, параллельная запись. Изменение содержимого счетчиков 24 и 25 происходит по синхросигн.алам, поступающим с входа 10 устройства. Число, которое записывается в тот или иной счетчик, всегда на единицу меньше требуемого количества циклов. При этом в старший разряд записывается ноль. После прохождения очередного цикла из счетчика вычитается единица. Поскольку цикле, как правило, участвует не менее двух микрокоманд, то на первой микрокоманде производится уменьшение содержимого счетчика на единицу, а на второй - анализ содержимого старшего разряда счетчика с условным переходом. Циклы повторяются до тех пор, пока со старшего разряда счетчика при анализе условного перехода по нему считывается ноль. Как только содержимое счетчика обнуляется , что не влечет выхода из цикла, а затем еще раз вычитается единица, в старшем разряде счетчика появля я единица (признак переполнения), по которой и происходит выход из цикла. Количество счетчиков обусловлено тем, что в алгоритмах обработки часто встречается протекание одного цикла в другом. На 3-м такте по переднему фронт импульса на синхровходе 13 управляю щее слово записывается в регистр 6 и подается в решакяцее поле АЛ. Кром того, в регистр 3 записывается новая микрокоманда, а в один из регистров 30 и 31 - адрес следующей микрокоманды. Наличие регистра 7 в МУУ позволяет запоминать в нем адрес возврат в случае перехода на подпрограмму. Запись адреса в регистр 7 происходи по переднему фронту импульса, поступающему с синхровхода 11. Последней микрокомандой в микропрограмме является микрокоманда Е, по которой с выхода признака оконча ния микропрограммы регистра 3 в генератор импульсов по шине 1А направляется сигнал о запрете синхросигналов по синхровходам 10-13. Одновременно микрокоманда Е является первой микрокомандой в каждой микропрограмме, и по ней происходит предварительная настройка решаницего поля АЛ. Наличие двух регистров 30 и 31 и соответствующей схемы переключения на триггере 32 позволяет в пред лагаемом устройстве проводить запис в регистры 3, 30 или 31 считываемой из памяти 2 достоверной информации по одному и тому же импульсу. Достоверность записываемой информации обеспечивается тем, что адрес, по которому она расположена в памяти 2 и который записан в одном из регистров, не изменяется в течение времени записи этой информации в регистры 3, 30 или 31. Принятие та888кого решения обусловлено тем, что современные интегральные схемы, на которых построены МУУ, не нормируются по минимальному времени переключения. И в случае наличия одного регистра адреса (допустим регистра 30) не исключена возможность записи в регистры 3 и 30 по переднему фроиту импульса инфо тации, хранящейся в памяти 2, по виовь записанному адресу в регистр 30. В предлагаемом устройстве конвейер обеспечивается введением регистра 6 управляющего слова, блока 4 формирования управляющего слова, двух регистров 30 и 31 адреса со схемой переключения на триггере 32 и блока 5 циклов.. Причем введение блока 4 приводит к значительному сокращению объема памяти 2 микрокоманд ввиду того, что адреса обращения к решающему полю АЛ хранятся не в памяти 2, а формируются в блоке 4. Это позволяет сделать соизмеримыми такты решающего поля АП и МУУ. Кроме того, обращение к очередным разрядным слайсам в решающем поле происходит по изменяемому содержимому счетчиков слайсов, т.е. на это не надо тратить в цикле лишней микрокоманды. Таким образом, за счет конвейерной организации предлагаемого устройства в АП в течениеодного такта происходит обработка слайса (слайсов) данных в решающем поле, формирование следзпощего управляющего слова, формирование адреса следующей микрокоманды и выборка по нему из памяти 2 соответствующей микрокоманды, работа счетчиков циклов.

1

1200288

| Хассон С | |||

| Микропрограммное управление | |||

| - М.: Мир, 1974, рис | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Ассоциативньй матричный процессор STARAN - Зарубежная радиоэлектроника, 1977 | |||

| Микропрограммное устройство управления | 1978 |

|

SU746517A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-23—Публикация

1983-12-15—Подача