2. Преобразователь по п. 1, о т JT и ч а ю щ и и с я тем, что блок управления состоит из формирователя импульсов, первого, второго и третьего элементов задержки, инвертора, элемента ИЛИ и первого и второго элементов И, первый вход блока управления через соединенные последовательно формирователь импульсов, первый и второй элементы задержки подключен к первому входу блока управления , второй вход которого соединен с первым входом элемента ИЛИ, третий

/4888

вход подключен к первому входу перв . го эле1-«ента И и через инвертор - к первому входу второго элемента И, четвертый вход через третий элемент задержки соединен с вторыми входами первого и второго элементов И, второй вход элемента ШБ1 подключен к выходу второго элемента И, а выход к четвертому выходу блока управления третий выход которого соединен с выходом первого элемента задержки, а второй выход подключен к выходу первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Устройство для ввода информации | 1982 |

|

SU1089566A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Адаптивное микропрограммное устройство управления | 1980 |

|

SU934471A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

1. ПРЕОБРАЗОВАТЕЛЬ НОМЕРА ДАТЧИКА В ЦИФРОВОЙ КОД, содержащий регистр, информационные входы которого соединены с входными шинами, разрядные выходы -подключены к входам блока кодирования и элемента И-НЕ, выход которого соединен с первым входом блока управления и с входом управления регистра, установочный вход которого соединен с первым выходом блока управления, второй выход которого соединен с шиной готовности, второй вход пйдключен к шине сброса, а третий вход - к выходу блока выделения совпадений, входы которого соединены с соответствующими входами шифратора, выходы которого подключены к выходным шинам, отличающийся TeMj что, с целью повышения точности преобразования, в него введен буферный запоминающий блок, информационные входы и .выходы которого соединены соответст.венно С выходами блока кодирования и входами блока выделения совпадений, а вход записи, вход управления и выход готовности буферного запоминающего блока подключены соответственно к тр.етьему и четвертому выходам и к (Л четвертому входу блока управления. Од 4;: 00 00 00

Изобретение относится к вычислительной технике и может быть использовано в многомерных аназшзаторах при статистическом анализе угловых распределений, а также при измерении интенсивности излучений во многих точках пр.остранства.

Известно устройство, содержащее блок управления, шифратор номера детектора, входы которого соединены с входными шинами устройства, а выходы, через регистр подключены к выходным шинам. .

Недостаток такого устройства низкая точность преобразования.

Наиболее близким техническим решением к изобретению является преобразователь номера датчика в цифровой КОД) содержащий регистр, информационные входы которого соединены с ВХОДНЫГ-1И шинами, разрядные выходы подключены к входам блока кодирования и элемента И-НЕ, выход которого соединен с первым входом блока управления и с входом управления регистра, установочный вход которого соединен с первым выходом блока управления, второй выход которого соединен с шиной готовности, второй вход подключен к шине сброса, а третий вход - к выходу блока выделения совпадений, входы которого соединены с соответствующими входами шифратора, выходы которого . подключены к выходным шинам.

Недостатком этого устройства является потеря информации, вследствие

чего интенсивность появления двоичных кодов на выходе устройства становится меньше интенсивности поступления входных импульсов, что приводит к снижению точности преобразования.

Цель изобретения - повышение точности преобразования.

Поставленная цель достигается

тем, что в преобразователь номера датчика в цифровой код, содержащий регистр, информационные входы которого соединены с входными шинами, разрядные выходы подключены к входам блока кодирования и элемента

И-НЕ, выход которого соединен с первым входом блока управления и с ёходом управления регистра, устано-. вочный вход которого соединен с

первым выходом блока управления, второй выход которого соединен с шиной готовности,,второй вход подключен к шине сброса, а третий вход к выходу блока выделения совпадеНИИ, входы которого соединены с соответствуюшр ми входами шифратора, выходы которого подключены к выходным шинам, введен буферный запоминающий блок, информационные входы и

выходы которого соединены соответственно с выходами блока кодирования и входами блока вьиеления совпадений, а вход записи, вход управления и выход готовности буферного запоминающего блока подключены соответственно к третьему и четвертому выходам и к четвертому входу блока управления .

Причем блок управления состоит иэ формирователя импульсов, первого, . второго и третьего элементов задерж ки, инвертора, элемента Ш1И и первого и второго элементов И, первый вхо блока управления через соединенные последовательно формирователь импульсов, первый и .второй элементы задержки подключен к первому, выходу блока управления, второй .вход которого coe динен с первым входом элемента ИЛИ, третий вход подключен к первс му входу первого элемента И и через инвертор - к первому входу второго элемента И, четвертый вход через третий элемент задержки соединен с вторыми входами первого и второго элементов И, второй вход элемента ИЛИ подключе к выходу второго элемента И, а выход к четвертому выходу блока управления третий выход которого соединен с выходом первого элемента задержки, а второй выход подключен к выходу первого элемента И.

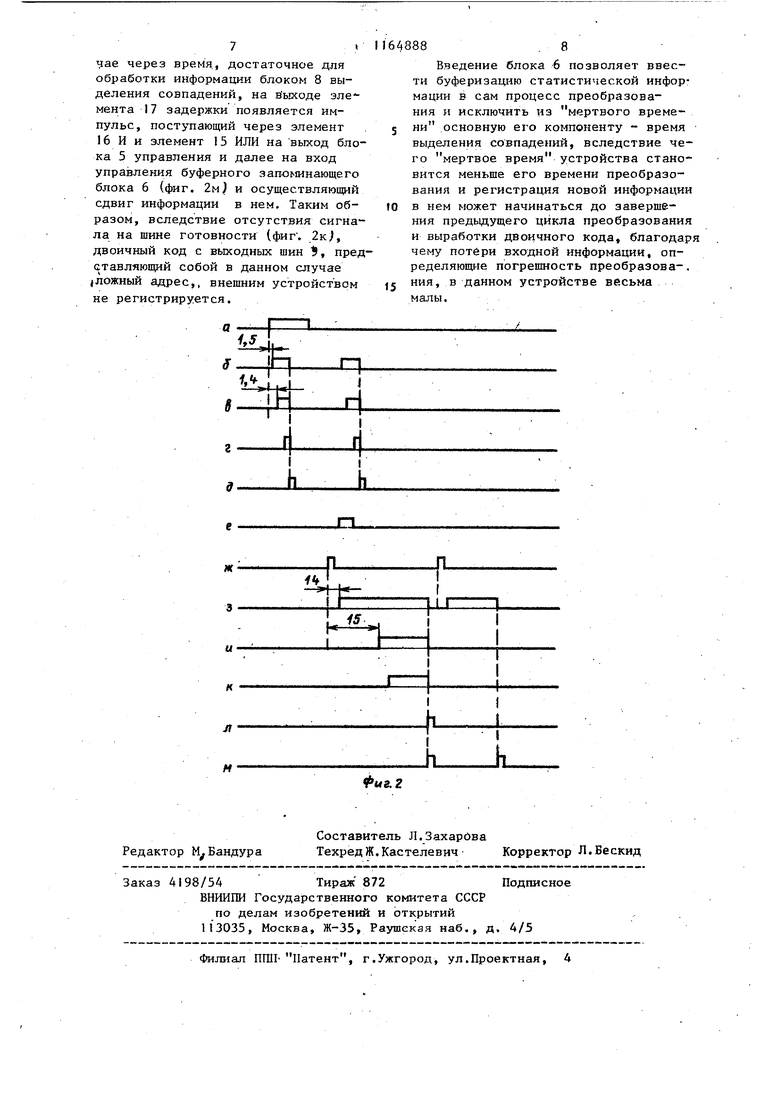

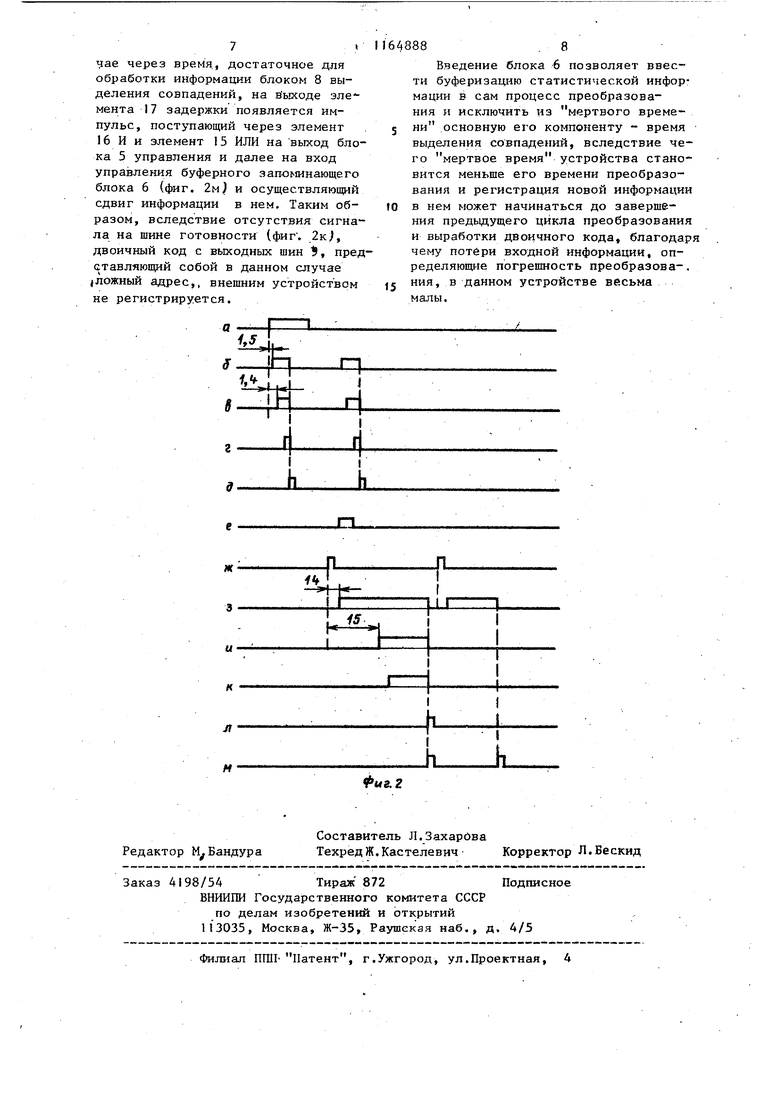

На фиг.1 представлена функциональ ная схема предлагаемого устройства; на фиг.2 - временные диаграммы, иллюстрирующие его работу.

Устройство содержит (п+1) разрядный регистр 1, информационные входы которого соединены с соответствующими входными щинами 2, разрядные выходы регистра 1 соедине.ны с входами: блока 3 кодирования, выполненного в виде К-координатной матрицы, и с входами элемента 4 И-НЕ, выход которого соединен с первым входом блока 5 управления и с входом управления регистра 1, установочный вход которого соединен с первым выходом блока 5 управления, выходы блока 3 кодирования соединены с соответствуюП1дми входами буферного запоминающего блока 6, информационные выходы которого подключены к соответствующим входам шифратора 7 и входам блока 8 выделения совпадения, выходы шифратора 7 соединены с выходными шинами 9, второй выход блока 5 управления подключен к щине 10 готовности, а щина 1 сброса соединена с вторым входом блока 5 управления, третий и четвертый выходы которого соединены соответственно с входами записи и управления буферного запоминающего блока 6, выход управления которого сое динен с четвертым входом блока 5 .управления, который состоит из формирователя 12 импульсов, вход которого соединен с первым входом блока 5 а выход через первый элемент 13 задержки соединен с третьим выходом блока 5 управления и с входом второго элемента 14 задержки, первый вход элемента 15 ИПИ соединен с вторым входом блока 5 управления, втор вход - с выходом элемента 16 И, а выход подключен к четвертому выходу блока 5 управления, четвертый вход которого через третий элемент 17 задержки подключен к входам элементов 16, 18 И, третий вход блока 5 управления соединен с другим входом элемента 18 И и через инвертор 19 - с другим входом элемента 16 И.

К-координатная матрица блока 3 кодирования выполнена в виде К групп элементов 20 ИЛИ по m элементов в каждой. Каждый из входов блока 3 кодирования соединен с одним из входов одного-из элементов 20 ИЛИ каждой группы. Выходы элементов 20 ИЛИ, относящиеся к одной группе, образуют соответствующую группу выходов блока 3 кодирования.

Блок 8 выделения совпадений состоит из соединенных последовательно сумматоров 21 и элемента 22 сравнения, другие входы которого подключены к выходам регистра 23.

В качестве шифратора 7 может быть использовано устройство (3 ), а в качестве буферного запоминающего блока - устройство (4).

Работу устройства рассмотрим для случая использования, в блоке 3 кодирования К-координатной .матрицы с m 2 , где а - целое число.

Устройство работает следующим образом.

В случайный момент времени на одну из входных шин 2 поступает импульс (фиг.2аК Через входную шину 2 входной сигнал- поступает на информационный вход регистра 1, изменяя состояние его первого разряда. При этом на выходе элемента 4 И-НЕ ус анавливается логическая 1 (фиг.26), поступакгщая на вход управления регистра I и блокирующая его. Кроме того, сигнал с выхода элемента 4 И-НЕ поступает на первый вход блока 5 управления и запускает формирователь 12, а информации с разрядных выходов регистра I поступает на входы блока 3 кодирования и далее на входы соответствующих элементов 20 ИЛИ, .на выходах которых вырабатывается си1-пал логической 1. С выходов блока 3 кодирования информация в закодированном виде поступает на информационные входы буферного запоминающего блока 6 (фиг.2в). По истечении времени, достаточного для обработки информации блоком 3 кодирования, импульс формирователя 12 через-элемент И 3 задержки поступает на выход,блока 5 управления (фиг. 2г ) и далее на вход записи бу ферного запоминающегоблока. 6, осуществляя запись по его первому адре информации с выходов блока 3 кодиро вания. Вслед за тем появляется импульс на выходе элемен:га 14 задержк поступающий через выход блока 5 управления на установочный вход регис ра 1 (фиг.2д )и устанавливающий его исходное состояние. Таким образом, в первичном преобразовании и регистрации информации в устройстве участвуют только регист и блоки 3, 6 чем определяется присущая ему весьма малая величина мер вого времени. Информация из первого адреса буферного запоминающего, блока 6 автоматически перемещается в.его по-, следний адрес, освобождая место для последующих записей. При поступлении информации одновременно на несколько входных шин 2 (фиг. 2а, е ), информация о зарегистрированных регистром 1 сигналах вновь записывается по первому адресу буферного запоминающего .блока 6 и произведенная запись автоматически перемещается в его предпоследний адрес. После перемещения записи, сделанной в буферной запоминающий блок 6, в его последний .адрес, на выходе готовности вырабатьшается импульс (фиг. 2ж|, поступающий на вход блока 5 управления и через элемент 17 задержки на один из входов элемен тов 16,18И. Вместе с тем сигналы с информацио ных выходов буферного запоминающего блока 6 поступают иа входы шифратора 7, который преобразует их в двоич ный код, передаваемьш на выходные ши ны 9 (фиг.2з). Кроме того, информация с блока 6 поступает на входы бло ка 8 выделения совпадений и дапее н входы младших разрядов комбинационных сумматоров 21, вследствие чего на разрядных выходах сумматора 21 88 .6 образуется двоичный код (в данном примере код числа К.), который поступает на входы элемента 22 сравнения. На другие входы элемента 22 сравнения с разрядных выходов ретистра 23 поступает двоичный код числа (К+1 ), поэтому на выходе элемента 22 сравнения в данном случае присутствует логическая 1., которая поступает через вход (фиг,2и блока 5 управления (фиг.2- на другой вход элемента 13 И, на выходе которого через время, достаточное для обработки информации блоком 8 выделения совпадений, появляется логическая 1, поступающая через выход блока 5 управления на шину 10 готовности (фиг. 2к ), Таким образом, анализ информации на наличие совпадений и формирование двоичного кода осуществляется в регуляризированном потоке и не препятствуют регистрации информации регистром 1 и ее первичной обработке. После регистрации с выходных щин 9 двоичного кода, отражающего номер входной шины 2, принявшей сигнал внешним устройством, последнее подает на шину 11 сброса импульс (фиг. 2л), поступающий на вход блока 5 управления. Поступивший импульс проходит через .элемент 15 ИЛИ и вызывает генерацию импульса на выходе блока 5 управления, кОторьш поступает навход управления (,фиг. 2м ) буферного запоминающего блока 6 и стирает информацию из его последнего адреса. При этом вся записанная в буферном запоминающем блоке 6 информация перемещается на один адрес и при заполнении последнего адреса на выходе готовности образуется импульс (фиг. 2ж), поступающий на вход блока 5 управления. Информация с выходов буферного запоминающего блока 6 вновь поступает на.входы шифратора 7, который преобразует ее в двоичный код, поступающий на выходные шины 9 (фиг. 2з). Если считываемая с информационных выходов блока 6 информация отражает наличие совпадений импульсов на входных шинах 2, то на выходе блока 8 выделения совпадений сохраняется логический О (фиг. 2i), поступающий через вход блока 5 управления на вход инвертора 19, логическая 1 с выхода которого поступает на один из входов элемента 16 И. В этом случае через время, достаточное для обработки информации блоком 8 выделения совпадений, на вькоде эле мента 17 задержки появляется импульс, поступающий через элемент 16 И и элемент 15 ИЛИ на выход блока 5 управления и далее на вход управления буферного запоминающего блока 6 (фиг. 2мJ и осуществляющий сдвиг информации в нем. Таким образом, вследствие отсутствия сигннла на шине готовности (фиг. 2к), двоичный код с вькодных шин S, представляющий собой в данном случае ложный адрес,, внешним устройством не регистрируется.

Введение блока 6 позволяет ввести буферизацию статистической информации в сам процесс преобразования и исключить из мертвого време5 ни основную его компоненту - время выделения совпадений, вследствие чего мертвое время устройства становится меньше его времени преобразования и регистрация новой информации в нем может начинаться до завершения предыдущего цикла преобразования и выработки двоичного кода, благодаря чему потери входной информации, определяющие погрешность преобразова-. НИН, в данном устройстве весьма малы.

Авторы

Даты

1985-06-30—Публикация

1984-01-20—Подача