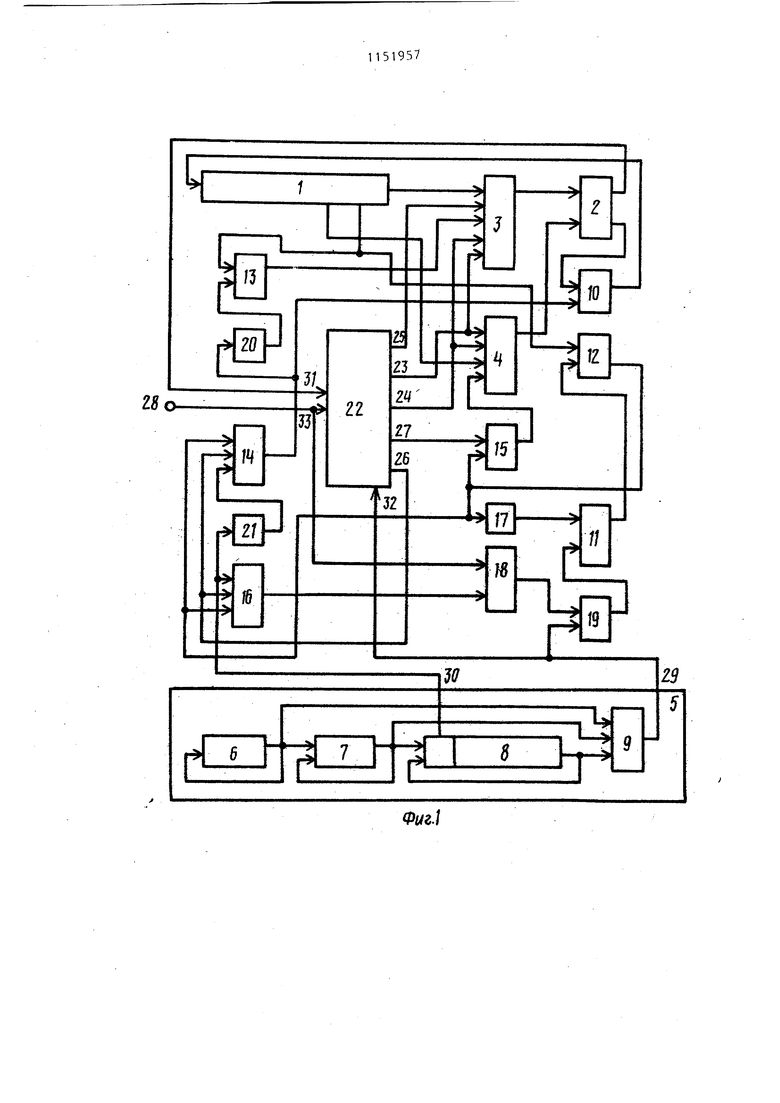

разряда третьего сдвигающего регистра и с входом второго элемента НЕ, выход которого соединен с третьим входом третьего элемента И, выход седьмого элемента И соединен с единичным входом второго триггера, нулевой вход которого соединен с входной шиной начальной установки устройства, а инверсный выход - с первым входом шестого элемента И, второй вход которого соединен с выходом пятого элемента И, выход шестого элемента И соединен с единичным входом первого триггера, причем блок управления содержит три триггера, три элемента И, элемент ИЛИ, элемент НЕ и счетчик, причем выход первого триггера блока управления является первым выходом блока управления и соединен с информационным входом второго триггера блока управления, выход которого соединен с первыми входами первого, второго элементов И блока управления, второй вход первого элемента И блока управления соединен с входом элемента НЕ блока управления и с первым входом блока управления, а второй вход второго элемента И блока управления соединен с вьрсодом элемента НЕ блока управле51957

ПИЯ, выход iiejiBoro элемента И блока управления соединен с первым входом элемента ИЛИ блока управления и япляется пятым выходом блока управления, выход второго элемента И блока управления соединен с информационным входом третьего триггера блока управления и является вторым выходом блока управления, выход третьего триггера блока управления является третьим и четвертым выходами блока управления и соединен с первым входом третьего элемента И блока управления и входом счетчика, выход которого соединен с вторым входом третьего элемента И блока управления, выход третьего элемента И блока управления соединен с вторым входом элемента ИЛИ блока управления, выход элемента ИЛИ блока управления соединен с информационньи входом первого триггера, блока управления, единичный вход которого соединен с нулевыми входами второго и третьего триггеров блока управления и входом сброса счетчика и является вторым входом блока управления, сдвиговые входы триггеров блока управления объединены между собой и. являются третьим входом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Цифровой фазовращатель | 1986 |

|

SU1372593A1 |

| Устройство для вычисления элементарных функций | 1974 |

|

SU560229A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Арифметическое устройство | 1981 |

|

SU993252A1 |

| Устройство для выполнения базовой операции быстрого преобразования Хартли-Фурье вещественных последовательностей | 1990 |

|

SU1718229A1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

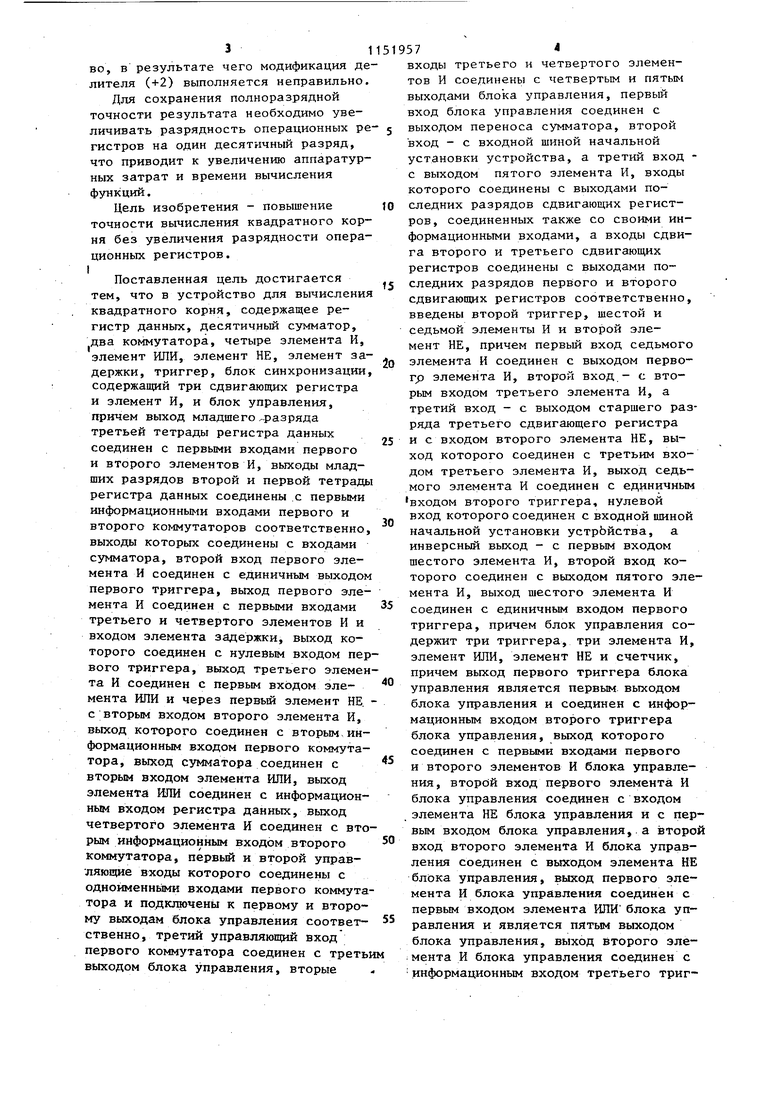

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее регистр данных, десятичный сумматор, два коммутатора, четыре элемента И, элемент ШШ, элемент НЕ, элемент задержки, триггер, блок синхронизации, содержащий три сдвигающих регистра и элемент И, и блок управления, причем выход младшего разряда третьей тетрады регистра данных соединен с первыми входами первого и второго элементов И, выходы младших разрядов второй и первой тетрады регистра данных соединены с первыми информационными входами первого и второго коммутаторов соответственно, выходы которых соединены с входами сумматора, второй вход первого элемента И соединен с единичным выходом первого триггера, выход первого элемента И соединен с первыми входами третьего и четвертого элементов И и входом элемента задержки, выход которого соединен с нулевым входом первого триггера, выход третьего элемента И соединен с первым входом элемента ИЛИ и через первый элемент НЕ - с вторым входом второго элемента И, выход которого соединен с вторым информационным входом первого коммутатора, выход сумматора соед Гнен с вторым входом элемента. ИЛИ, выход элемента Ш1И соединен с информа-ционным входом регистра данных, выход четвертого элемента И соединен с вторым информационным входом второго коммутатора, первый и второй управляющие входы которого соединены с одноименными входами первого коммутатора и подключены к первому и второму выходам блока управления соответственно, третий управляющий вход первого коммутатора соединен с третьим выходом блока управления, вторые входы третьего и четвертого элементов (Я И соединены с четвертым и пятьпч выходами блока управления, первый вход блока управления соединен с выходом переноса сумматора, второй вход - с входной шиной начальной установки устройства,а третий вход - с выходом пятого элемента И, входы которого соединены с выходами последних разряел дов сдвигающих регистров, соединенных также со своими информационными вхосо дами, а входы сдвига второго и третьО1 его сдвигающих регистров соединены с выходами последних разрядов первого и второго сдвигающих регистров соответственно, отличающееся тем, что, с целью повьшения точности, оно содержит второй триггер, шестой и седьмой элементы И и второй элемент НЕ, причем первый вход седьмого элемента И соединен с выходом первого элемента И, второй вход - с вторым входом третьего элемента И, а третий вход - с выходом старшего

I

Изобретение относится к вычислительной технике и может найти применение при разработке последовательны вычислительных машин, например ЭКВМ.

Известно устройство, предназначен ное для вычисления квадратного корня при импульсно-числовом способе передачи информации, содержащее два двоиных счетчика, счетный триггер и вентили передачи кода из одного счетчика в другой О .

Недостатком этого устройства является его низкое быстродействие, особенно при большой разрядности чисел.

Известно устройство для вычисления квадратного корня, содержащее регистры, два сумматора и схему сравнения 2J.

Недостатками этого устройства являются его конструктивная сложность

за счет использования двух сумматоров и сложность алгоритма вычисления, определяющая сложность блока управления.

Наиболее близким по технической сущности к предлагаемому является устройство для вычисления квадратного корня, содержащее сумматоры, триггер, регистры, элементы И, ИЛИ, элемент задержки, инвертор и блок управления Сз J.

Недостатком известного устройства является низкая точность вычисления результата в случае нечетного порядка подкоренного выражения. Это объясняется тем, что при вычислении последней цифры результата (количество вычисляемых цифр равно разрядности регистра данных) младший разряд делителя выходит за разрядную сетку впра3во, в результате чего модификация де лителя (+2) выполняется неправильно. Для сохранения полноразрядной точности результата необходимо увеличивать разрядность операционных ре гистров на один десятичный разряд, что приводит к увеличению аппаратурных затрат и времени вычисления функций. Цель изобретения - повышение точности вычисления квадратного корня без увеличения разрядности операционных регистров, Поставленная цель достигается тем, что в устройство для вычислени квадратного корня, содержащее регистр данных, десятичный суьсматор, два коммутатора, четыре элемента И, элемент ИЛИ, элемент НЕ, элемент задержки, триггер, блок синхронизации содержащий три сдвигающих регистра и элемент И, и блок управления, причем выход младшего .разряда третьей тетрады регистра данных соединен с первыми входами первого и второго элементов И, выходы младших разрядов второй и первой тетрады регистра данных соединены .с первыми информационными входами первого и второго коммутаторов соответственно выходы которых соединены с входами сумматора, второй вход первого элемента И соединен с единичным выходом первого триггера, выход первого элемента И соединен с первыми входами третьего и четвертого элементов И и входом элемента задержки, выход которого соединен с нулевым входом пер вого триггера, выход третьего элемен та И соединен с первым входом элемента ИЛИ и через первый элемент НЕ. с вторым входом второго элемента И, выход которого соединен с вторым информационным входом первого коммутатора, выход сумматора соединен с вторым входом элемента ИЛИ, выход элемента Ш1И соединен с информационным входом регистра данных, выход четвертого элемента И соединен с вто рым информационным входом второго коммутатора, первый и второй управляющие входы которого соединены с одноименными входами первого коммута тора и подкгаочены к первому и второму выходам блока управления соответственно, третий управляющий вход первого коммутатора соединен с треть выходом блока управления, вторые 57Л входы третьего и четвертого элементов И соединены с четвертым и пятым выходами блока управления, первый вход блока управления соединен с выходом переноса сумматора, второй вход - с входной шиной начальной установки устройства, а третий вход с выходом пятого элемента И, входы которого соединены с выходами последних разрядов сдвигающих регистров, соединенных также со своими информационными входами, а входы сдвига второго и третьего сдвигающих регистров соединены с выходами последних разрядов первого и второго сдвигающих регистров соответственно, введены второй триггер, шестой и седьмой элементы И и второй элемент НЕ, причем первый вход седьмого элемента И соединен с выходом первогр элемента И, второй вход.- с вторым входом третьего элемента И, а третий вход - с выходом старшего разряда третьего сдвигающего регистра и с входом второго элемента НЕ, выход которого Соединен с третьим входом третьего элемента И, выход седьмого элемента И соединен с единичным входом второго триггера, нулевой вход которого соединен с входной шиной начальной установки устрЬйства, а инверсньш выход - с первым входом шестого элемента И, второй вход которого соединен с выходом пятого элемента И, выход шестого элемента И соединен с единичным входом первого триггера, причем блок управления содержит три триггера, три элемента И, элемент ИЛИ, элемент НЕ и счетчик, причем выход первого триггера блока управления является первым выходом блока управления и соединен с информационным входом второго триггера блока управления, выход которого соединен с первыми входами первого и второго элементов И блока управления, второй вход первого элемента И блока управления соединен с входом элемента НЕ блока управления и с первым входом блока управления,. а второй вход второго элемента И блока управления соединен с выходом элемента НЕ блока управления, выход первого элемента И блока управления соединен с первым входом элемента ИЛИ блока управления и является пятьм выходом блока управления, выход второго элемента И блока управления соединен с информационным входом третьего триг«гера блока управления и является вт рым ВЫХОДОМ блока управления, выход третьего триггера блока управления является третьим и четвертым выхода блока управления и соединен с первым входом третьего элемента И блока управления и входом счетчика, выход которого соединен с вторым входом третьего элемента И блока управления выход третьего элемента И блока управления соединен с вторым входом элемента ИЛИ блока управления, выход элемента ИЛИ блока управления соединен с информационным входом первого триггера блока управления, единичный вход которого соединен с нулевыми входами второго и третьего триггеров блока управления и входом сброса счетчика и является вторым входом блока управления, сдвиговые входы триггеров блока управления объединен между собой и являются третьим входо блока управления. Благодаря введению новых признаков, а именно второго триггера и эле ментов И, выход первого из которых соединен с единичным входом второго триггера., а нулевой выход триггера соединен с входом второго элемента И предлагаемое устройство обеспечивает более высокую точность вычисления последней цифры корня при нечетном порядке аргумента. Ни оДно из извест ных решений не цмеет предлагаемой схемы, и поэтому точность вычисления последней цифры корня в известных устройствах tl и 23 при нечетном порядке аргумента низкая. Для обеспе чения необходимой точности результата устройство для извлечения квадратного корня з1 может быть выполнено с увеличенной разрядностью операционных регистров, что приводит к существенным затратам оборудования На фиг.1 представлена схема устройства для вычисления квадратного корня; на фиг.2 - функциональная схема блока управления. Устройство содержит регистр 1 данных,.десятичный сумматор 2, коммутаторы 3 и 4, блок 5 синхронизации, содержащий три сдвиговых рег-истра 6 - 8 и элемент И 9, элемент ИЛИ 10, триггер 11, элементы И 12-16, элемент 17 задержки, триггер 18, элемент И 19, элементы НЕ 20 и 21, блок 22 управления (БУ), выходные шины 23-27 БУ 22, внешнюю шину 28, 957 шины 29 и 30 блока 5 синхронизации, входные шины 31-33 БУ 22. Блок 22 управления содержит три триггера 34-36, элементы И 37-39, элемент РШИ 40, счетчик 41 и элемент НЕ 42, Устройство работает следующим образом. Регистр 1 данных хранит три операнда. Операнды хранятся в регистре 1 таким образом, что одноименные десятичные разряды разных операндов группируются совместно. Подкоренное выражение записывается в регистр 1 на место второго (считая справа) операнда. Перед началом вычисления в регистр 1 на место первого операнда записывается 1 в самый старший разряд в случае, если порядок подкоренного выражения четный. Если порядок подкоренного выражения нечетный, то установка единицы производится со сдвигом вправо на один десятичный разряд. Далее вьшолняется обычный процесс деления посредством последовательных вычитаний делителя из делимого. При этом на выходной шине 23 БУ 22 вырабатывается сигнал, поступающий на коммутаторы 3 и 4 и обеспечивающий вычитание первого операнда из второго. Для запуска вычислений по входной шине 28 поступает сигнал, обеспечивающий установку в состояние Лог.1 триггера 34 и обнуление триггеров 35 и 36 и счетчика 41. На вход 32 БУ 22, соединенный со сдвиговыми входами триггеров 34-36, поступает тактирующий сигнал с вьиода 29 блока 5 синхронизации, чем обеспечивается инхронное изменение управляющих игналов на выходах БУ 22. С выхода риггера 34 сигнал Лог.1 постуает на вход триггера 35 и на шину 3 БУ 22, с которой далее поступает а коммутаторы 3 и 4 и обеспечивает ычитание первого операнда из второго. Моменты поступления импульсов по ине 29 блока 5 синхронизации на вход 2 БУ 22 синхронизированы с моментами кончания выполнения микрокоманд, адаваемых выходными сигналами БУ 22. После окончания вычитания на вход 2 БУ 22 поступает импульс, который беспечивает занесение Лог.1 из риггера 34 в триггер 35, в результае чего на первые входы элементов 11 И 37 и 38 поступает сигнал Лог,1, В этот момент выполняется анализ знака остатка делимого по значению переноса сумматора 2, сформированного пос ле предыдущего вычитания и поступающе го по шине 31 БУ 22. При положительном остатке на вход 31 БУ 22 поступает сигнал Лог.1, при этом на выходе элемента И 37, соединенном с шиной 27 БУ 22, формируется сигнал Лог.1, обеспечивающий модификацию делителя. Для выполнения модификации делителя в самом начале работы блока 5 синхронизации триггер 11 устанавливается в состояние Лог. посредством сигнала, вырабатываемого на выходе элемента И 19, на первый вход которого поступает сигнал с выхо да элемента И 9. Сигнал на выходе элемента И 9 вырабатьгеается в момент прихода регистров 6-8 блока 5 синхронизации в исходное состояние (наличие Лог.Г в первых разрядах регистров); для этого входы элемента И 9 соединены с выходами последних разрядов регистров 6-8. На второй вход элемента И 19 поступает сигнал с нуле вого плеча триггера 18, который устанавливается в состояние Лог.О перед началом вычисления квадратного корня по шине 28 БУ 22. При наличии Лог.1 на выходе триггера 11 на выходе элемента И 12 формируется одиночный импульс, соответствующий младшей единице первого операнда регистра 1. Именно в этот момент производится модификация делителя (первого операнда). Для этого сигнал с выхода элемента И 12 поступает на первый вход элемента И 15, на второй вход которого поступает сигнал по шине 27 БУ 22, разрешающий модификацию делителя. С выхода элемента И 15 информация поступает на вход коммутатора 4 и далее на вход сумматора 2. Сигнал с выхода элемента И 37 поступает через элемент ИЛИ 40 на вход триггера 34, в результате чего после выполнения модификации делителя вновь .устанавливается в состояние Лог.1 триггер 34, и вновь возбуждается шина 23 БУ 22 и выполняется вычитание, как описано вьше. Б случае отрицательного остатка производится его восстановление, а модификация делителя не выполняется. 7 При отрицательном остатке на вход 31 БУ 22 поступает сигнал Лог.О, при этом на выходе элемента НЕ 42 и соответственно на выходе элемента И 38, соединенном с шиной 24 БУ 22, формируется сигнал Лог.1. Этот сигнал по шине 24 БУ 22 поступает на четверть е входы коммутаторов 3 и 4 и обеспечивает прибавление первого операнда к второму (делителя к остатку) . СигнсШ с выхода элемента И 38 поступает также на вход триггера 36, в результате после прихода очередного импульса на вход 32 БУ 22, сигнал Лог.Г заносится в триггер 36, выход которого соединен с шинами 25 и 26 БУ 22. После восстановления остатка выполняется сдвиг влево остатка и частного, т.е. второго и третьего, операндов, хранящихся в регистре 1. Непоследовательных вычислительных машинах, использующих динамические регистры, информация в которых непрерывно циркулирует вправо, сдвиг влево выполняется посредством удлинения цепи циркуляции на один десятичный разряд во время сдвига влево. Для этого на второй информационный вход коммутатора 3 поступает информация с третьего выхода регистра 1, а на третий управляющий вход коммутатора 3 сигнал с выхода 25 БУ 22, разрешающий прохождение информации с третьего выхода регистра 1 на вход сумматора 2 и далее опять на вход регистра 1. Одновременно со сдвигом влево остатка в регистре 1 выполняется формирование нового делителя (первого операнда, хранящегося в регистре 1). Для этого с выхода 26 БУ 22 сигнал Лог.1 поступает на первый вход элемента И 14, на второй вход которого поступает импульс, вьфабатьшаемый описанным выше образом на выходе элемента И 12. Третий вход элемента И 14 связан с выходом элемента НЕ 21, на вход которого поступает сигнал с выхода первого разряда регистра 8 блока 5 синхронизации. Такт образом, выработка сигнала на выходе элемента И 14 возможна только при нулевом значении первого разряда регистра 8. Сигнал Лог.1, появившийся на выходе элемента И 14, поступает на вход элемента ИЛИ 10 и на вход элемента НЕ 20, на выходе которого формируется Лог.О, в результате чего элемент , И 13 запирается. Последовательный двоично-десятичный сумматор 2 имеет задержку, равную одной тетраде,- поэтому младшая единица делителя сдвинется на один десятичный разряд вора во. Это соответствует формированию нового делителя. Одновременно к счет 1чику 41 прибавляется единица. Выход .третьего триггера 36 соединен также ci первым входом элемента И 39,второй. ;вход которого .соединен с выходом счетчика 41, на котором вырабатывается сигнал Лог.1 до момента накопления в счетчике 41 величины,равной разрядности частного. После этого на выходе счетчика 41 устанавливается Лог.О. Сигнал с выхода элемента И 39 через элемент ИЛИ 40 поступает на вход триггера 34. образом, циклы вычисления цифр частного выполняется до тех пор, пока не получают частное полной разрядности. Перед вычислением последней .цифры частного в случае нечетного поряд ка подкоренного выражения в младшем разряде делителя оказывается Лог.1 При формировании делителя для последней цифры частного единица на первом выходе регистра 1 появляется в момент нахождения Лог.1 в первом разряде регистра 8 блока 5 синхронизации. 957-10 Поэтому при наличии единичного сигнала на выходе 26 БУ 22 в момент формирования одиночного импульса на выходе элемента И 12 на всех входах элемента И 16 имеются сигналы Лог.Г, в результате чего на выходе элемента И 16 вырабатывается сигнал, производящий установку триггера 18 в единичное состояние. Нулевой выход триггера 18 соединен с входом элемента И 19, поэтому он запирается, в результате чего сигнал с выхода элемента И 9 не может пройти на единичный установочный вход триггера 11. Триггер 11 остается в нулевом состоянии, а делитель - неизменным в течение всего цикла вычисления последней цифры частного (в случае нечетно1о порядка аргумента), После получения последней цифры вычисление квадратного корня заканчивается. Предлагаемое устройство для вычисления квадратного корня позволяет получить последнюю десятичную цифру корня с высокой точностью. При этом увеличение точности достигается без увеличения разрядности операционных регистров и времени вычисления результага, Введенные дополнительные элементы триггер, два элемента И и элемент НЕ требуют для своей реализации весьма незначительных затрат оборудования.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 0 |

|

SU316088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-12-22—Подача