Изобретение относится к вычислительной технике и предназначено для выявления неисправностей типа постоянного О или постоянной 1 в любом цифровом , например блоке синтеза полного телевизионного сигнала системы отображения информации (сои) метеорологической радиолокационной станции (МРЛ).

Целью изобретения является упро- щение устройства.

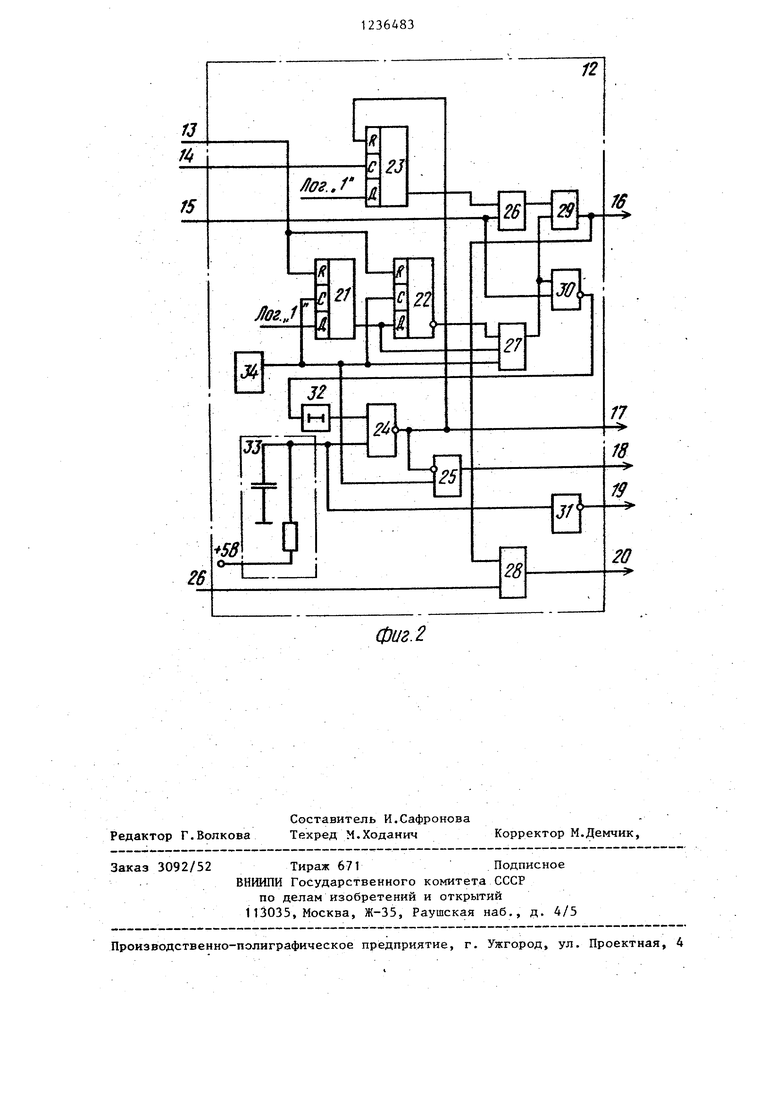

На фиг. 1 изображена структурная схема устройства, на фиг. 2 - функциональная схема блока управления.

Устройство содержит первый 1„ второй 2, третий 3 и четвертый 4 счетчики, блок 5 коммутаторов, коммутатор 6, элемент И 7, элемент ИЛИ 8, блок 9 памяти, блок 10 индикации, блок 11 задания режи- мов, блок 12 управления, входы 13-15 блока управления, выходы 16-20 блока управления.

Блок управления содержит триггеры 21-23, элемент И-НЕ 24, элементы И 25-28, элемент ИЛИ 29, элемент ИЛИ-НЕ 30, элемент НЕ 31, элемент 32 задержки, интегрирующую цепь 33, генератор 34 тактовых импульсов, вход 35 блока управления.

Устройство работает следукяцим образом.

При подаче на вход устройства контроля цифрового блока питающего напряжения на выходе ннтегрируюацей цепи 33 формируется сигнал логической 1, в процессе формирования которого на выходах 17 и 18 блока 12 вырабатываются установочные сигналы П17-1 и nt8-1 соответственно. По сигналу П17-1 устанавливается в О триггер 23 блока 12 и в счетчик 1 записывается код, соответствукмций состояниям счетчиков 2 и 3, которые устанавливаются в исходные состояния по сигналу П18-1 (т.е. счетчик 3 устанавливается в О, а в счетчик 4 записывается исходный код, соответствующий десятичному номеру 01).

Счетчик 2 предназначен для формирования двоичного кода номера сигнала каждого функционально законченного .устройства (ФЗУ) цифрового блока, а счетчики 3 и 4 предназначены соответственно для формирования двоичного и двоично-десятичного кодов номера ФЗУ цифрового блока.

В блоке 9 по каждому адресу, определяемому состояниями счетчиков

5 0

5

5

0

5

0

5

0

2 и 3, записана следующая информация: двоично-десятичный код номера контакта разъема ФЗУ цифрового блока, соответствующего номеру сигнала ФЗУ, код интервала контроля, который программируется в зависимости от частоты контролируемого сигнала (чем ниже частота, тем больше значение кода), признак сигнала (входной или выходной) и сигнал, принимающий значение, равное 1 для последнего контролируемого сигнала каждого ФЗУ цифрового блока.

С выхода коммутатора 6 снимается контролируемый сигнал одного из ФЗУ цифрового блока, номер которого и номер ФЗУ определяются соответственно счетчиками 2 и 3. Поскольку после включения устройства контроля счетчик 2 находится в произвольном состоянии, а счетчик 3 в исходной нулевом состоянии, то с выхода коммутатора 6 снимается j-й контролируемый сигнал первого ФЗУ цифрового блока.

После установки триггеров и счетчиков устройства в исходные состояния при подаче питающего напряжения его работу целесообразно рассматривать в случае отсутствия и в случае наличия неисправности в контролируемом блоке.

При отсутствии неисправности типа логического О или логической 1 по сигналу с выхода элемента И 7 переключается триггер 23 блока 12 в состояние 1. На счетный вход счетчика 1 с выхода генератора 34 через элемент 25 блока 12 проходит импульс 19. По Импульсу 13 с выхода переполнения счетчика 1 блок 12 формирует импульс, по которому счетчик 2 переключается в следующее состояние, и, следовательно, происходит переход к контролю (J+1) сигнала первого ФЗУ цифро13ого блока. Также по импульсу с выхода счетчика 1 с помощью элемента 32 элемент И-НЕ 24 блока 12 формирует новый сигнал установки П17-1, по которому производится подготовка к НОВОМУ такту контроля, а именно устанавливается в О триггер 23 и в счетчик I записывается новьй код, соответствующий (j+1)-My контролируемому сигналу первого ФЗУ цифрово-. го блока. Импульс 17 задержан по отношению к импульсу 15 для того, чтобы до записи нового кода в счетчик 1 произошло переключение счетчика 2

3

в новое состояние и в блоке 9 была произведена новая выборка соответствующей информации.

В некоторый MOMSirT времени блок 9 вырабатывает сигнал окончания контроля первого ФЗУ и блок 12 формирует импульс 20, по которому счетчик 3 и 4 переключаются в состояния, соответствующие второму ФЗУ цифрового блока, а счетчик 2 устанавливается в О. Далее, при отсутствии неисправности происходит последовательная проверка всех сигналов 2-го ФЗУ, 3-го ФЗУ,..., М-го ФЗУ. По импульсу переполнения счетчика 3, т.е. по окончании контроля всех сигналов М-го ФЗУ происходит установка счетчика 4 в исходное состояние, определяющее десятичный номер 01 контролируемого ФЗУ, т.е. начинается новый цикл контроля.

При наличии неисправности после очередной установки в О триггера 23 (в этом случае сигнал на входе 14 постоянно равен О или 1) импульсы на выходах 16 и 20 не формируются, т..е. состояния счетчиков 2-4 не меняются. При этом блок 9 формирует признак типа контролируемого сигнала и двоично-десятичный код номера контакта разъема ФЗУ, где обнаружена неисправность. Тип сигнала и номер контакта разъема ФЗУ, а также номер ФЗУ, формируемый счетчиком 4, индицируются блоком 10.

Формула изобретения

1

Устройство для контроля цифровых блоков, содержащее блок задания режимов, блок индикации, первый счетчик и блок управления, отличающееся тем, что, с целью упрощения устройства, оно содержит блок коммутаторов, коммутатор, второй, третий и четвертый счетчики, блок памяти, элемент И и элемент ИЛИ а блок управления содержит три триггера, четыре элемента И, элемент ИЛИ, элемент ИЛИ-НЕ, элемент И-НБ, элемент НЕ, генератор тактовых импульсов, элемент задержки, интегри- рунмдую цепь, причем первый и второй входы первого элемента И соединены соответственно с прямым выходом первого триггера и первым входом элемента ИЛИ-НЕ, второй вход которого подключен к выходу второго элемента И-и первому входу элемента ИЛИ

и

10

15

20

25

,

2364834

второй вход которого соединен с выходом первого элемента И, первый и второй входы второго элемента И соединены соответственно с инверсным выходом второго триггера и прямым выходом третьего триггера, С-входы второго и третьего триггеров, третий вход второго элемента И, прямой вход третьего элемента И и второй вход четвертого элемента И объединены и соединены с выходом генератора тактовых импульсов, инверсный вход третьего элемента И и R-вход первого триг гера объединены и подключены к выходу элемента И-НЕ, перйьй вход которого соединен через элемент задержки с выходом элемента ШШ-ЯЕ, второй вход элемента И-НЕ объединен с входом элемента НЕ и подключен через интегрирующую цепь к входу порогового потенциала блока управления, прямой выход первого триггера подключен к первому вхрду четвертого элемента И, D-входы первого и третьего триггеров подключены к входу логической единицы блока управления, D-вход второго триггера соединен с прямым выходом третьего триггера, R-вход второго и третьего триггеров блока управления соединен с выходом запуска блока задания режимов устройства, С-вход первого триггера блока управления подключен к выходу элемента И устройства, первый и второй входы элемента И соединены соответственно с выходом задания режима проверки блока задания режимов и выходом коммутатора, группа информационных входов которого подключена - к группе выходов блока коммутации, m групп информационных входов которого подключены к группам выходов соответствующих контролируемых цифровых блоков, группа управляющих вх одов блока коммутации соединена с группой выходов второго счетчика, группа управляющих входов коммутатора подключена к группе информационных выходов третьего счетчика, выход переполнения которого связан с первым входом элемента ИЛИ устройства, второй вход которого объединен с входом сброса третьего счетчика и подключен к выходу элемента НЕ блока управления, счетные входы третьего и четвертого счетчиков и вход сброса второго счетчика устройства объединены и подключены к выходу четвертого элемента И блока управ30

35

40

45

50

55

ления, счетный вход второго счетчика- устройства подключен к выходу первого элемента ИЛИ блока управления, входы установки и счета первого счетчика устройства соединены соответственно с выходами элемента И-НЕ и третьего элемента И блока управления, выход элемента И устройства соединен с вторым входом первого элемента И блока управления, первая и вторая группы адресных входов блока памяти соединены соответственно с группами выходов второго и третьего счетчиков, первая и вторая группы информационных выходов блока памяти связаны соответственно с первой группой входов блока индикации и группой информационных входов первого счетчика выходы признака типа контролируемого сигнала и признака окончания контроля блока памяти подключены соответственно к управляющему входу блока индикации и третьему входу четвертого элемента И блока

управления, вторая группа входов блока индикации соединена с группой выходов четвертого счетчика, первый и второй информационные входы которого являются входами логического нуля и логической единищз устройства, вход установки четвертого счетчика подключен к выходу элемента ИЛИ.

фиг.1

Редактор Г.Волкова

Составитель И.Сафронова

Техред М.Ходанич Корректор М.Демчик,

Заказ 3092/52

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1983 |

|

SU1166115A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Многоканальное устройство для регистрации и индикации аварийных ситуаций | 1990 |

|

SU1796907A1 |

| Устройство для регистрации данных по табельному учету | 1982 |

|

SU1027746A1 |

| Устройство для диагностики неисправностей цифровых интеграторов | 1979 |

|

SU877551A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1259270A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Устройство для централизованного контроля параметров | 1985 |

|

SU1280397A1 |

Изобретение относится к вычислительной технике и предназначено для выявления неисправностей типа постоянного О или постоянной 1 в любом цифровом блоке. Целью изобретения является упрощение устрой-, ства. Для достижения цели в устройство, содержащее блок задания режимов, блок индикации, счетчик и блок Управления, введены коммутатор, блок коммутаторов, три счетчика, блок памяти, элемент И и элемент ИЛИ. 2 ил. (Л с ю со О) сх со

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1166115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-07—Публикация

1984-09-04—Подача