Изобретение относится к вычислительной технике и предназначено для обнаружения, неисправностей в цифровом блоке и индикации операндов в любом цифровом блоке, например в блоке синтеза полного телевизионного сигнала системы отображения информации (сои) метеорологического радиолокатора (МРЛ). .г

Цель изобретения - увеличение глубины контроля.

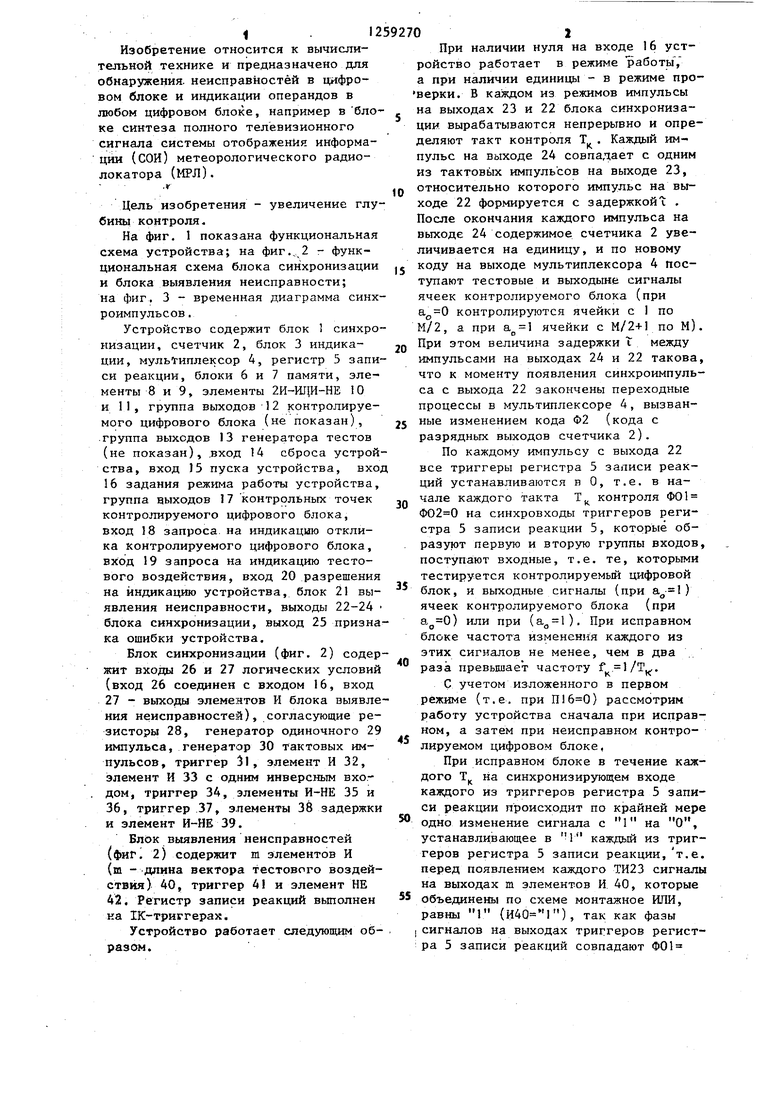

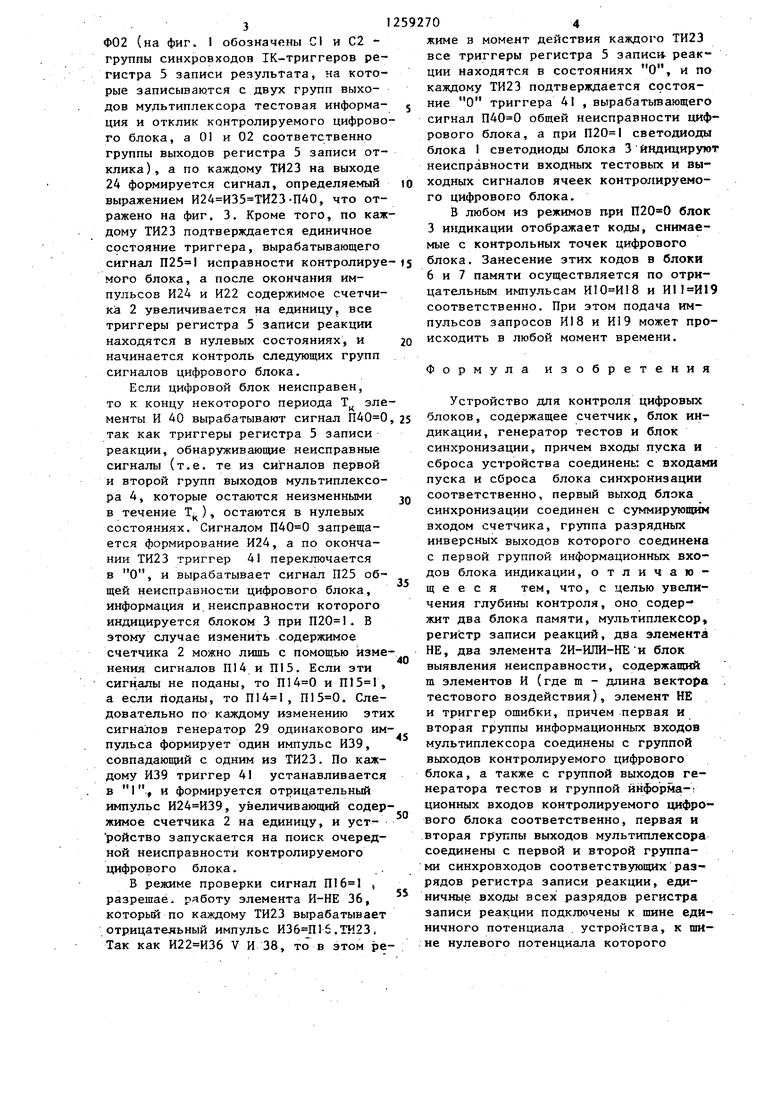

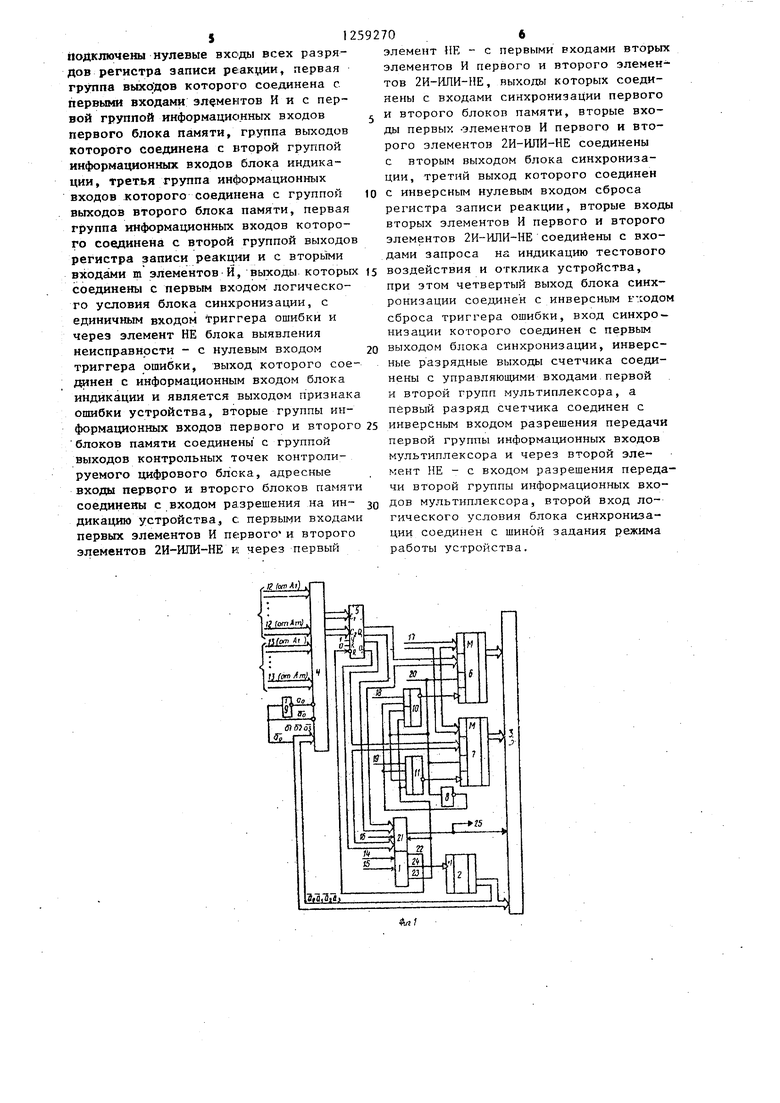

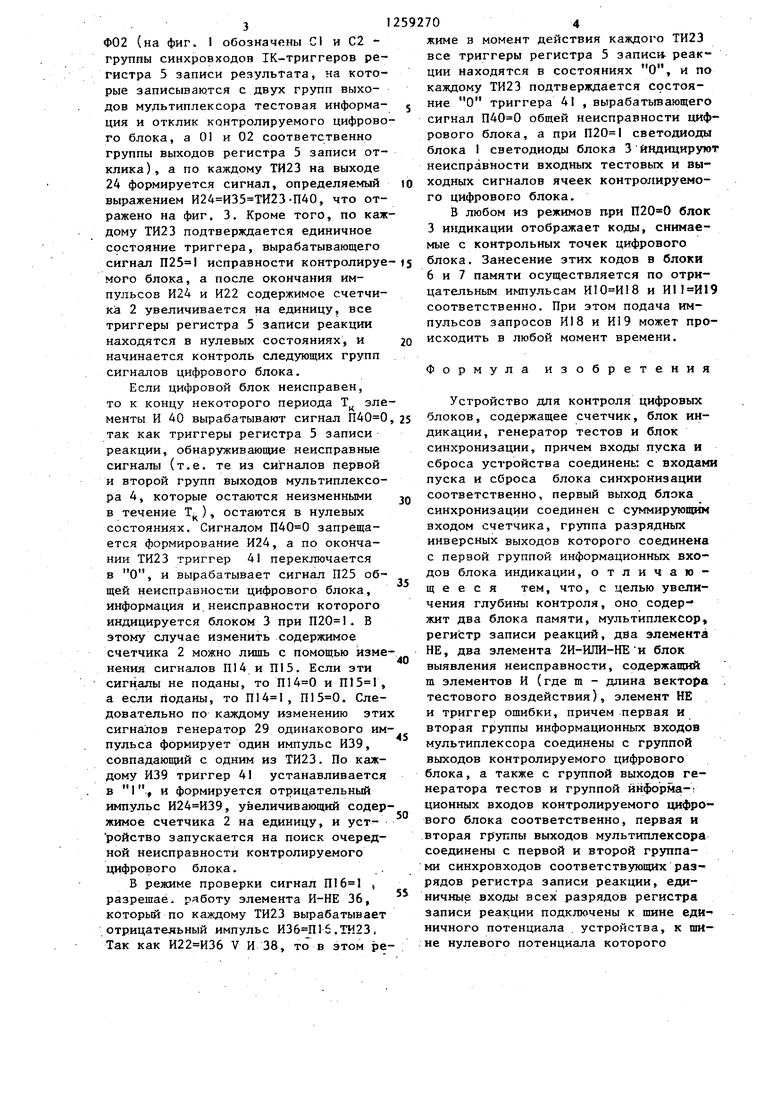

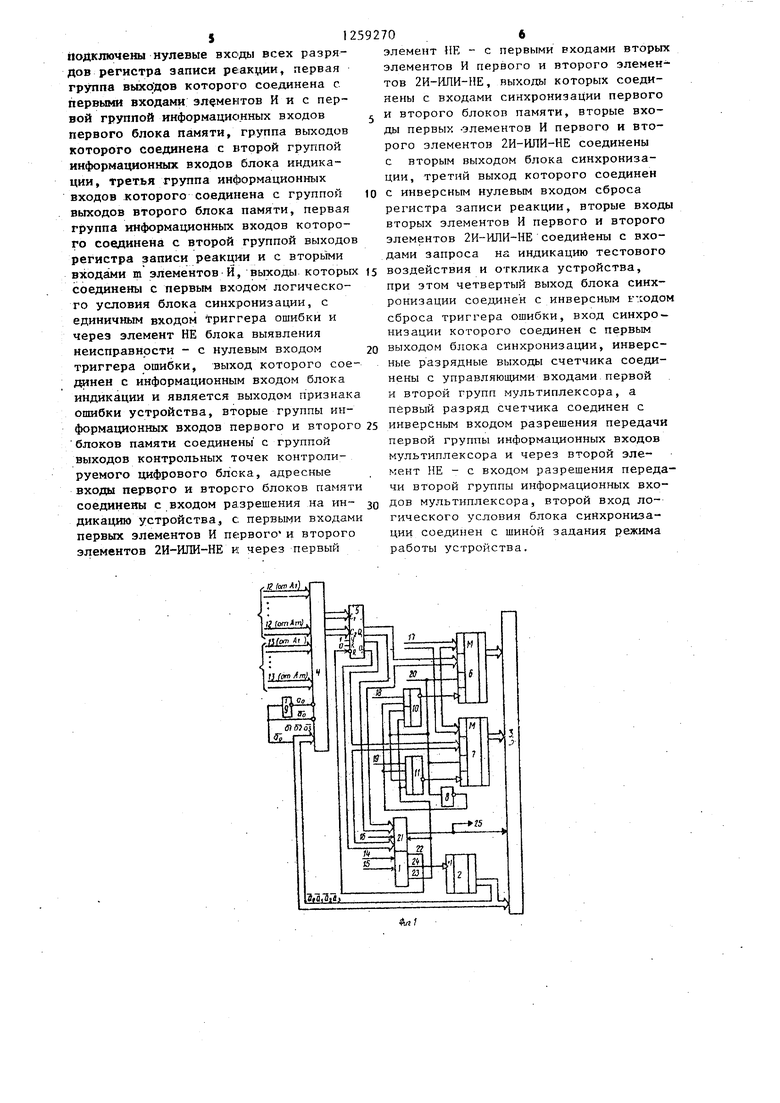

На фиг, 1 показана функциональная схема устройства; на фиг,,, 2 - функциональная схема блока синхронизации и блока выявления неисправности; на фиг, 3 - временная диаграмма синхроимпульсов.

Устройство содержит блок синхронизации, счетчик 2, блок 3 индикации, мультиплексор 4, регистр 5 записи реакции, блоки 6 и 7 памяти, элементы 8 и 9, элементы 2И-Шр-НЕ 10 и 11, группа выходов 12 контролируемого цифрового блока (не показан), группа выходов 13 генератора тестов (не показан), .вход 14 сброса устройства, вход 15 пуска устройства, вход 16 задания режима работы устройства, группа выходов 17 контрольных точек контролируемого цифрового блока, вход 18 запроса, на индикацию отклика контролируемого цифрового блока, вход 19 запроса на индикацию тестового воздействия, вход 20 разрешения на индикацию устройства, блок 21 выявления неисправности, выходы 22-24 блока синхронизации, выход 25 признака ошибки устройства.

Блок синхронизации (фиг. 2) содержит входы 26 и 27 логических условий (вход 26 соединен с входом 16, вход 27 - выходы элементов И блока выявления неисправностей), согласующие резисторы 28, генератор одиночного 29 импульса, генератор 30 тактовых импульсов, триггер 31, элемент И 32, элемент И 33 с одним инверсным вхо.- дом, триггер ЗА, элементы И-НЕ 35 и 36, триггер 37, элементы 38 задержки и элемент И-НБ 39.

Блок выявления неисправностей (фиг. 2) содержит ш элементов И (т - Длина вектора тестового воздействия) 40, триггер 4 и элемент НЕ 42, Регистр записи реакций вьшолнен на 1К-триг г ерах.

Устройство работает следующим образом.

1259270

5

0

5

При наличии нуля на входе 16 устройство работает в режиме работы, а при наличии единицы - в режиме про- верки. В каждом из режимов импульсы на выходах 23 и 22 блока синхронизации вырабатываются непрерывно и определяют такт контроля Т. Каждый импульс на выходе 24 совпадает с одним из тактовых импульсов на выходе 23, относительно которого импульс на выходе 22 формируется с задержкой с . После окончания каждого импульса на выходе 24 содержимое счетчика 2 увеличивается на единицу, и по новому коду на выходе мультиплексора 4 поступают тестовые и выходыне сигналы ячеек контролируемого блока (при в.0 контролируются ячейки с 1 по М/2, а при ячейки с М/2+ по М). При этом величина задержки t между импульсами на выходах 24 и 22 такова, что к моменту появления синхроимпульса с выхода 22 закончены переходные процессы в мультиплексоре 4, вызванные изменением кода Ф2 (кода с разрядных выходов счетчика 2).

По каждому импульсу с выхода 22 все триггеры регистра 5 записи реакций устанавливаются и О, т.е, в начале каждого такта Т контроля Ф01 на синхровходы триггеров регистра 5 записи реакции 5, которые образуют первую и вторую группы входов, поступа ют входные, т.е. те, которыми тестируется контролируемьй цифровой блок, и выходные сигналы (при ) ячеек контролируемого блока (при a.) или при (ag l). При исправном блоке частота изменения каждого из этих сигналов не менее, чем в два раза превьшает частоту f . 1/Т..

К

С учетом изложенного в первом режиме (т.е. при ) рассмотрим работу устройства сначала при исправном, а затем при неисправном контролируемом цифровом блоке,

При исправном блоке в течение каждого 1 на синхронизирующем входе каждого из триггеров регистра 5 записи реакции происходит по крайней мере одно изменение сигнала с 1 на О, устанавливающее в 1 каждьй из триггеров регистра 5 записи реакции, т,е. перед появлением каждого ТИ23 сигналы на выходах m элементов И 40, которые 5 объединены по схеме монтажное ИЛИ, равны 1 (И40), так как фазы I сигналов На выходах триггеров регист- ра 5 записи реакций совпадают Ф01

0

5

0

5

0

Ф02 (на фиг. I обозначены С и С2 - группы синхровходон 1К-триггеров регистра 5 записи результата, на которые записываются с двух групп выходов мультиплексора тестовая информа- ция и отклик контролируемого цифрового блока, а 0 и 02 соответственно группы выходов регистра 5 записи отклика), а по каждому ТИ23 на выходе 24 формируется сигнал, определяемый выражением И24 И35 ТИ23-ПАО, что отражено на фиг, 3. Кроме того, по каждому ТИ23 подтверждается единичное состояние триггера, вырабатывающего сигнал исправности контролируе мого блока, а после окончания импульсов И24 и И22 содержимое счетчика 2 увеличивается на единицу, все триггеры регистра 5 записи реакции находятся в нулевых состояниях, и начинается контроль следующих групп сигналов цифрового блока.

Если цифровой блок неисправен, то к концу некоторого периода Т элементы И 40 вырабатывают сигнал так как триггеры регистра 5 записи реакции, обнаруживающие неисправные сигналы (т.е. те из сигналов первой и второй групп выходов мультиплексора 4, которые остаются неизменными

в течение Т), остаются в нулевых состояниях. Сигналом запрещается формирование И24, а по окончании ТИ23 триггер 41 переключается в О, и вырабатывает сигнал П25 общей неисправности цифрового блока, информация и.неисправности которого индицируется блоком 3 при . В этому случае изменить содержимое счетчика 2 можно лишь с помощью изменения сигналов П14 и П15. Если эти сигналы не поданы, то и , а если поданы, то , . Следовательно по каждому изменению этих сигналов генератор 29 одинакового импульса формирует один импульс И39, совпадающий с одним из ТИ23. По каждому И39 триггер 41 устанавливается в 1 % и формируется отрицательный импульс , увеличивающий содержимое счетчика 2 на единицу, и уст- ройство запускается на поиск очередной неисправности контролируемого цифрового блока..

В режиме проверки сигнал t разрешаем работу элемента И-НЕ 36, который по каждому ТИ23 вырабатывает отрицательный импульс .ТИ23, Так как V И 38, то в этом реjю 15 20

25

0

5

0

5

0

S

жиме в момент действия каждого ТИ23 все триггеры регистра 5 запис реакции находятся в состояниях О, и по каждому ТИ23 подтверждается состояние О триггера 41 , вьтрабатьшающего сигнал общей неисправности цифрового блока, а при светодиоды блока I светодиоды блока 3 индицируют неисправности входных тестовых и выходных сигналов ячеек контролируемого цифрового блока.

В любом из режимов блок 3 индикации отображает коды, снимаемые с контрольных точек цифрового блока. Занесение этих кодов в блоки 6 и 7 памяти осуществляется по отрицательным импульсам и соответственно. При этом подача импульсов запросов И18 и И19 может происходить в любой момент времени.

Формула изобретения

Устройство для контроля цифровых блоков, содержащее счетчик, блок индикации, генератор тестов и блок синхронизации, причем входы пуска и сброса устройства соединены с входами пуска и сброса блока синхронизации соответственно, первый выход блока синхронизации соединен с суммирующим входом счетчика, группа разрядных инверсных выходов которого соединена с первой группой информационных входов блока индикации, отличающееся тем, что, с целью увеличения глубины контроля, оно содер- жит два блока памяти, мультиплексор, регистр записи реакций, два элемента НЕ, два элемента 2И-ИЛИ-НЕ и блок выявления неисправности, содержащий m элементов И (где m - длина вектора . тестового воздействия), элемент НЕ и триггер ошибки, причем первая и вторая группы информационных входов мультиплексора соединены с группой выходов контролируемого цифрового блока, а также с группой выходов генератора тестов и группой информа-V ционных входов контролируемого цифрового блока соответственно, первая и вторая группы выходов мультиплексора соединены с первой и второй группами синхровходов соответствующих раз- рядов регистра записи реакции, единичные входы всех разрядов регистра записи реакции подключены к щине еди- ничного потенциала . устройства, к шине нулевого потенциала которого

подключены нулевые входы всех разрядов регистра записи ре:акции, первая группа вько дов которого соединена с первыми входами элементов И и с первой группой информационных входов первого блока памяти, группа выходов которого соединена с второй группой информационных входов блока индикации, третья группа информационных входов которого соединена с группой выходов второго блока памяти, первая группа информационных входов которого соединена с второй группой выходов регистра записи реакции и с вторыми входами ю элементов И, выходы которых соединены с первым входом логического условия блока синхронизации, с единичным входом триггера ошибки и через элемент НЕ блока выявления неисправности - с нулевым входом триггера ошибки, выход которого сое- дииен с информационным входом блока индикации и является выходом признака ошибки устройства, вторые группы информационных входов первого и второго блоков памяти соединены с группой выходов контрольных точек контролируемого цифрового блока, адресные входы первого и второго блоков памяти соединены с входом ра.зрешения на ин- дикацию устройства, с первыми входами первых элементов И п€;рвого и второго элементов 2И-ИЛИ-НЕ и через первый

элемент НЕ - с первыми входами вторы элементов И первого и второго элементов 2И-ИЛИ-НЕ, выходы которых соединены с входами синхронизации первого и второго блоков памяти, вторые входы первых -элементов И первого и второго элементов 2И-ИЛИ-НЕ соединены с вторым выходом блока синхронизации, третий выход которого соединен с инверсным нулевым входом сброса регистра записи реакции, вторые вход вторых элементов И первого и второго элементов 2И-ИЛИ-НЕ соедийены с входами запроса на индикацию тестового воздействия и отклика устройства, при этом четвертый выход блока синхронизации соединен с инверсным К .содо сброса триггера ошибки, вход синхронизации которого соединен с первым выходом блока синхронизации, инверсные разрядные выходы счетчика соединены с управляющими входами первой и второй групп мультиплексора, а первый разряд счетчика соединен с инверсным входом разрешения передачи первой группы информационных входов мультиплексора и через второй элемент НЕ - с входом разрешения передачи второй группы информационных входов мультиплексора, второй вход логического условия блока синхронизации соединен с шиной задания режима работы устройства.

, J

YS

37

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1983 |

|

SU1166115A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

Изобретение относится к области автоматики .и. вычислительной техники и может быть использочано для контроля цифровых блоков. Цэль изобретения - увеличение глубины контроля. Устройство содержит мультиплексор, счетчик, генератор тестов, блок синхронизации, блок индикации, блок ти, регистр записи реакций, два.элемента НЕ, два селектора и блок выявления неисправности. Через мультиплексор тестовая информация и выходная информация контролируемого циф рового блока кода поступает в регистр записи реакции, а через него - в блоки памяти, куда также записывается информация, снимаемая с контрольных точек цифрового блока. Мультиплексор управляется счетчиком, ошибка фиксируется в блоке выделения неисправности. 3 ил.

Редактор Н. Яцола

Составитель Л. Сиротская

Техред И.Попович Корректор Е. Рошко

Заказ 5123/47 Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, МОСКВА, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля синхронизаторов | 1978 |

|

SU730133A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1166115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-01-31—Подача