Изобретение относится к области вычислительной техники и может быть использовано для контроля синхронных последовательностей импульсов.

Известно устройство для контроля синхронизатора, содержащее элементы И, ИЛИ и триггер, в котором обнаруживаются ошибки в последовательности импульсов 1.

Недостатком устройства является возможность контроля только одной последовательности импульсов.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для контроля синхронизаторов, содержащее два элемента ИЛИ, элемент И, элемент аадержки и триггер. Входы первого элемента ИЛИ соединены с шинами нечетных импульсов контролируемой последовательности, входы второго элемента ИЛИ - с шинами четных импульсов .контролируемой последовательности, .выход первого элемента ИЛИ соединен со счетным входом триггера, инверсный выход которого соединен с первым входом элемента И, выход второго элемента ИЛИ - со вторым входом элемента И и элементом задержки, выход которого соединен с нулевым входом триггера, а выход элемента И - с шиной контроля 2.

Недостатком устройства является возможность контроля только одной последовательности импульсов, с ростом же числа контролируемых последовательностей количество оборудования увеличивается практически линейно. Для современных ЭВМ характерно наличие значительного

10 числа синхронных последовательностей.

Целью изобретения является сокращение количества оборудования при контроле большого числа синхронизаторов.

Поставленная цель достигается тем, что

15 в устройство для контроля синхронизаторов, содержащее первый и второй элементы ИЛР1, группу элементов задержки, группу триггеров фиксации состояний, первый и второй элементы И, причем выходы каждого триггера фиксации состояний группы образуют группу выходов устройства, введены первая и вторая группы схем сравнения и дешифратор. Входы схем сравнения первой группы соединены с первыми

25 выходами контролируемых синхронизаторов, входы схем сравнения второй группы - со вторыми выходами контролируемых синхронизаторов. Первый и второй выходы первого контролируемого синхронизатора

соединены соответственно с первым и вторым входом дешифратора. Выходы всех схем сравнения первой группы соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с третьим входом дешифратора, выходы всех схем сравнения второй группы - с соответствуюш,ими входами второго элемента ИЛИ, выход которого соединен с четвертым входом дешифратора. Первый, второй, третий и четвертый выходы дешифратора соединены с первыми входами соответствуюш;их триггеров фиксации состояний группы и через соответствуюш,ие элементы задержки со вторыми входами триггеров фиксаций состояний группы. Первый, второй и третий упр авляющий входы устройства соединены соответственно с первым и вторым входами первого элемента И и с первым входом второго элемента И. Выход первого элемента И соединен со вторым входом второго элемента И, выход которого соединен с установочным входом всех триггеров фиксации состояний группы.

При контроле значительного числа синхросерий (до 16-18), что характерно для современных ЭВМ, достигается выигрыш в количестве оборудования в 1,5-2 раза.

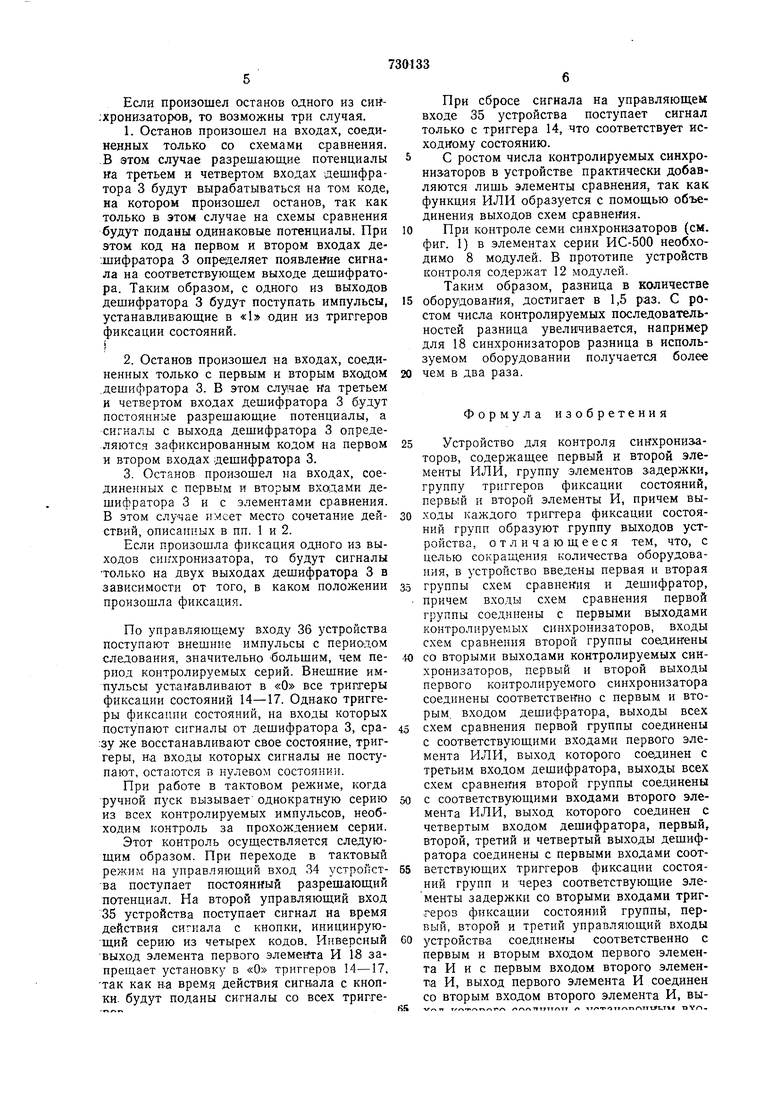

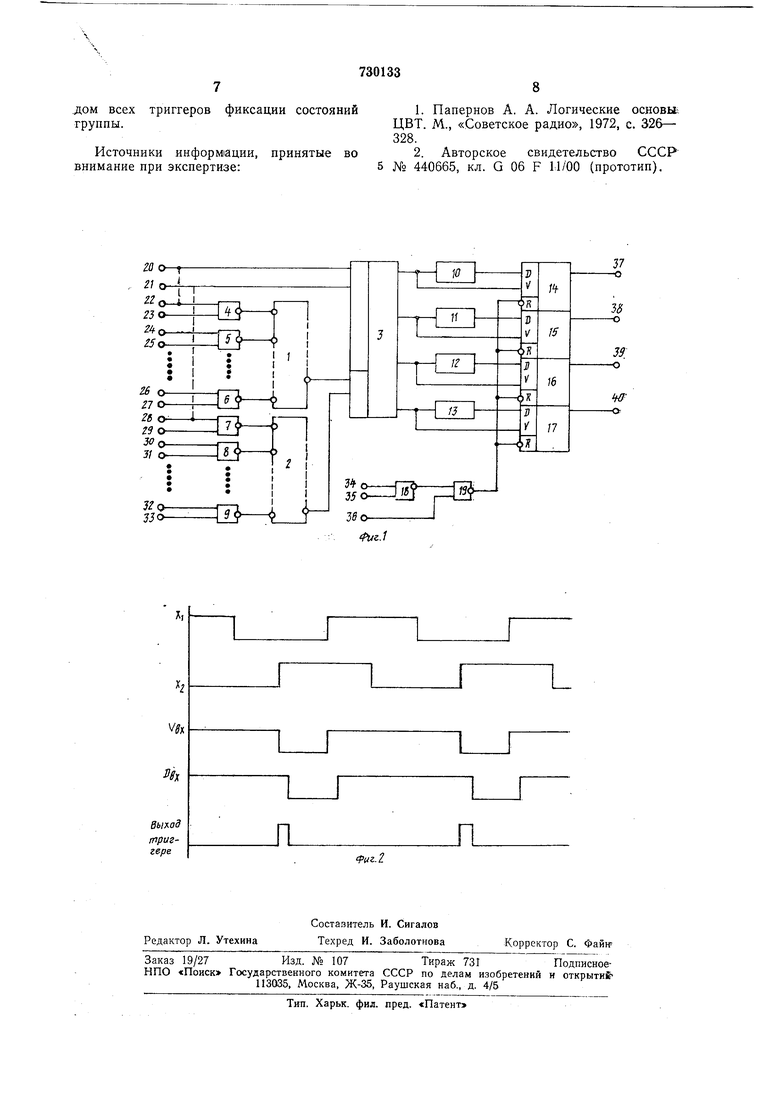

На фиг. 1 представлена схема предлагаемого устройства; иа фиг. 2 - временная диаграмма его работы.

Устройство содерлсит элементы ИЛИ 1, 2, дешифратор 3, первую группу схем сравнения 4-6 и вторую группу схем сравнения 7-9 группу элементов задержки 10-13, группу триггеров фиксации состояний 14- 17, первый и второй элементы И 18, 19, выходы синхронизаторов 20-33, первый, второй и третий управляюш,ие входы устройства 34-36; группа выходов 37-40 устройства.

Устройство для контроля синхронизаторов работает следующим образом.

С выходов синхронизаторов 20-33 на вход дешифратора 3 и входы схем сравнения первой и второй группы 4-9 поступают синхросигналы. На фиг. 2 показана одна пара синхросигналов (Xi, Х), причем сочетание их состояний подчинено последовательности 00, 01, 11, 10.

С выходов 37-40 устройства поступают сигналы контроля.

Устройство выполняет следующие функции.

1.При синхронном поступлении синхросигналов должны быть единичные сигналы от четырех триггеров фиксации состояний. На фиг. 2 в качестве примера показаны импульсы на входах и выходах одного

триггера.

2.При отсутствии импульсов от любого синхронизатора (фиксация Х и Хз) на контроль должен поступить единичный сигнал от одного из триггеров, фиксации состояний в зависимости от зафиксирован3.При отсутствии части импульсов от любого синхронизатора (фиксация либо i, либо Х2) на контроль должны поступать единичные сигналы от двух триггеров фиксации состояний в зависимости от зафиксированного состояния Xi или Ху.

4.При выходе из строя нескольких синхронизаторов возможен случай отсутствия единичных сигналов со всех триггеров фиксации состояний.

Ситуация, описанная в п. 2, может возникнуть как в результате выхода из строя синхронизатора, так и при настройке с использованием ручного шагового режима.

В этом случае, меняя последовательно коды в выбранном синхрониз аторе, можно следить за изменением последовательности сигналов этого синхронизатора, поскольку в этом случае контроль будет автоматически относиться к тому синхронизатору, который находится в шаговом режиме.

Шаговый режим может быть двух тигюв.

1.Импульсный режим, когда с приходом каждого внешнего сигнала с контролируемого синхронизатора поступает следующий по порядку код.

2.Тактовый режим, когда с приходом каждого внешнего сигнала с контролируемого синхронизатора поступают последовательно все четыре кода, при этом осуществляется контроль за их прохождением.

Сигналы Xi с первых выходов 22-27 синхронизаторов поступают на входы первой группы схем сравнения 4-6, а сигдалы Лг со вторых выходов 28-33 синхронизаторов поступают на входы второй группы схем сравнения 7-9. Число сиихропизаторов Может быть увеличено, что вызовет лишь увеличения числа схем сравнения. На первый и второй вход дешифратора 3 поступают си.гналы Х, Х с выходов 20, 21 нечетного синхронизатора. Если

число синхронизаторов четное, первый и второй входы дешифратора 3 должны быть соединены с аналогичными выходами любого синхронизатора (на фиг. 1 они соединены с выходами 22 и 28).

Если сигналы поступают в фазе, то с выходов схем сравнения будут поступать через четыре элемента ИЛИ 1 и 2 разрешающие (по схеме И) потенциалы на третий и четвертый входы дешифратора 3, что

позволяет производить дешифрацию сигналов, поступающих н.а первый и второй входы дешифратора 3.

С выходов дешифратора 3 будут поступать импульсы на У-входы триггеров 14-

17. На /}-входы триггеров поступают эти же импульсы через элементы задержки 10-13, что позволяет надежно производить запись «1 в эти триггеры. В качестве задержки используются два каскада усилиЕсли произошел останов одного из cnii:хронизаторов, то возможны три случая. 1.Останов произошел на входах, соединенных только со схемами сравнения. -В этом случае разрешающие потенциалы на третьем и четвертом входах дешифратора 3 будут вырабатываться на том коде, на котором произошел останов, так как только в этом случае на схемы сравнения будут поданы одинаковые потенциалы. При этом код на первом и втором входах де-шифратора 3 определяет появление сигнала на соответствуюш.ем выходе дешифратора. Таким образом, с одного из выходов дешифратора 3 будут поступать импульсы, устанавливающие в «1 один из триггеров фиксации состояний. 2.Останов произошел на входах, соединенных только с первым и вторым входом .деши41ратора 3. В этом случае на третьем и четвертом входах дешифратора 3 будут постоянные разрешающие потенциалы, а сигналы с выхода дешифратора 3 определяются зафиксированным кодом на первом и втором входах дешифратора 3. 3.Останов произошел на входах, соединенных с первым и вторым входами дешифратора 3 и с элементами сравнения. В этом случае имеет место сочетание действий, описанных в пп. 1 и 2. Если произошла фиксация одного из выходов сиьхронизатора, то будут сигналы только на двух выходах дешифратора 3 в зависимости от того, в каком положении произошла фиксация. По управляющему входу 36 устройства поступают внешние импульсы с периодом следования, значительно большим, чем период контролируемых серий. Внешние импульсы устанавливают в «О все триггеры фиксации состояний 14-17. Однако триггеры фиксации состояний, на входы которых поступают сигналы от дешифратора 3, ераЗУ же восстанавливают свое состояние, триггеры, н,а входы которых сигналы не поступают, остаются в нулевом состоянии. При работе в тактовом режиме, когда ручной пуск вызывает однократную серию из всех контролируемых импульсов, необходим контроль за прохождением серии. Этот контроль осуществляется следующим образом. При переходе в тактовый режим на управляющий вход 34 устройства поступает постоянный разреш.ающий потенциал. На второй управляющий вход 35 устройства поступает сигнал на время действия сигнала с кнопки, инициирующий серию из четырех кодов. Инверсный выход элемента первого элемента И 18 запрещает установку в «О триггеров 14-17, так как на время действия сигнала с кнопки, будут поданы сигналы со всех триггеПри сбросе сигнала на управляющем входе 35 устройства поступает сигнал только с триггера 14, что соответствует исходному состоянию. С ростом числа контролируемых синхронизаторов в устройстве практически добавляются лишь элементы сравнения, так как функция ИЛИ образуется с помощью объединения выходов схем сравнения. При контроле семи синхронизаторов (см. фиг. 1) в элементах серии ИС-500 необходимо 8 модулей. В прототипе устройств контроля содержат 12 модулей. Таким образом, разница в количестве оборудования, достигает в 1,5 раз. С ростом числа контролируемых последовательностей разница увеличивается, например для 18 синхронизаторов разница в используемом оборудовании получается более чем в два раза. Формула изобретения Устройство для контроля синхронизаторов, содержащее первый и второй элементы ИЛИ, группу элементов з-адержки, группу триггеров фиксации состояний, первый и второй элементы И, причем выходы каждого триггера фиксации состояний групп образуют группу выходов устройства, отличающееся тем, что, с целью сокращения количества оборудования, в устройство введены первая и вторая группы схем сравнения и дешифратор, причем входы схем сравнения первой группы соединены с первыми выходами контролируемых синхронизаторов, входы схем сравнения второй группы соединены со вторыми выходами контролируемых синхронизаторов, первый и второй выходы первого контролируемого синхронизатора соединены соответственно с первым и вторым, входом дешифратора, выходы всех схем сравнения первой группы соединены с соответствуюшими входами первого элемента ИЛИ, выход которого соединен с третьим входом дешифратора, выходы всех схем сравнения второй группы соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с четвертым входом дешифратора, первый, второй, третий и четвертый выходы дещифратора соединены с первыми входами соответствующих триггеров фиксации состояний групп и через соответствующие элементы задержки со вторыми входами триг.героз фиксации состояний группы, первый, второй и третий управляющий входы устройства соединены соответственно с первым и вторым входом первого элемента И и с первым входом второго элемента И, выход первого элемента И соединен со вторым входом второго элемента И, выдом всех триггеров фиксации состояний группы.

Источники информ1ации, принятые во внимание при экспертизе:

1.Папернов А. А. Логические основш ЦВТ. М., «Советское радио, 1972, с. 326- 328.

2.Авторское свидетельство СССР № 440665, кл. G 06 F Ы/00 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения сбоев синхронизируемых дискретных блоков | 1983 |

|

SU1125628A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для поиска перемежающихся неисправностей | 1985 |

|

SU1262502A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля синхронизаторов | 1984 |

|

SU1196872A1 |

| Устройство для контроля микропрограммного блока управления | 1984 |

|

SU1203526A1 |

| Устройство для диагностического контроля памяти | 1983 |

|

SU1161991A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1619280A1 |

Авторы

Даты

1982-01-07—Публикация

1978-10-03—Подача