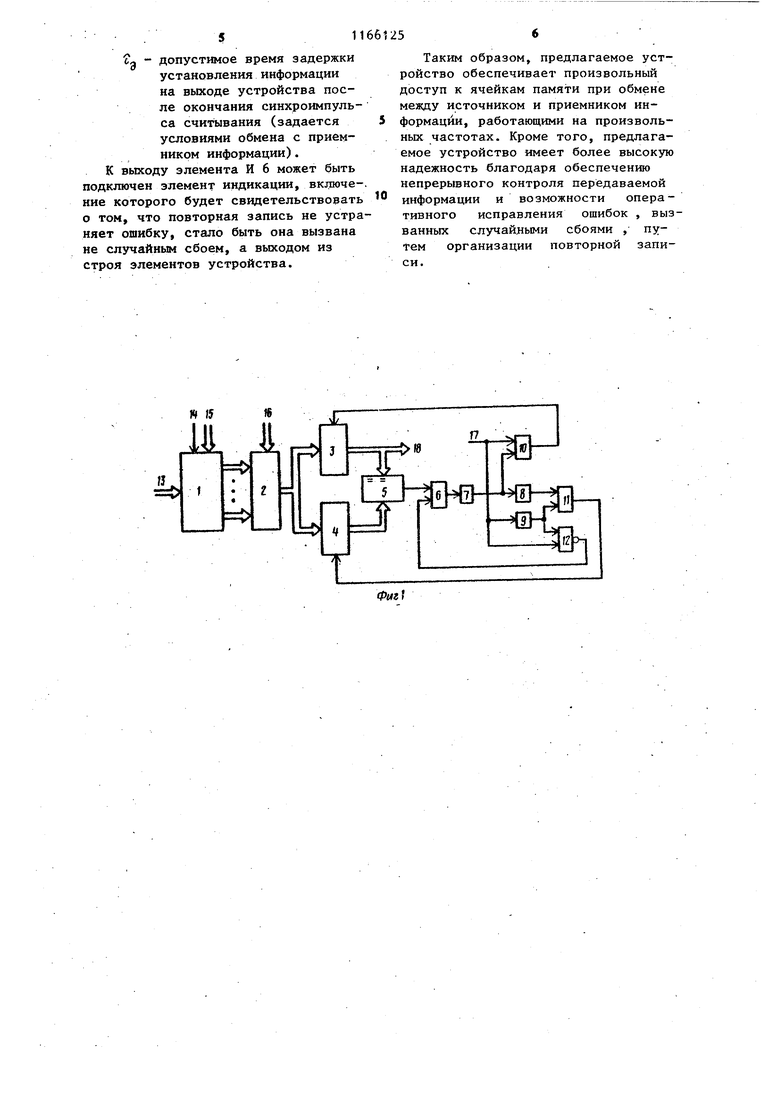

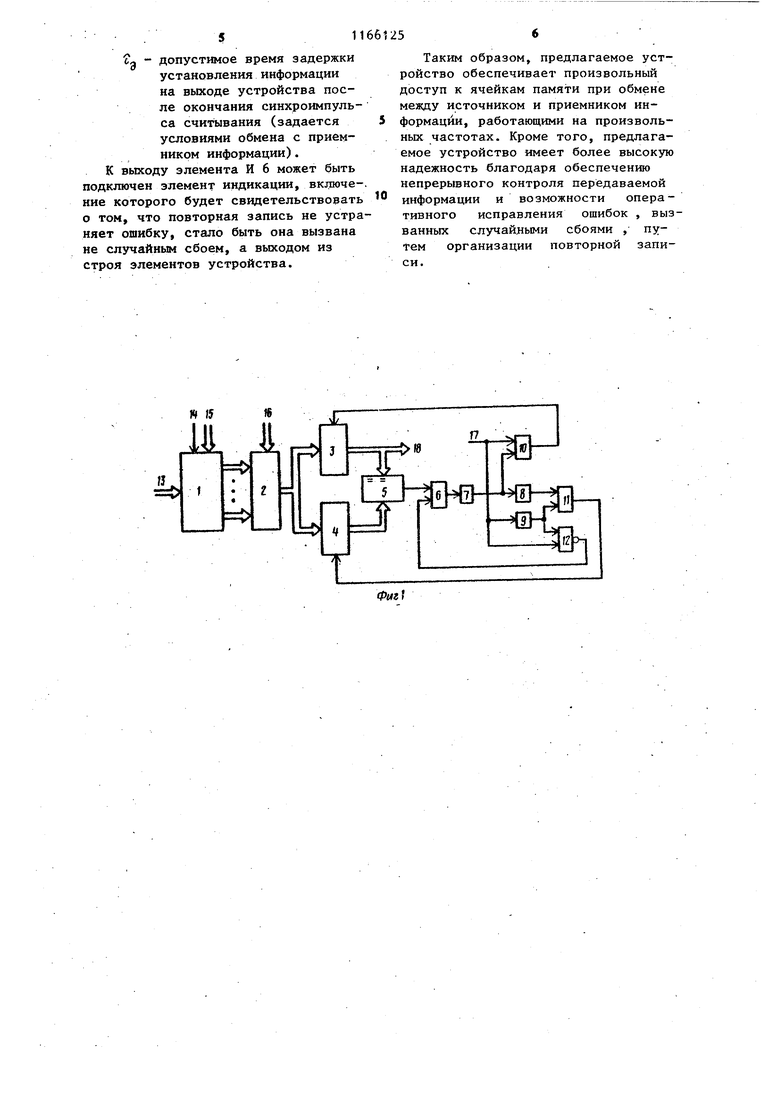

1 1 Изобретение относится к вычислительной технике и может быть исполь зовано в системах обмена данными в качестве устройства сопряжения различных по скоростным характеристикам источников и приемников инфор мации. .. Известно устройство для сопряжеНИН, содержащее триггер,- элементы И элемент ИЛИ, регистр сдвига, элемен НЕ, дешифратор адреса, формировател схему сравнения, дешифратор кода запроса, коммутатор каналов ij . К недостаткам этого устройства относятся низкое быстродействие. обусловленное необходимостью ожидания совпадения г1дресного кода требу емой информации с адресным кодом прин1 1аемойИнформации, а также невысокая, надежность из-за отсутствия контроля работы. Наиболее близким к изобретению по технической сущности является устройство для сопряжения, содержащее блок оперативной памяти, информационный вход которого является ин формационньм входом устройства, адресный вход подключен к выходам элементов ШШ группы, вход синхрони зации записи через элемент задержки записи подключен к входу синхронизации записи устройства, суммирующим входам счетчика записи и ревер сивного счетчика и первому входу триггера, а выход - к информационно . му входу коммутатора чтения, выход которого является информационным выходом устройства, а управляющий вход через элемент задержки считыва ния соединен с входом синхронизации .считывания, вторым входом триггера, суммирующим входом счетчика записи и вычитающим -входом реверсивного счетчика, выход которого через дешифратор нуля соединен с блокирующим входом элементов И первой группы, группы входов элементов И первой и второй групп подключены соответственно к выходам счетчика считьшания и счетчика записи, управляющие входы - соответственно к перво му и второму выходам триггера, а вьпсоды - соответственно к входам элементов ИЛИ группы . Недостаток известного устройства .состоит в ограниченной области при,менеиия, так как устройство не обес печивает доступ к произвольным ячей 2 кам блока оперативной памяти при записи и считывании информации. Цельюизобретения является расширение области применения устройства. Поставленная цель достигается тем, что в устройство, содержащее блок оперативной памяти, информационный вход которого является информационным входом устройства, а группа выходов соединена с группой информационных входов коммутатора, первый элемент задержки и второй элемент задержки, вход которого соединен с входом синхронизации считывания устройства, введены два регистра, схема сравнения, элемент И, формирователь импульсов, два .элемента ИЛИ и элемент ИЛИ-НЕ, при чем адресный вход и вход синхрониза ции блока оперативной памяти являются соответственно адресным входом записи и входом синхронизации записи устройства, адресный вход коммутатора является адресным входом считывания устройства, а выход соединен с информационными входами первого и второго регистров, синхровходы которых подключены соответственно к выходам первого и второго элементов ИЛИ, а выходы - соответственно к первому и второму входам схемы сравнения, выходом соединенной с первым входом элемента И, выход которого подключен к входу формирователя импульсов, выходом соединенного с первым входом первого элемента ИЛИ и через первый элемент задержки - с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу второго элемента задержки и первому входу элемента Ш1И-НЕ, выход которого соединен с вторым входом элемента И, а второй вход - с вторым входом первого элемента ИЛИ и входом синхронизации считывания устройства, выход первого регистра является информационным выходом устройства. На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 временные диаграммы работы устройства (нумерация сигналов соответствует нумерации элементов, с вькодов которых данные сигнала снимаются). . Устройство содержит (фиг.1) блок 1 оперативной памяти, коммутатор 2, регистры 3 и 4, схему 5 сравнения, элемент И 6, формирователь 7 импуль-. са (одновибратор), элементы 8 и 9 задержки, элементы ИЛИ 10 и 11, эле мент ИЛИ-НЕ 1/, информационный вход 13, шину 14 входа синхронизации записи, шину 15 адресного входа запис шину 16 адресного входа .считывания, шину 17 входа синхронизации считывания, информационный выход 18 устройства. Устройство работает следующим об разом. Сигналом начала работы устройств служит включение питающего напряжения. При этом обнуляется блок 1 опе ративной памяти, построенный на основе регистров. Информация источника, принимаемая в виде параллельного кода на информационный вход 13, по синхроимпульсу записи, поступающему по шине 14, записывается в ячейку блока 1 оперативной памяти, определяемую кодом адреса записи, принимаемым по шине 15. . Приемник информации по шине 16 задает адрес опрашиваемой ячейки блока 1 оперативной памяти, в соответствии с которым информация данной ячейки поступает через коммутатор 2 на входы регистров 3 и 4. Запись информации в регистр 3 происхо дит по переднему фронту синхроимпул са считывания, который вьвдается при емником информации по шине 17 и через элемент ИЛИ 10 поступает на синхровход регистра 3. Запись информации в регистр 4 происходит по пе- реднему фронту задержанного синхроимпульса считывания, поступающего на синхровход регистра 4 через элемент задержки и элемент ИЛИ 11. При этом на выходе схемы 5 сравнения вырабатьшается импульс единичного .уровня, соответствующий несовпадению информации в регистрах 3 и 4. Начало этого импульса совпадает с передним фронтом синхроимпульса считывания, а окончание - с передним фронтом задержанного синхроимпульса считывания. На выходе элемента И 6 поддерживается нулевой уровень, так как оЯ блокируется сигналом нулевого уровня с выхода элемента ИЛИ-НЕ 12 на время от момента начала синхроимпульса считывания до момента окон чания задержанного синхроимпульса считывания. Ввиду того, что источник и приемник информации могут работать на произвольных частотах, неизбежно возникновение ситуаций, при которых запись информации в одну из ячеек блока 1 оперативной памяти происходит во время вывода информации данной ячейки для записи ее в регистры 3 и 4. Если при этом передний фронт синхроимпульса считывания совпадает по времени с переходным процессом, возникающим в опрашиваемой ячейке в момент смены информации, то в регистр 3 записывается искаженная информация (фиг.2а), тогда как в регистр 4, в данном случае, запись происходит после окончания переходного процесса. В результате этого сигнал несравнения удерживается на выходе схемы 5 сравнения после записи информации в регистр 4. После окончания задержанного синхроимпульса считывания сигнал с выхода схемы 5 сравнения через элемент И 6 поступает на вход одновибратора 7. По переднему фронту этого сигнала одновибратор 7 вырабатывает импульс, равный по длительности синхроимпульсу считывания, который через элемент ИЛИ 10 поступает на синхровход ре гистра 3, а также через элемент 8 задержки и элемент ИЛИ 11 - на синхровход регистра 4. Таким образом, осуществляется повторная запись, после которой в регистрах 3 и 4 оказывается правильная информация. На фиг.26 приведен случай, когда информация искажается при записи в регистр 4. При этом также происходит повторная запись. Кроме того, . при записи в один из регистров 3 или 4 информация может быть искажена результате воздействия импульсной помехи. И в этом случае аналогичным образом происходит исправление искаженной информации. Для нормальной работы устройства необходимо выдержать следующие вреенные соотношения: . - время задержки элемента В задержки; . q - время задержки элемента 9 задержки; ц- длительность переходного процесса или помехи, «не Длительность синхроимпульса считыванияJ

Cg - допустимое время задержки установления информации на выходе устройства после окончания синхроимпульса считывания (задается условиями обмена с приемником информации). К вькоду элемента И 6 может быть подключен элемент индикации, включе-. ние которого будет свидетельствовать о том, что повторная запись не устраняет ошибку, стало быть она вызвана не случайным сбоем, а выходом из строя элементов устройства.

Таким образом, предлагаемое устройство обеспечивает произвольный доступ к ячейкам памяти при обмене между источником и приемником информации, работающими на произвольных частотах. Кроме того, предлагаемое устройство имеет более высокую надежность благодаря обеспечению непрерывного контроля передаваемой информации и возможности оперативного исправления ошибок , вызванных случайными сбоями , путем организации повторной записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1275454A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1238093A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1580383A1 |

| Устройство для вывода информации на экран электронно-лучевой трубки | 1985 |

|

SU1312560A1 |

| Устройство для контроля записи информации в блоках памяти | 1981 |

|

SU949720A1 |

| Устройство для контроля записи информации в блоках памяти | 1982 |

|

SU1076954A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1403091A1 |

| Устройство для вывода графической информации | 1986 |

|

SU1403092A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401468A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА И ПРИЕМНИКА ИНФОРМАЦИИ, . содержащее блок оперативной памяти, информационный вход которого является информационным входом устройства, а группа выходов соединена с группой информационных входов коммутатора, первый элемент задержки и второй элемент задержки, вход которого соединен с входом синхронизации считывания устройства, отличающееся тем, что, с целью расширения области применения устройства, в него введены два регистра, схема сравнения, элемент И, формирователь импульсов, два элемента ИЛИ и элемент ИЛИ-НЕ, причем адресный вход и вход синхронизации блока оперативной памяти являются соответственно адресным входом записи устройства, адресный вход коммутатора является адресным входом считывания устройства, а выход соединен с информационными входами первого и второго регистров, синхровходы KOTopbtx подключены соответственно к выходам первого и второго элементов ИЖ, а выходы - соответс твенно к первому и второму входам схемы сравнения, выходом соединенной с первым входом элемента И, выход которого подключен к входу формирователя импульсов, выходом соединенного с первым входом первого элемента ИЛИ и через первый элемент задерж(Л ки - с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу второго элемента задержки и первому входу элемента U ШШ-НЕ, выход которого соединен с вторым входом элемента И, а второй вход - с вторым входом первого эле9 мента ИЛИ и входом синхронизации б считывания устройства, выход первого регистра является информационным выходом устройства.

(5

и. JL

J6 .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ ультразвуковой очистки изделий | 1976 |

|

SU636049A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения | 1978 |

|

SU752321A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-07—Публикация

1984-01-30—Подача