Изобретение, относится к вычислительной технике и может быть использовано в системах обмена данными в качестве устройства сопряжения различных по скоростным характеристикам источников и приемников информации.

При организации обмена между источником и приемником информации, работающими на произвольных частотах, возникает проблема исключения возмож- ности искажения- информации при одновременном воздействии на устройство сопряжения режимов записи и счить - вания. .

Цель изобретения - повьппение бы- стродействия устройства.

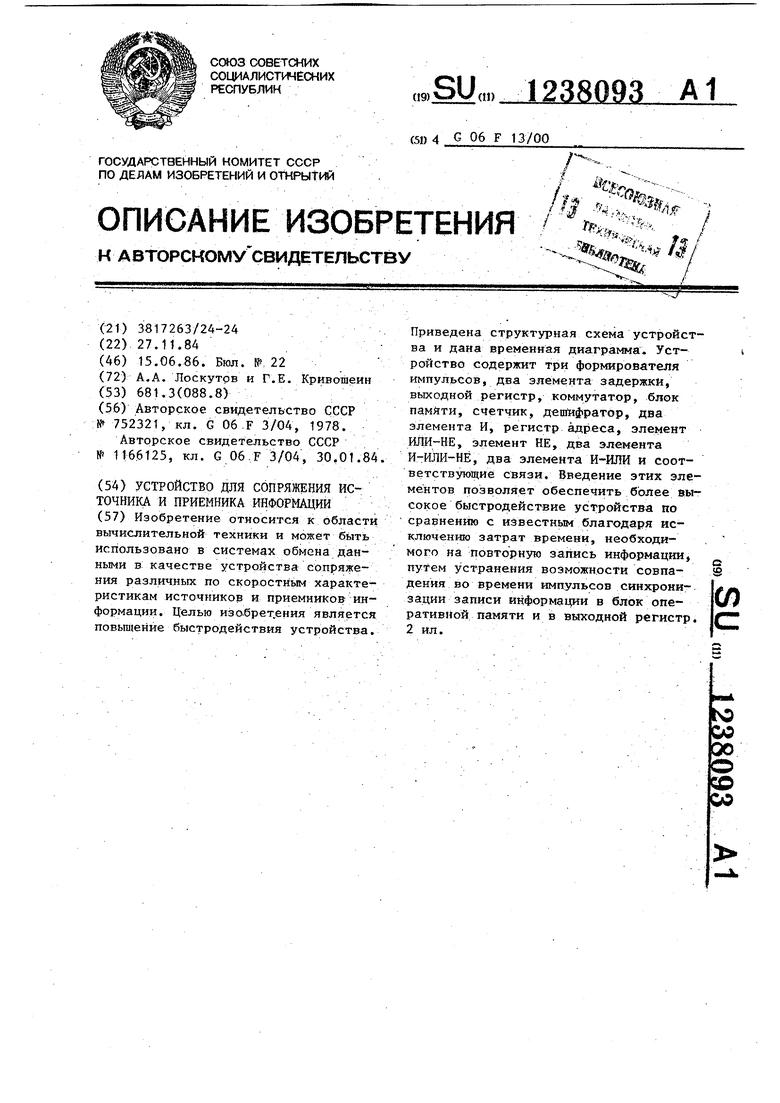

На фиг. 1 изображена функциональная схема предлагаемого устройства} на фиг, 2 - временная диаграмма фор- синхроимпульсов для записи информации в блок цамяти и в выходно регистр..

Устройство содержит (фиг.1) формирователи 1 и 2 импульсов, элемент ИЛИ-НЕ 3, второй элемент И-ИЛИ-НЕ 4, первый элемент И-ИЛИ-НЕ 5, элемент НЕ 6, элементы 7 и 8 заде.ржки, эле- менты И-ИЛИ 9 и 10, счетчик 11, блок- 12 памяти, дешифратор 13, регистр 14 адреса, коммутатор 15, формирователь 16 импульсов, элементы И 17 и 18, выходной регистр 19.

На фиг. 1 приняты также следующие обозначения : выход 20 идентификации записи источника инфо рмации5 инфбр- мационный выход 21 источника информации; тактовьй вьтход 22 считьшания приемника информации,; адресный выход 23 приемника информации; адресный выход 24 источника информации, информа- ционный вход 25 приемника информации.

Устройство работает следующим образом.

При включении питания устанавлива- roTCJFi в исходное состояние блок 12 .памяти, построенный на основе регистров, и счетчик 11. Информация источника, принимаемая в виде параллельного кода на его информационном выходе 21 записывается в ячейку блока 12 памяти, определяемую кодом адреса записи, вьщаваемую на адресном выходе 24 источника информации. Запись информации происходит по импульсу, поступающему на вход синхронизации записи блока 12 с выхода элемента И-ИЛИ 10, который вырабатывается на входе формирователя 2 импульсов по

переднему фронту входного синхроимпульса записи, поступающего на вход устройства. В зависимости от состояния триггера, собранного на элементах И-ИЛИ-НЕ 4 и 5, синхроимпульс пропускается или непосредственно с выхода формирователя 2 импульсов, или через элемент 8 задержки.

Считывание информации из устройства сопряжения приемником осуществляется последовательным кодом. В качестве примера рассматривают алгоритм считывания шестнадцатираз- рядной информации при восьмиразрядном адресном коде считывания (фиг.2).

Приемник информации вьщает на своем выходе двадцать две пачки из двадцатичетьфех синхроимпульсов. . Последовательный восьмиразрядньй адр.есньй код считывания с выхода 23 записывается в регистр 14 адреса по синхроимпульсам, поступающим на вход сдвига регистра 14 адреса через элемент И 18, который открывается сигналом с выхода дешифратора 13 только на время прохождения первых восьми синхроимпульсов. С выхода регистра 14 адреса принятый код ад.-. реса считывания поступает на адресный вход коммутатора 15,крторьй подключает к информационному входу вы ходного регистра 19 информацию с выхода соответствующей ячейки блока 12 .памяти. Сигнал с выхода дешифратора 13, поступающий на входы формирователей 1 и 16 импульсов, представляет собой дешифрацию Состояния счетчика 11 на восьмом такте. По переднему фронту этого сигнала на выходе- формирователя 16 импульсов вырабатывается сигнал разрешения парал- записи,, поступающ ш на вход V режима выходного регистра 19, а на выходе формирователя 1 импульсов вырабатывается импульс синхронизации параллельной записи. В зависимости от состояния триггера, собранного на элементах И-ИЛИ-НЕ 4 и 5, элемент И-ИЛИ 9 пропускает этот.импульс на вход С2 синхронизации параллельной записи выходного регистра 19 или непосредственно с выхода формирователя 1 импульсов, или через элемент 7 задержки. После осуществления параллельной записи информации в выходной регистр 19 на информационном выходе устройства выставляется информация шестнадцатого разряда.

Последовательная выдача информации из выходного регистра 19 осуществляется по заднему фронту импульсов считывания, которые поступают на вход С1 синхронизации вьосодного ре- гистра 19 через элемент И 17. На входе V выбора режима выходного регистра 19 в это время присутствует потенциал, соответствующий режиму сдвига. После окончания 24-синхроимпуль- са считывания счетчик 11 устанавливается в исходное состояние.

Если сигнал записи приходит во врмя действия сигнала считывания или наоборот, триггер остается в том же состоянии, какое он принял в момент поступления более раннего сигнала. В этом случае импульс, вырабатьшае- мый формирователем 1 или 2 импульсов сигнал на вход которого поступил раны ше, пропускается нeпocpe; cтвeннo с выхода данного формирователя импульса, а импульс с выхода другого формирователя импульсов пропускается через соответствующий элемент задерж ки. Вследствие этого исключается возможность искажения информации при перезаписи ее из блока 12 памяти в выходной регистр 19..

Формула изобретения

Устройство для сопряжения источника и приемника информации, содержащее первьй формирователь импульсов, элемент задержки, выходной регистр, коммутатор и блок памяти, информационный и адресный входы, которого соединены соответственно с информационным и адресным выходами источника информации, группа информационных выходов блока памяти подключена к группе информационных входов коммутатора, выход которого соединен с информационным входом выхо дного регистра, выход которого соединен с информационным входом приемника информации, вьпсод первого формирова- теля импульсов соединен с входом первого элемента задержки, отличающееся тем,что, с целью по- вышения быстродействия,в устройство введены счетчик, дешифратор, два элемента И, второй элемент задерж.ки, регистр адреса, элемент ИЛИ-НЕ, элемент НЕ, два элемента И-ИЛИ-НЕ,

два элемента И-ИЛИ и два формирователя импульсов, причем выход второ

5 ю

f520 :5

5

0

5

го формирователя импульсов соединен с входом второго элемента задержки, выход третьего формирователя импульсов соединен с регулирующим входом выходного регистра, первый и второй входы синхронизации которого соединены соответственно с вьтходами первого элемента И и первого элемента И-ИЛИ, первьй вход первого элемента И-ИЛИ соединен с выходом первого формирователя импульсов, второй вход первого элемента И-ИЛИ соединен с выходом первого элемента И-Ш1И-НЕ, с первым и вторым входами второго элемента И-ЙЛИ-НЕ и с первым входом второго элемента И-ИЛИ, выход которого соединен с входом управления записью блока памяти, выходы второго элемента задержки и второго формирователя импульсов соединены соответственно. с вторым и третьим входами второго элемента И-ИЛИ, четвертый вход которого соединен с выходом второго элемента И-ИЛИ-НЕ, с первым и вторым входами первого элемента И-КПИ-НЕ и с третьим входом первого элемента iИ-ИЛИ, четвертый вход ко.торого соединен с выходом первого элемента задержки, тактовьй выход приемника информации подключен к тактовому входу счетчика и к первым входам первого и второго элементов И,выход счетчика подключен к входу дешифратора, первый, второй и третий выходы которого соединены соответственно с входом третьего формирователя .импульсов, вторым входом первого элемента И, вторым входом второго элемента И, выход которого соединен с управляющим входом регистра адреса, информационный вход которого подключен к адресному выходу приемника информации, выход регистра адреса подключен к адресному входу коммута- тора, первьй выход дешифратора подсоединен к входу первого формирователя импульсов и к первому входу элемента ИЛИ-НЕ, выход которого через элемент

НЕ соединен с третьими входами первого и второго элементов И-ШТИ-НЕ, четвертый вход второго элемента И ИПИ-НЕ соединен с первым входом элемента ИЛИ-НЕ, второй вход которого подключен к четвертому входу первого элемента И-ИЛИ-НЕ к входу второго формирователя импульсов и к выходу идентификации записи источника информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1166125A1 |

| Устройство для сопряжения источника и приемника информации | 1987 |

|

SU1425695A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1275454A1 |

| Устройство для сопряжения | 1983 |

|

SU1104498A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1580383A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство для обработки видеоинформации | 1986 |

|

SU1322320A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах обмена данными 3 качестве устройства сопряжения различных по скоростным характеристикам источников и приемников информации. Целью изо.брет.ения является повышение быстродействия устройства. Приведена структурная схема устройства и дана временная диаграмма. Устройство содержит три формирователя импульсов, два элемента задержки, выходной регистр, коммутатор, блок памАти, счетчик, дептифратор, два элемента И, регистр адреса, элемент РШИ-НЕ, элемент НЕ, два элемента И-ИЛИ-НЁ, два элемента И-ИЛИ и соответствующие связи. Введение этих элементов позволяет обеспечить более высокое быстродействие устройства по сравнению с известным благодаря исключению затрат времени, необходимого на повторную запись информации, путем устранения возможности совпадения во времени импульсов синхронизации записи информации в блок оперативной памяти ив выходной регистр. 2 ил. § (Л S«r 00 эо 9 :о 00

Редактор С. Лисина

Составитель Г. Стериин Техред Л.Сердгокова

Заказ 3293/50Тираж 671

ВНЙИПИ Государственного комитета СССР

по делам изобретений и открытий . 113035,:Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

Корректор Л. Пилипеп чо,

Подписное

| Устройство для сопряжения | 1978 |

|

SU752321A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1166125A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-11-27—Подача