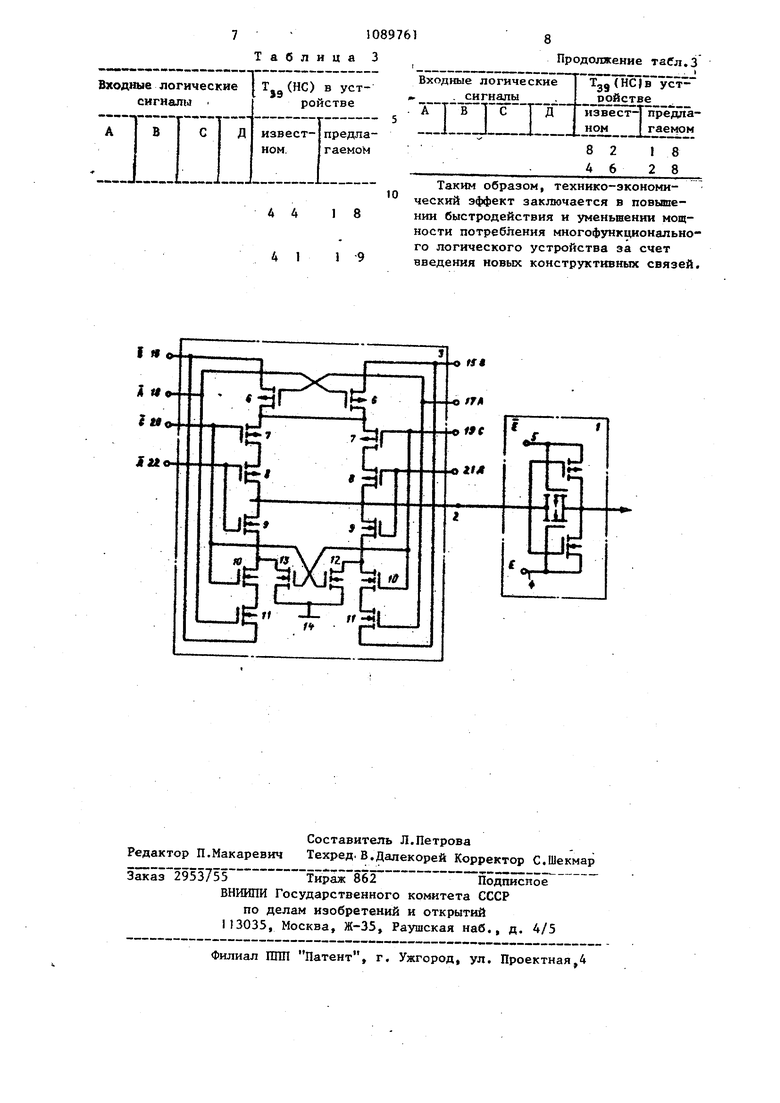

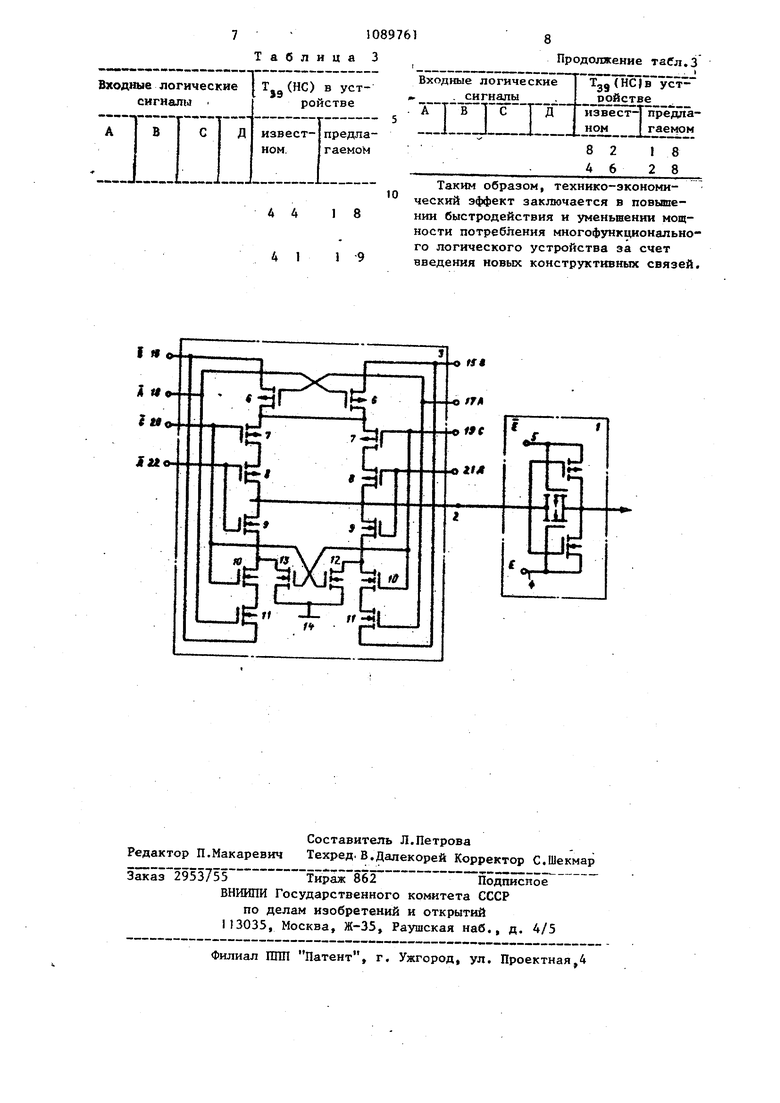

Изобретение относится к вычисли тельной технике, электронике автоматике и, в частности; мелеет исполь зоваться в интегральных схемах и ЁИ на МДП-транзисторах дсполияющсго тип проводимости, Известен многофункциональньш логический элемент, содержашлш элементы ИЛИ, формирователи с прямыми и инверсными входами и элемент ИЛ-1исключйтельно. Многофункциональный логический элемент выполнен на 22 ВДП-транзисторах, имеет четыре выход и семь входов Cl3. Недостатком устройства является низкое быстродействие из-за большого числа каскадов. Наиболее близким к предлагаемому по технической сущности является многофункциональное логическое устро ство, содержащее входные каскады и элемент разнозначности, выход которо го является выходом устройства а входы соответственно подключены; пер вьй - к выходу элемента И, второй - к ошне первого сигнала. Входными кас кадами являются два элемента равнозначности и элемент И, прячем входы первого и второго элементов равнозна чности подключены к соответствугоигим шинам информационных и паравляюпгих сигналов, а выходы -, к входам элемента И С2 . Недостатком устройства является низкое быстродействие, больншя потре бляемая мощность из-за ислользованкя ОДП-транзисторов одного типа проводимости. Цель изобретения - повышение (Зь::-стродействия и уменьшение потребляемой мощности. Для достижения поставленной цели в многофункциональном логическом уст ройстве, содержащем входной каскад и элемент равнозначности, выход которого подключен к выходной шине уст родства, а входы соответственно подключены: первьй - к выходу входного каскада, второй - к шине первого входного сигнала, третий - к гайке инверсии первого входного сигнала, входной каскад состоит из двух цепо чек, каждая из которых содер/кит шест последовательно включенных М.ДП-транзисторов дополняющего типа проводимости, и двух дополнительных п-канальных МДП транзиеторов, истоки котЬрых подключены к общей шине,.причем истоки первого р-канального МДП-тран зистора, и шестого п-канального МДПтр 1кзистора первой и второй цепочек подключены, соответственно, к шине второго входного сигнала и к шине инверсии второго входного сигнала, затвор шестого МДП-транзистора первой цепочки подключен к затвору первого -ЗДП-транзистора второй цепочки- и к шине третьего входного сигнала, затвор шестого МДП-транзистора второй цепочки подключен к. затвору первого МДП-транзистора первой цепочки и к шине инверсии третьего входного сигкала, сток первого МДП-транзистора первой цепочки подключен к стоку этого лее МДП-транзистора второй цепо.чки, затворы второго р-канального и пятого п-канального МДП-транзистороа первой цепочки подключены к шине четвертого входного сигнала, а затво ры этих же МДП-транзисторов второй цепочки к шине инверсии четвертого входного сигнала, затворы р-канального третьего и п-канального четвертого Ш Д-транзксторов первой цепочки подключены к шине пятого входного . сигнала, а затворы этих же М/Щ-транзисторов второй цепочки - к шине инверсии пятого входного сигнала, стоки зтих МДП-транзисторов первой и второй цепочек подключены к выходу входного каскада, сток первого дополнительного п-канального МДП-тран- зистора подключен к стоку пятого МДП--.гранзистора первой -цепочки, а его затвор - к шине инверсии четвертого входного сигнала, сток второго дополнительного п-канального МДПтранзистора подключен к стоку пятого 1-1,Щ1-транзистора второй цепочки, а его затвор - к шине четвертого входного сигнала., истоки дополнительных МДПтранзисторов соединены с общей шиной. На чертеже представлена электрическая принципиальная схема устройства. На схеме первьй вход элемента 1 раБисзиачности Г1од слючен к выходу 2 входного каскада 3, второй вход элемента 1 равнозначности подключен к тине 4 первого входного сигнала Е, а третий - к шине 5 инверсии первого входного сигнала Е. Выход элемента 1 равнозначности является выходом зстройства. Входной каскад 3 состоит из двух цепочек. каждая из которых содержит шесть последовательно включенных ЩП-транзистороз дополняющего типа

проводимости, первый, второй, третий МДП-транзисторы 6,7,8 - р-канальные I а четвертый, пятый, шестой МДП-транзисторы 9,10,11 - п-канальные, идвух дополнительных п-канальных МДП-транзисторов 12 и 13, истоки которых подключены к общей шине 14. Истоки первого и шестого МДП-транзисторов 6 и 11 первой цепочки, подключены к шине 15 второго входного сигнала В, Истоки первого и шестого МДП-транзисторов 6 и 11 второй цепочки подключены к шине 16 инверсии второго входного сигнала S. Затвор МДП-транзистора 11 первой цепочки подключен к затвору МДП-транзистора 6 второй цепочки и к шине 17 третьего входного сигнала А, Затвор МДП-транзистора 11 второй цепочки подключен к затвору ДП-транзистора 6 первой цепочки и к вчне 18 инверсии третьего входного сигнала А. Сток МДП-транзистора 6 первой цепочки подключен к стоку этого же МДП-транзистора второй цепочки. Затворы МДП-транзисторов 7 и 10 первой цепочки подключены к шине

19 четвертого входного сигнала С, а затворы этих .же МДП-транзисторов второй цепочки - к шине 20 инверсии четвертого входного сигнала С. Затворы МДП-транзисторов 8 и 9 первой цепочки подключены к шине 21 пятого входного сигнала Д, а затворы этих же МДПтранзисторов второй цепочки - к шине 22 инверсии пятого входного сигнала

Д. Стоки МДП-транзисторов 8 и 9 первой и второй цепочек подключены к выходу 2 входного каскада 3. Сток МДП-транзистора 12 подключен к стоку МДП-транзистора 10 первой цепочки, а

его затвор - к шине 20. Сток МДПтранэистора 13 подключен к стоку МДПтранзистора 10 второй цепочки, а его:затвор - к шине 19.

Устройство работает следующим образом.

На выходе устройства реализуются все переключательные фуикции двух переменных. Работу многофункционального логического устройства удобно

проишиострировать с помощью табл. I и 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический элемент | 1982 |

|

SU1016841A1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Логический элемент на КМДП-транзисторах | 1985 |

|

SU1262721A1 |

| Устройство согласования уровней напряжения /его варианты/ | 1983 |

|

SU1138940A1 |

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064470A1 |

| Сумматор по модулю два | 1984 |

|

SU1191906A1 |

| Логический элемент | 1982 |

|

SU1018250A1 |

| Логический элемент | 1981 |

|

SU997252A1 |

| Логический элемент на МДП-транзисторах | 1987 |

|

SU1480116A1 |

ГтоГОФУНКЩЮЯАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО, содержащее входной каскад и элемент равнозначности, выход которого подключен к выходной шине устройства, а входы соответственно. подключены: первый - к выходу входного каскада, второй -. к шине . первого входного сигнала, третий - к шине инверсии первого входного сигнала, отличающееся тем, что, с целью повьшения быстродействия и уменьшения потребляемой мощности, входной каскад состоит из двух цепочек, каждая из которых содержит шесть последовательно включенных МДП-транзисторов дополняющего типа проводимости, и двух дополнительных п-канальных МДП-транзисторов, истоки которых подключены к общей шине причем истоки первого р-канального МДПтранзистора и шестого п-канального ЩЩ транзж:тора первой и второй цепочек подключены соответственно к шине второго входного сигнала и гг.. шине инверсии второго входного скг нала, затвор исестого МДП-транзистора первой цепочки подключен к затвору первого МД11 туанзистора второй цепоч ки и к шине третьего входного сигнала, затвор шестого МДП-транзистора второй цепочки подключен к затвору первого МДП-транзистора первой цепочки и к шине инверсии третьего входного сигнала, сток первого ЩПтранзистора первой цепочки подключен к стоку этого же МДП-транзистора втр рой цепочки, затворы второго р-канального и пятого п-канального МДП транзисторов первой цепочки подключены к шине четвертого входного сигс е нала, а затворы этих же МДП-транзксторов второй цепочки - к шине инверсии четвертого входного сигналаj затворы р-канального третьего и пканального четвертого МДП-транзисторов первой цепочки подключены к шине пятого, входного сигнала, а затворы этих же (жни МДП транзисторов второй цепочки -я шине инверсии пятого входного сигнала, стоки этик МДП-транзисторов первой и второй цепочек подключены ч| к выходу входного каскада, сток первого дополнительного п-канального ЩЦ1-транзистора подключен к стоку З-ЕЯ пятого МДП-транзистора первой цепочки, а его затвор - к шине инверсии четвертого входного сигнала, сток второго дополнительного п-канального МДПтранзистора подключен к стоку пятого МДП-тран2истора второй цепочки, а его затвор к шине четвертого вход ного сигнала, истоки дополнительных МДП-транзисторов соединены с общей шиной.

О I 2 3

В 1 1 1

4 5 6 7 8 9 10

О В

Д

о о в в

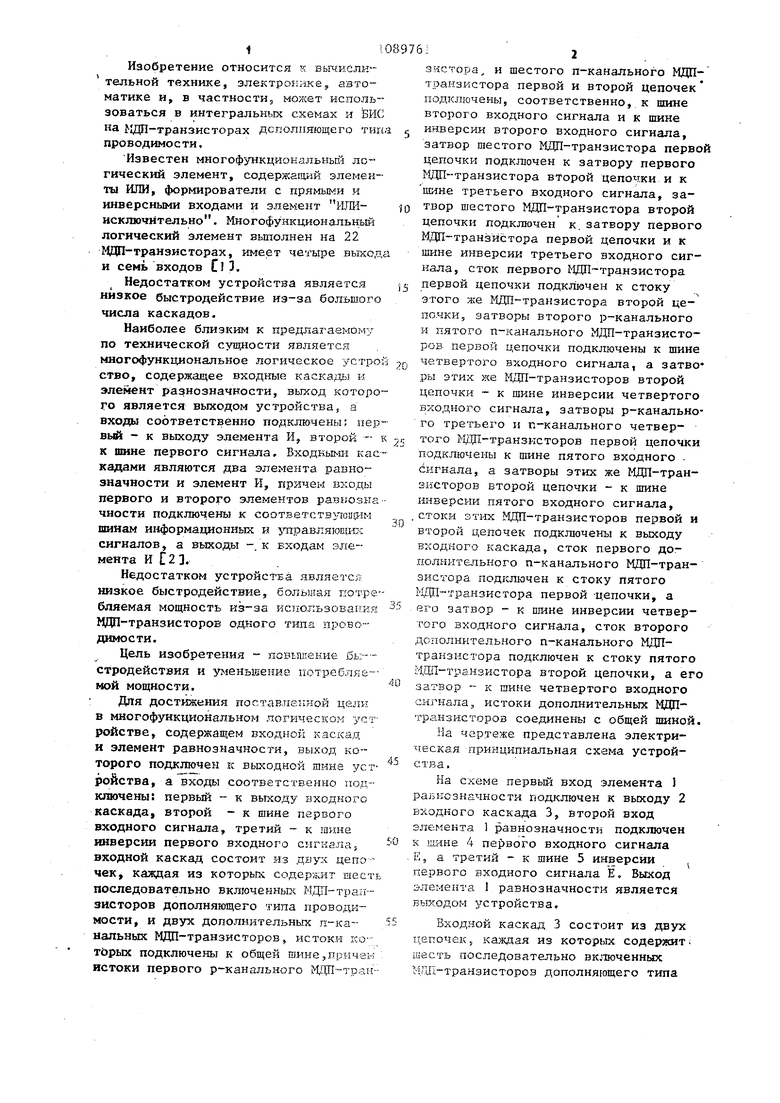

Таблица 1

о

о 1 I

вд вд в

I

5

1 1

вд

Д

о о 1 I 1

.

вд+вд в + Д в Д вд + вд в

Значения входных сигналов А, С, Е

Номер набора на шинах

.LA.

19

17

I

О О

Л О 1

1 В

д

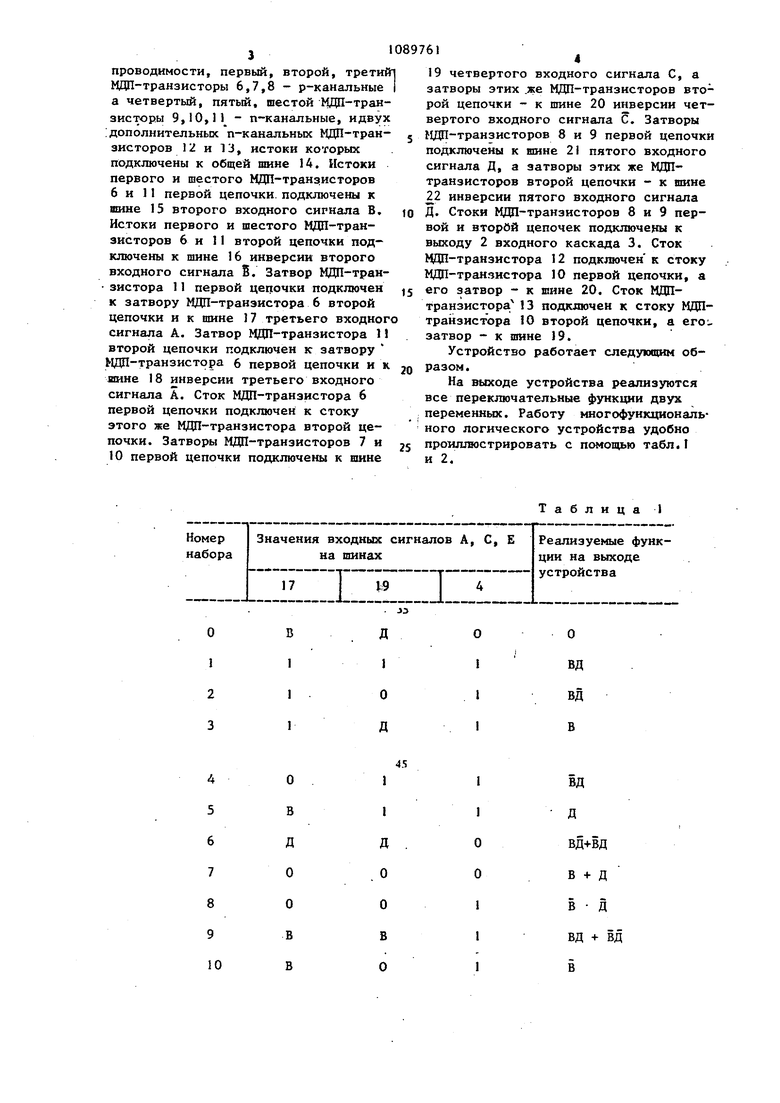

О0. О7,8 6,912 Табл.2 иллюстрирует реализацию функции F « ВД + ВД на шестом наборе сигналов табл.1. Таким образом, многофункциональное логическое устройство реализует 16 переключательных функций двух переменных. Так как быстродействие устройства зависит от времени перезаряда выходных емкостей через цепочки последовательно включенных МДП-транзисторов, то из-за меньшего числа каскадов, на

Продолжение табл, 1

Реализуемые функции иа выходе устройства

В + Д

Д

в + д в + д

}

Таблица 2

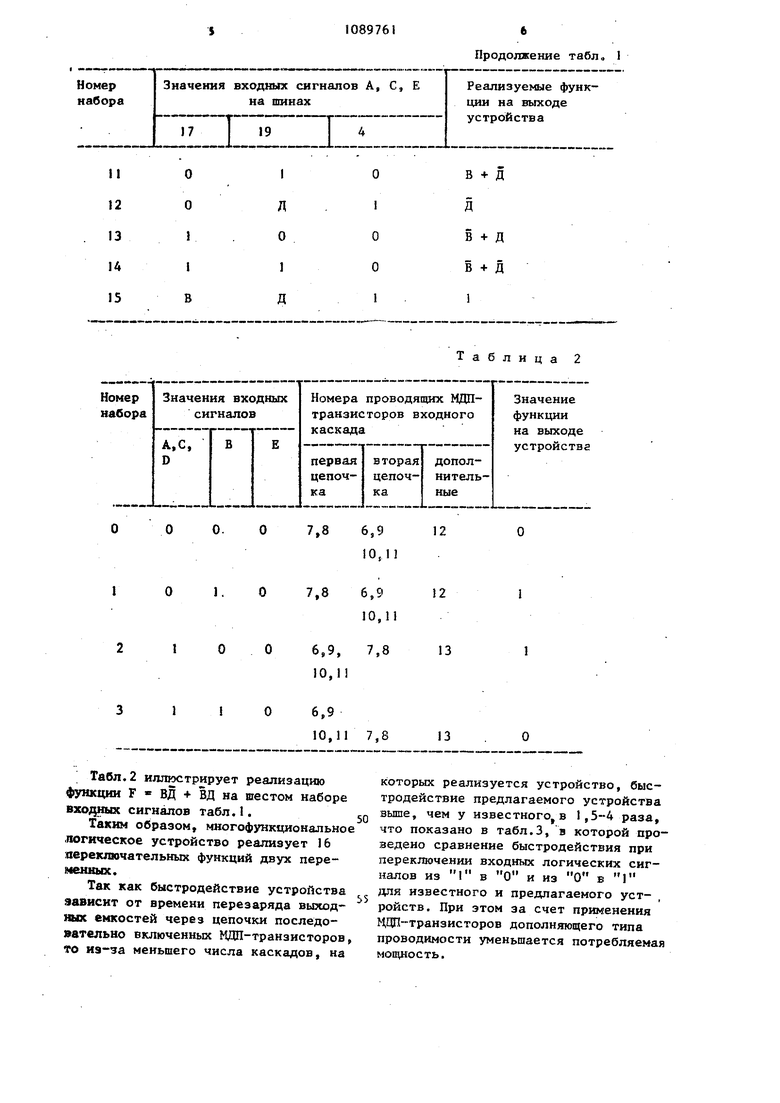

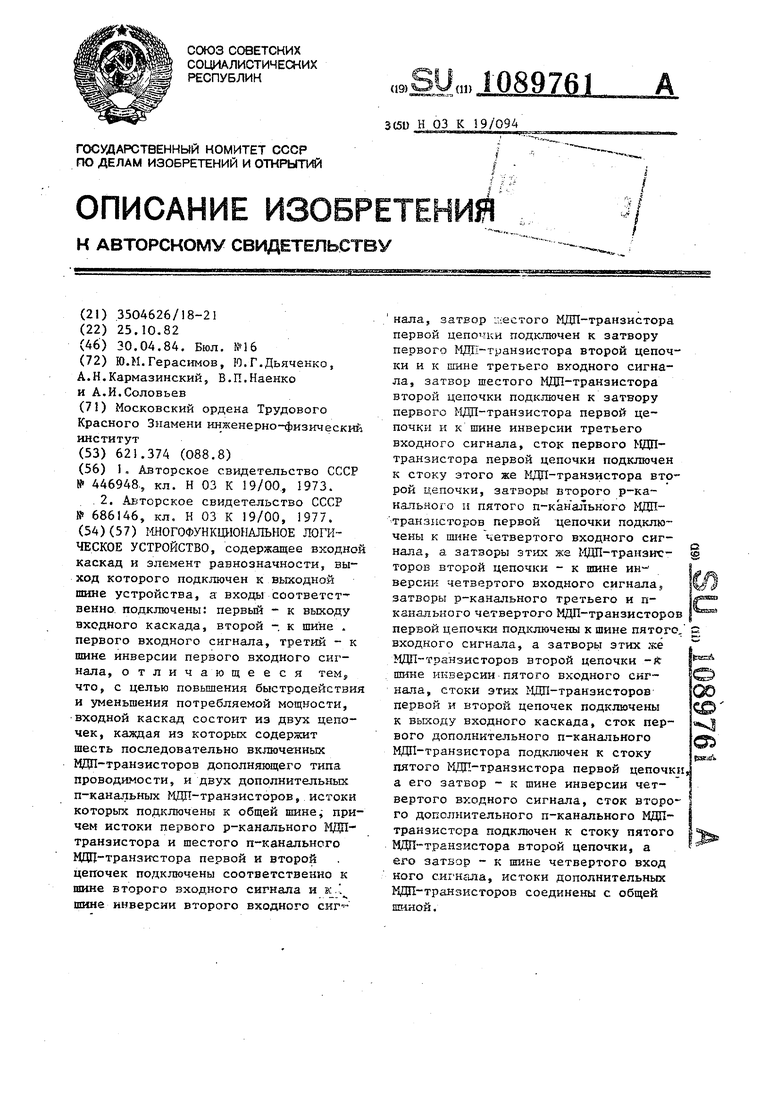

io,n которых реализуется устройство, быстродействие предлагаемого устройства выше, чем у известного в 1,5-4 раза, что показано в табл.3, в которой проведено сравнение быстродействия при переключении входных логических сигналов из 1 в О и из О в 1 для известного и предлагаемого устройств. При этом за счет прш енеиия НЦП-транзисторов дополняющего типа проводимости уменьшается потребляемая мощность.

7-1089761

Таблица 3

1 8

4 4

Продолжение табл.3

ческий эффект заключается в повьшении быстродействия и уменьшении мощности потребления многофункционального логического устройства за счет введения новых конструктивных связей.

| I, Авторское свидетельство СССР № 446948., кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многофункциональный логический элемент | 1977 |

|

SU686146A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-04-30—Публикация

1982-10-25—Подача