элемента ИЛИ-НЕ, к входам которого подключены выходы третьего и четвертого формирователей импульсов, при этом первым, вторым, третьим и четвертым входами устройства являются соответственно первый информационный вход первого блока анализа нечетных посылок, третий информационный вход первого блока анализа нечетных посылок, четвертый информационный вход первого блока анализа нечетных - посылок, который соединен с четвертым информационным входом второго блока анализа нечетных посылок, и второй информационный вход первого, блока анализа нечетных посылок, а выход четвертого элемента ИЛИ является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Тренажер радиотелеграфиста | 1983 |

|

SU1111195A1 |

| Устройство для отображения графической информации | 1988 |

|

SU1566339A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020825A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для определения максимальной гармоники спектра Уолша | 1984 |

|

SU1211751A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

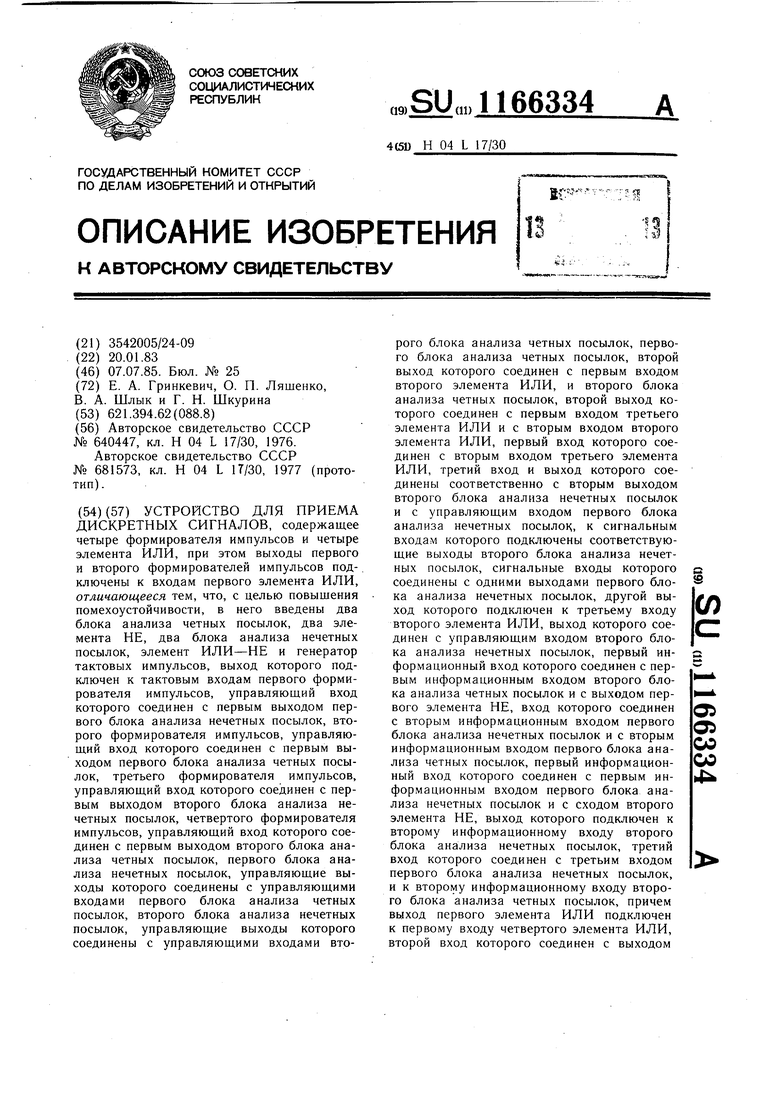

УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ, содержащее четыре формирователя импульсов и четыре элемента ИЛИ, при этом выходы первого и второго формирователей импульсов под-. ключены к входам первого элемента ИЛИ, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены два блока анализа четных посылок, два элемента НЕ, два блока анализа нечетных посылок, элемент ИЛИ-НЕ и генератор тактовых импульсов, выход которого подключен к тактовым входам первого формирователя импульсов, управляющий вход которого соединен с первым выходом первого блока анализа нечетных посылок, второго формирователя импульсов, управляющий вход которого соединен с первым выходом первого блока анализа четных посылок, третьего формирователя импульсов, управляющий вход которого соединен с первым выходом второго блока анализа нечетных посылок, четвертого формирователя импульсов, управляющий вход которого соединен с первым выходом второго блока анализа четных посылок, первого блока анализа нечетных посылок, управляющие выходы которого соединены с управляющими входами первого блока анализа четных посылок, второго блока анализа нечетных посылок, управляющие выходы которого соединены с управляющими входами второго блока анализа четных посылок, первого блока анализа четных посылок, второй выход которого соединен с первым входом второго элемента ИЛИ, и второго блока анализа четных посылок, второй выход которого соединен с первым входом третьего элемента ИЛИ и с вторым входом второго элемента ИЛИ, первый вход которого соединен с вторым входом третьего элемента ИЛИ, третий вход и выход которого соединены соответственно с вторым выходом второго блока анализа нечетных посылок и с управляющим входом первого блока анализа нечетных посылок, к сигнальным входам которого подключены соответствующие выходы второго блока анализа нечетных посылок, сигнальные входы которого I соединены с одними выходами первого блока анализа нечетных посылок, другой вы(Л ход которого подключен к третьему входу второго элемента ИЛИ, выход которого соединен с управляющим входом второго блока анализа нечетных посылок, первый информационный вход которого соединен с первым информационным входом второго блока анализа четных посылок и с выходом первого элемента НЕ, вход которого соединен О) с вторым информационным входом первого а блока анализа нечетных посылок и с вторым САд информационным входом первого блока анаОд 4 лиза четных посылок, первый информационный вход которого соединен с первым информационным входом первого блока анализа нечетных посылок и с сходом второго элемента НЕ, выход которого подключен к второму информационному входу второго блока анализа нечетных посылок, третий вход которого соединен с третьим входом первого блока анализа нечетных посылок, и к второму информационному входу второго блока анализа четных посылок, причем выход первого элемента ИЛИ подключен к первому входу четвертого элемента ИЛИ, второй вход которого соединен с выходом

1

Изобретение относится к технике передачи данных и может использоваться для приема дискретных сигналов в системах, работающих по двум параллельным каналам связи.

Цель изобретения - повышение помехоустойчивости.

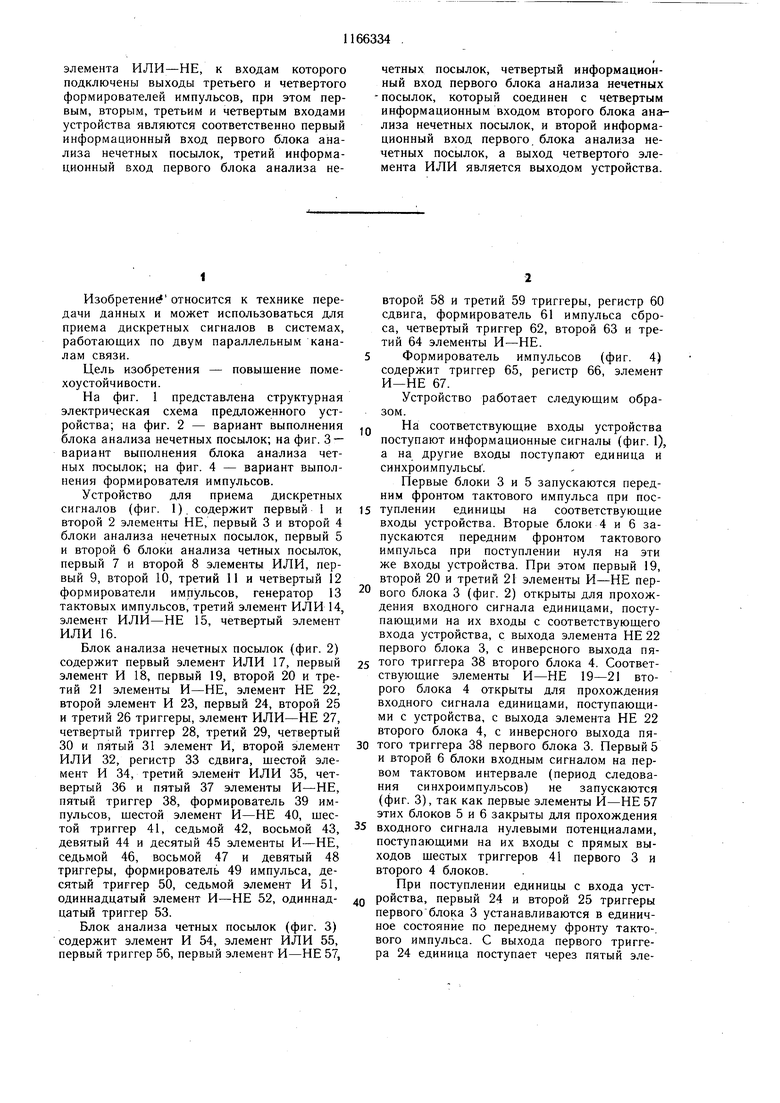

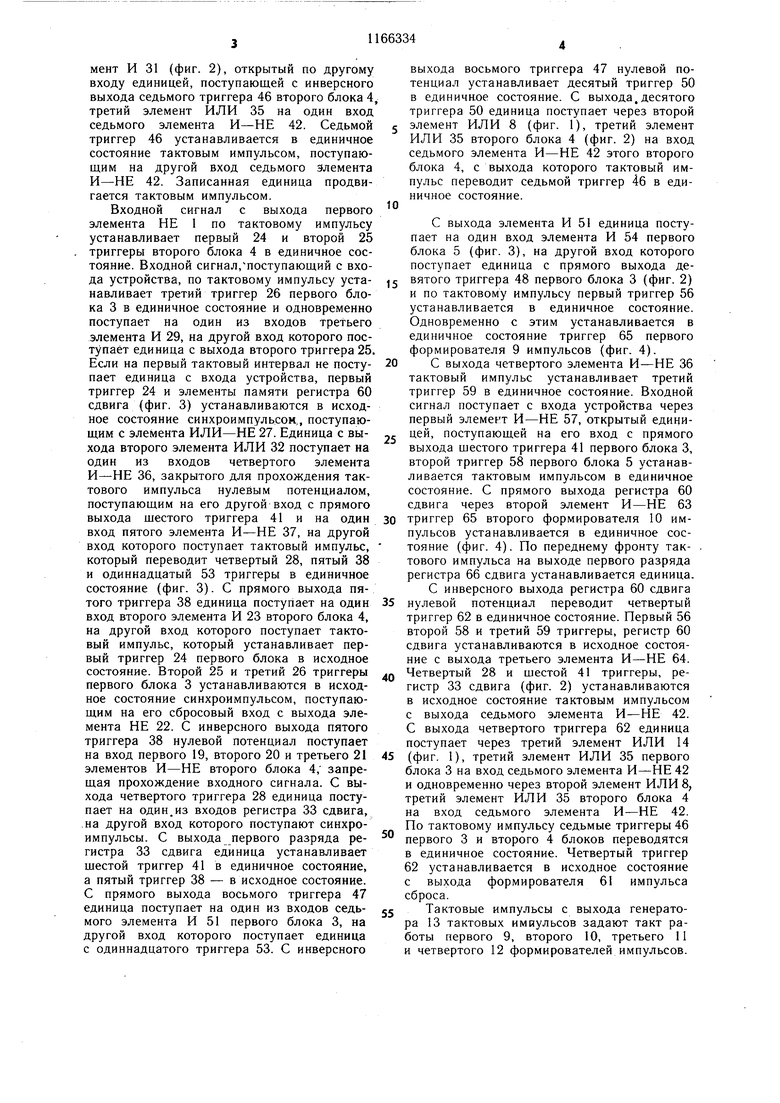

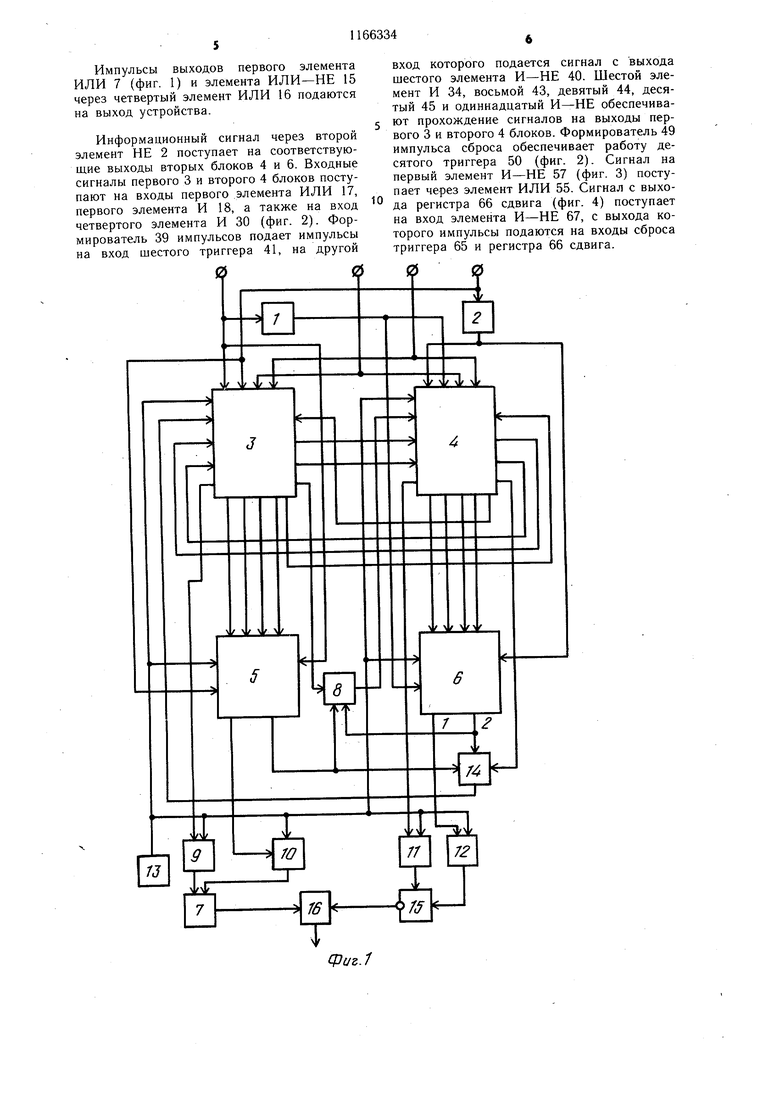

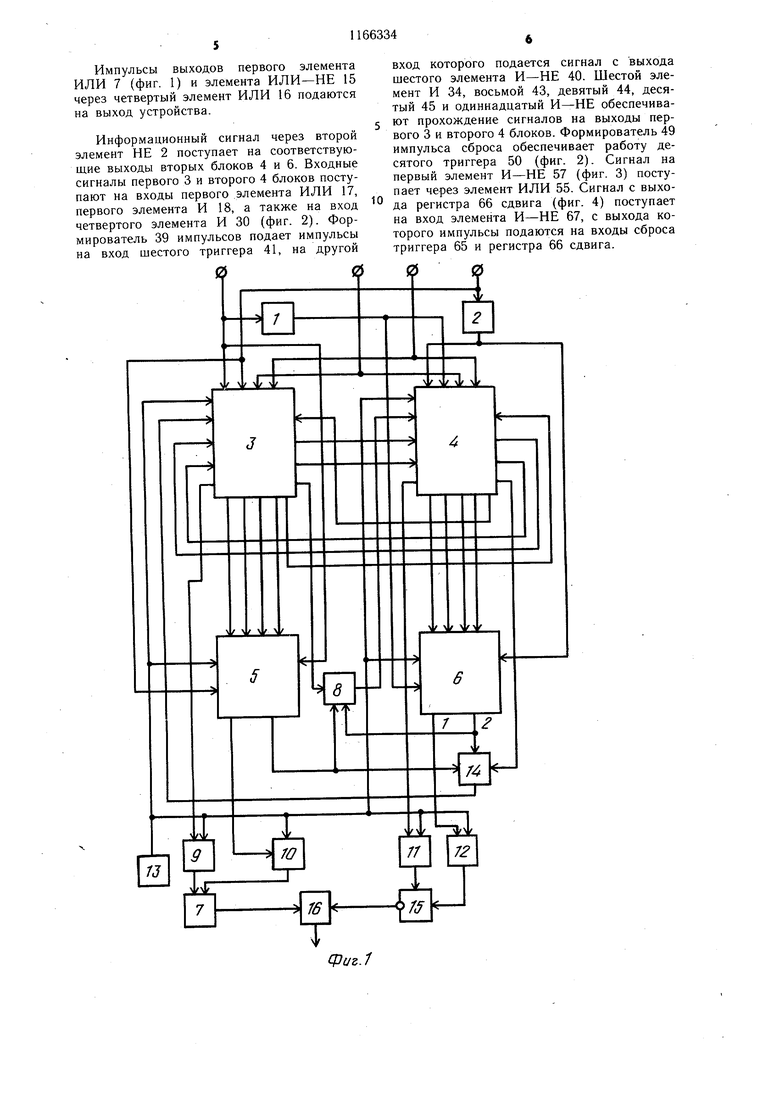

На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 - вариант выполнения блока анализа нечетных посылок; на фиг. 3 - вариант выполнения блока анализа четных посылок; на фиг. 4 - вариант выполнения формирователя импульсов.

Устройство для приема дискретных сигналов (фиг. 1). содержит первый 1 и второй 2 элементы НЕ, первый 3 и второй 4 блоки анализа нечетных посылок, первый 5 и второй 6 блоки анализа четных посылок, первый 7 и второй 8 элементы ИЛИ, первый 9, второй 10, третий 11 и четвертый 12 формирователи импульсов, генератор 13 тактовых импульсов, третий элемент ИЛИ 14, элемент ИЛИ-НЕ 15, четвертый элемент ИЛИ 16.

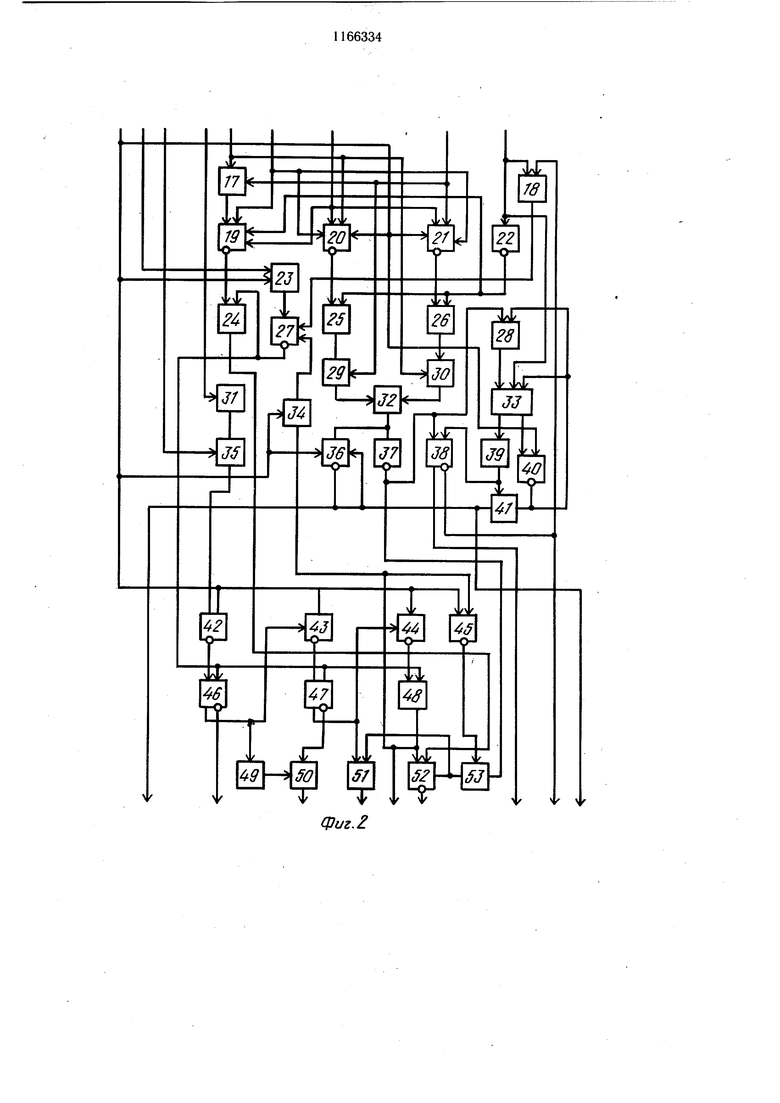

Блок анализа нечетных посылок (фиг. 2) содержит первый элемент ИЛИ 17, первый элемент И 18, первый 19, второй 20 и третий 21 элементы И-НЕ, элемент НЕ 22, второй элемент И 23, лервый 24, второй 25 и третий 26 триггеры, элемент ИЛИ-НЕ 27, четвертый триггер 28, третий 29, четвертый 30 и пятый 31 элемент И, второй элемент ИЛИ 32, регистр 33 сдвига, шестой элемент И 34, третий элемент ИЛИ 35, четвертый 36 и пятый 37 элементы И-НЕ, пятый триггер 38, формирователь 39 импульсов, шестой элемент И-НЕ 40, шестой триггер 41, седьмой 42, восьмой 43, девятый 44 и десятый 45 элементы И-НЕ, седьмой 46, восьмой 47 и девятый 48 триггеры, формирователь 49 импульса, десятый триггер 50, седьмой элемент И 51, одиннадцатый элемент И-НЕ 52, одиннадцатый триггер 53.

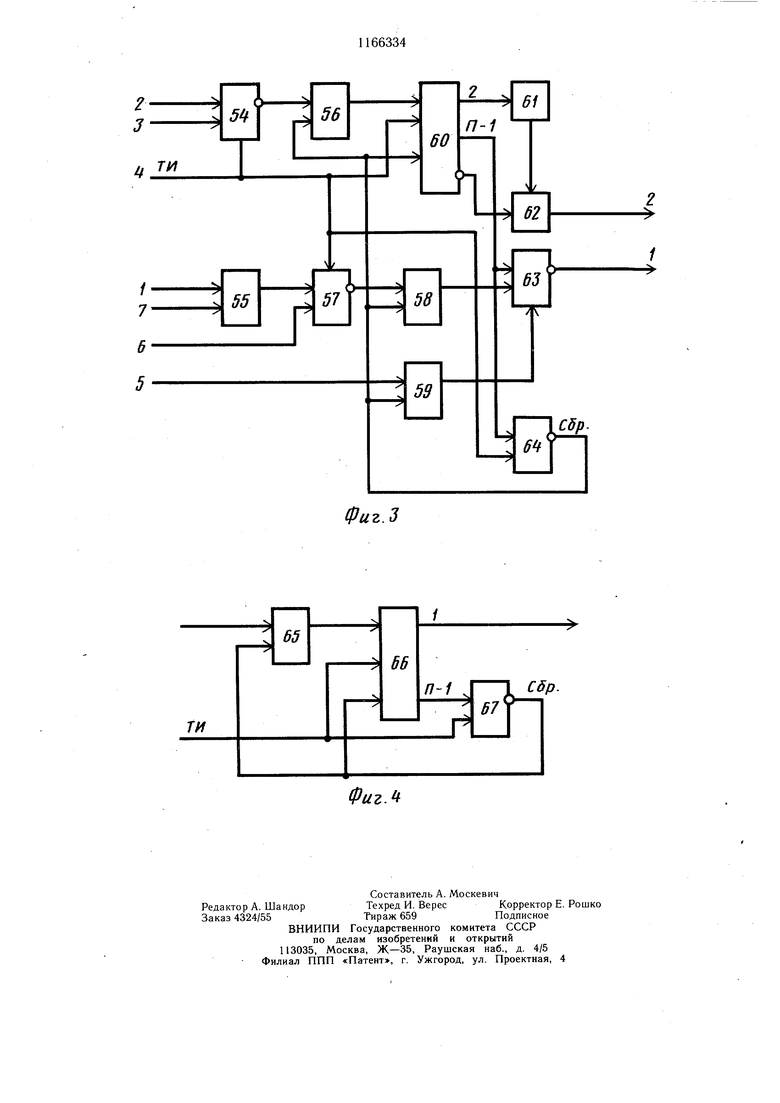

Блок анализа четных посылок (фиг. 3) содержит элемент И 54, элемент ИЛИ 55, первый триггер 56, первый элемент И-НЕ 57,

второй 58 и третий 59 триггеры, регистр 60 сдвига, формирователь 61 импульса сброса, четвертый триггер 62, второй 63 и третий 64 элементы И-НЕ.

5 Формирователь импульсов (фиг. 4) содержит триггер 65, регистр 66, элемент И-НЕ 67.

Устройство работает следующим образом.

Q На соответствующие входы устройства поступают информационные сигналы (фиг. 1), а на другие входы поступают единица и синхроимпульсы .

Первые блоки 3 и 5 запускаются передним фронтом тактового импульса при поступлении единицы на соответствующие входы устройства. Вторые блоки 4 и 6 запускаются передним фронтом тактового импульса при поступлении нуля на эти же входы устройства. При этом первый 19, второй 20 и третий 21 элементы И-НЕ первого блока 3 (фиг. 2) открыты для прохождения входного сигнала единицами, поступающими на их входы с соответствующего входа устройства, с выхода элемента НЕ 22 первого блока 3, с инверсного выхода пятого триггера 38 второго блока 4. Соответствующие элементы И-НЕ 19-21 второго блока 4 открыты для прохождения входного сигнала единицами, поступающими с устройства, с выхода элемента НЕ 22 второго блока 4, с инверсного выхода пятого триггера 38 первого блока 3. Первый 5 и второй 6 блоки входным сигналом на первом тактовом интервале (период следования синхроимпульсов) не запускаются (фиг. 3), так как первые элементы И-НЕ 57 этих блоков 5 и 6 закрыты для прохождения

5 входного сигнала нулевыми потенциалами, поступающими на их входы с прямых выходов шестых триггеров 41 первого 3 и второго 4 блоков.

При поступлении единицы с входа устройства, первый 24 и второй 25 триггеры первогоблока 3 устанавливаются в единичное состояние по переднему фронту такто-. вого импульса. С выхода первого триггера 24 единица поступает через пятый элемент И 31 (фиг. 2), открытый по другому входу единицей, поступающей с инверсного выхода седьмого триггера 46 второго блока 4 третий элемент ИЛИ 35 на один вход седьмого элемента И-НЕ 42. Седьмой триггер 46 устанавливается в единичное состояние тактовым импульсом, поступающим на другой вход седьмого элемента И-НЕ 42. Записанная единица продвигается тактовым импульсом.

Входной сигнал с выхода первого элемента НЕ 1 по тактовому импульсу устанавливает первый 24 и второй 25 триггеры второго блока 4 в единичное состояние. Входной сигнал,поступающий с входа устройства, по тактовому импульсу устанавливает третий триггер 26 первого блока 3 в единичное состояние и одновременно поступает на один из входов третьего элемента И 29, на другой вход которого поступает единица с выхода второго триггера 25. Если на первый тактовый интервал не поступает единица с входа устройства, первый триггер 24 и элементы памяти регистра 60 сдвига (фиг. 3) устанавливаются в исходное состояние синхроимпульсои,, поступающим с элемента ИЛИ-НЕ 27. Единица с выхода второго элемента ИЛИ 32 поступает на один из входов четвертого элемента И-НЕ 36, закрытого для прохождения тактового импульса нулевым потенциалом, поступающим на его другой вход с прямого выхода шестого триггера 41 и на один вход пятого элемента И-НЕ 37, на другой вход которого поступает тактовый импульс, который переводит четвертый 28, пятый 38 и одиннадцатый 53 триггеры в единичное состояние (фиг. 3). С прямого выхода пятого триггера 38 единица поступает на один вход второго элемента И 23 второго блока 4, на другой вход которого поступает тактовый импульс, который устанавливает первый триггер 24 первого блока в исходное состояние. Второй 25 и третий 26 триггеры первого блока 3 устанавливаются в исходное состояние синхроимпульсом, поступающим на его сбросовый вход с выхода элемента НЕ 22. С инверсного выхода пятого триггера 38 нулевой потенциал поступает на вход первого 19, второго 20 и третьего 21 элементов И-НЕ второго блока 4, запрещая прохождение входного сигнала. С выхода четвертого триггера 28 единица поступает на один.из входов регистра 33 сдвига, ,на другой вход которого поступают синхроимпульсы. С выхода первого разряда регистра 33 сдвига единица устанавливает шестой триггер 41 в единичное состояние, а пятый триггер 38 - в исходное состояние. С прямого выхода восьмого триггера 47 единица поступает на один из входов седьмого элемента И 51 первого блока 3, на другой вход которого поступает единица с одиннадцатого триггера 53. С инверсного

выхода восьмого триггера 47 нулевой потенциал устанавливает десятый триггер 50 в единичное состояние. С выхода,десятого триггера 50 единица поступает через второй элемент ИЛИ 8 (фиг. 1), третий элемент ИЛИ 35 второго блока 4 (фиг. 2) на вход седьмого элемента И-НЕ 42 этого второго блока 4, с выхода которого тактовый импульс переводит седьмой триггер 4б в единичное состояние.

С выхода элемента И 51 единица поступает на один вход элемента И 54 первого блока 5 (фиг. 3), на другой вход которого поступает единица с прямого выхода девятого триггера 48 первого блока 3 (фиг. 2) и по тактовому импульсу первый триггер 56 устанавливается в единичное состояние. Одновременно с этим устанавливается в единичное состояние триггер 65 первого формирователя 9 импульсов (фиг. 4).

С выхода четвертого элемента И-НЕ 36 тактовый импульс устанавливает третий триггер 59 в единичное состояние. Входной сигнал поступает с входа устройства через первый элемент И-НЕ 57, открытый единицей, поступающей на его вход с прямого выхода шестого триггера 41 первого блока 3, второй триггер 58 первого блока 5 устанавливается тактовым импульсом в единичное состояние. С прямого выхода регистра 60 сдвига через второй элемент И-НЕ 63 триггер 65 второго формирователя 10 импульсов устанавливается в единичное состояние (фиг. 4). По переднему фронту тактового импульса на выходе первого разряда регистра 66 сдвига устанавливается единица. С инверсного выхода регистра 60 сдвига нулевой потенциал переводит четвертый триггер 62 в единичное состояние. Первый 56 второй 58 и третий 59 триггеры, регистр 60 сдвига устанавливаются в исходное состояние с выхода третьего элемента И-НЕ 64. Четвертый 28 и шестой 41 триггеры, регистр 33 сдвига (фиг. 2) устанавливаются в исходное состояние тактовым импульсом с выхода седьмого элемента И-НЕ 42. С выхода четвертого триггера 62 единица поступает через третий элемент ИЛИ 14 (фиг. 1), третий элемент ИЛИ 35 первого блока 3 на вход седьмого элемента И-НЕ 42 и одновременно через второй элемент ИЛИ 8, третий элемент ИЛИ 35 второго блока 4 на вход седьмого элемента И-НЕ 42. По тактовому импульсу седьмые триггеры 46 первого 3 и второго 4 блоков переводятся в единичное состояние. Четвертый триггер 62 устанавливается в исходное состояние с выхода формирователя 61 импульса сброса.

Тактовые импульсы с выхода генератора 13 тактовых импульсов задают такт работы первого 9, второго 10, третьего 11 и четвертого 12 формирователей импульсов.

Импульсы выходов первого элемента ИЛИ 7 (фиг. 1) и элемента ИЛИ-НЕ 15 через четвертый элемент ИЛИ 16 подаются на выход устройства.

Информационный сигнал через второй элемент НЕ 2 поступает на соответствующие выходы вторых блоков 4 и 6. Входные сигналы первого 3 и второго 4 блоков поступают на входы первого элемента ИЛИ 17, первого элемента И 18, а также на вход четвертого элемента И 30 (фиг. 2). Формирователь 39 импульсов подает импульсы на вход шестого триггера 41, на другой

ЦЗиг.1

вход которого подается сигнал с выхода шестого элемента И-НЕ 40. Шестой элемент И 34, восьмой 43, девятый 44, десятый 45 и одиннадцатый обеспечивают прохождение сигналов на выходы первого 3 и второго 4 блоков. Формирователь 49 импульса сброса обеспечивает работу десятого триггера 50 (фиг. 2). Сигнал на первый элемент И-НЕ 57 (фиг. 3) поступает через элемент ИЛИ 55. Сигнал с выхода регистра 66 сдвига (фиг. 4) поступает на вход элемента И-НЕ 67, с выхода которого импульсы подаются на входы сброса триггера 65 и регистра 66 сдвига.

2 3

7

6 5

Фиг.З

ФигЛ

| Устройство для приема диксретных сигналов | 1976 |

|

SU640447A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для приема дискретных сигналов | 1977 |

|

SU681573A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-07-07—Публикация

1983-01-20—Подача