вертого коммутаторов, выхоаы которьос соеаинены с первыми входами соответ«ствешго первого и второго элементов И, второй и третий выхоаы формирователя тактовых импульсов соединены соответ ственно с вторыми и третьими информационными входами третьего и четвертого . коммутаторов, единичный вьиод четвв| того триггера управления соединен с первыми управляющими входами третьего и четвертого коммутаторов, первыми вхо« цами третьего, четвертого и пятого элементов И, первого и второго элеме TOS И-JHE, выходы которых соединены с вторыми входами соответственно первого и второго элементов Н, второй управлякадий выход первого регистра микрокоманд соединен с первыми входами второго и третьего элементов ИЛИ, выход которого соединен с первым управляющим входом первого коммутатора, второй управляющий выход второго регистра микрокоманд соединен с первым входом четвертого и вторым входом второго элемента ИЛИ, выход которого соединен с Твхоцом пятого триггера управления, единичный выход пятого триггера управления соедш1ен с вторыми управляющими входами третьего и четвертого коммутаторов, нулевой выход пятого триггера соединен с третьими управляющими входами третьего и четвертого коммутаторов, третьи управляющие выходы первого и второго регистров микрокоманд через пятый элемент ИЛИ соединены с едйнич1 ым входом четвертого триггера управления, нулевой выход которого соединен с вторым управляющим входом первого комму- штора и первым управляющим входом второго коммутатора, нулевые выходы первого и второго триггеров управления соеаинены с вторыми входами соответственно третьего и пятого элементов И, вы- ; Ходы.которых соединены с вторыми входами соответственно третьего и четвертого элеме1 тов ИЛИ, выход которого соединен с вторым управляющим входом второго коммутатора, третьи управляющие входы первого и второго регистров микрокоманд соединены с третьими управляющими входами соответственно перового и второго коммутаторов, единичный вьосод первого триггера управления соепи ней с вторым входом первого элемента И-4{Е и первым входом щестого элемента И, единичный выход второго триг гера управления соединен с вторым входом второго элемента И-ЛЕ и вторым входом шестого элемента И, выход ко« торого соединен с первыми входами седьмого и восьмого элементов И и через одновибратор - с нулевыми входами перового, второго и четвертого триггерОЬ управления, выходы адреса первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами схемы сравнения, прямой и инверо ный Бьжод которой соединен с вторыми : входами соответственно седьмого и восьмого элементов И, выход седьмого элемента И соединен с третьими входами третьего и четвертого элементов ИЛИ, выход восьмого элемента И соединен с первыми входами шестого и седьмого элементов ИЛИ, выходы которьк соединены соответственно с нулевым входом третьего триггера управления и выходом ошибки устройства, выход конпа операции блока элементов ИЛИ соединен с вторыми входами шестого элемента ИЛИ и четвертого элемента И, выход которого соединен с вторым входом седьмого элемента ИЛИ. -

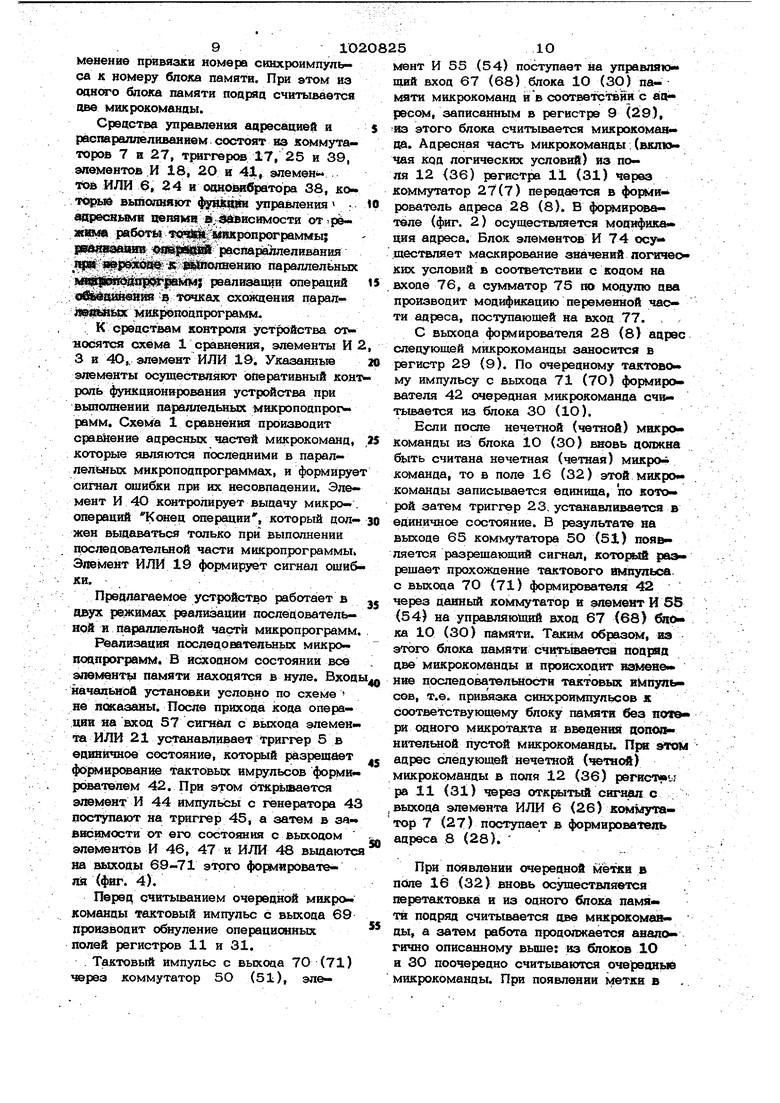

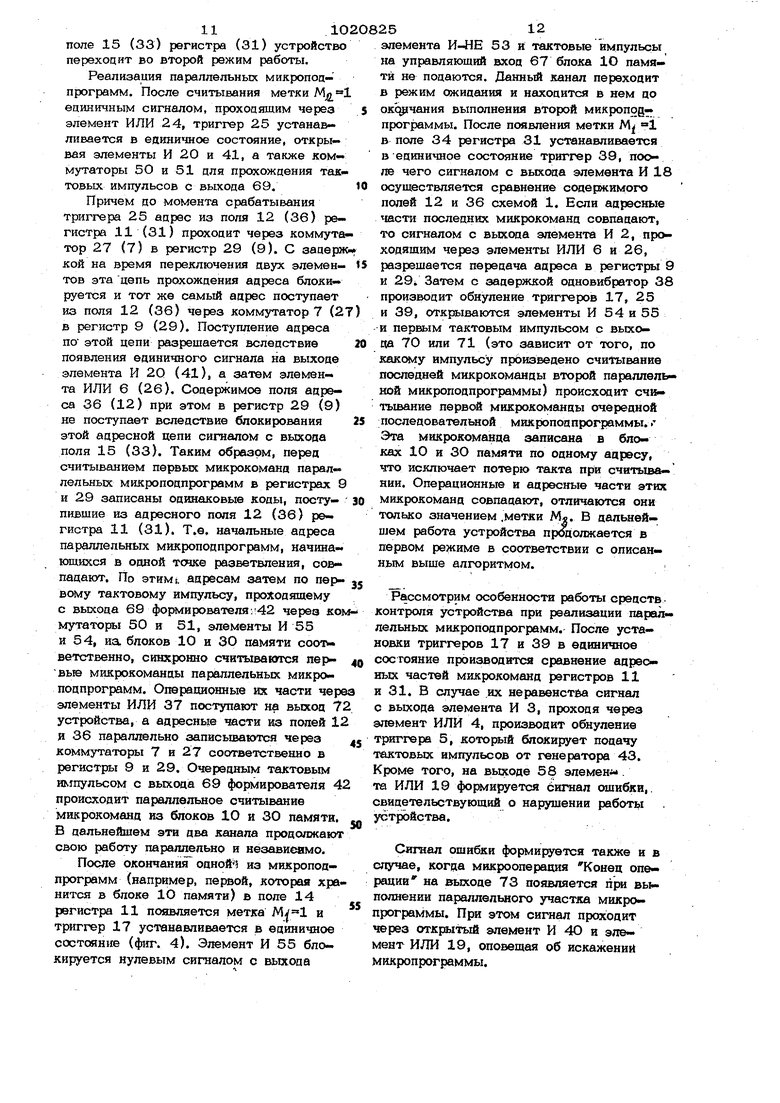

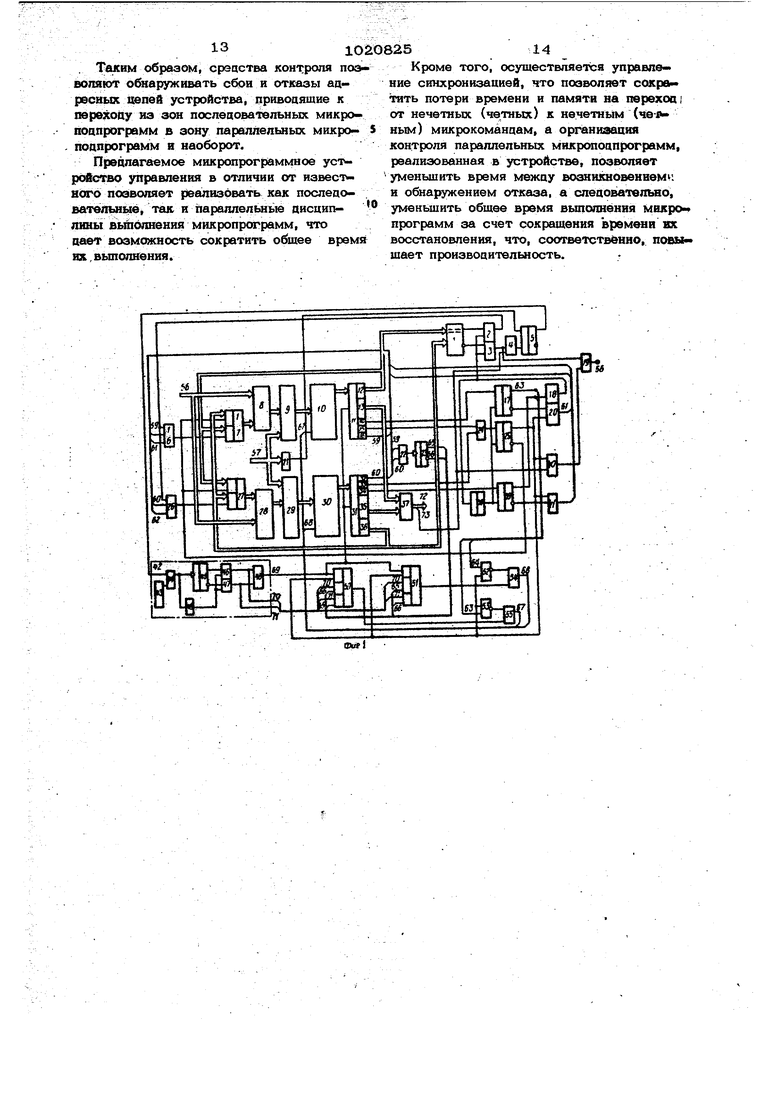

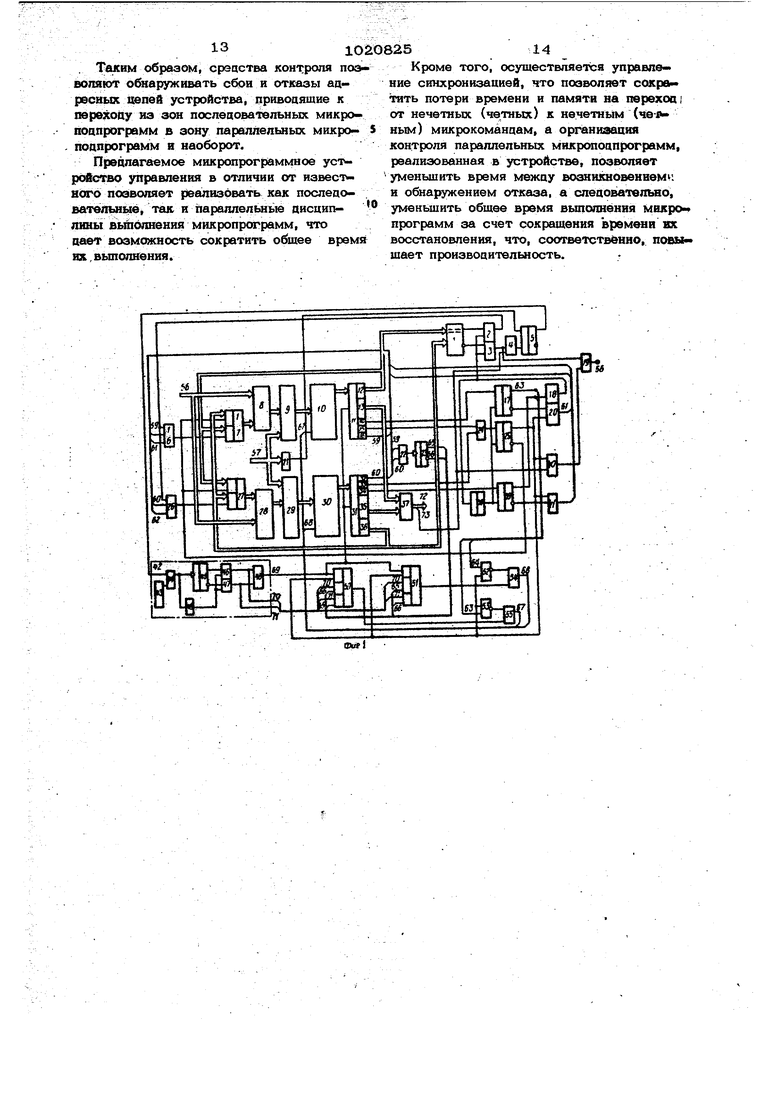

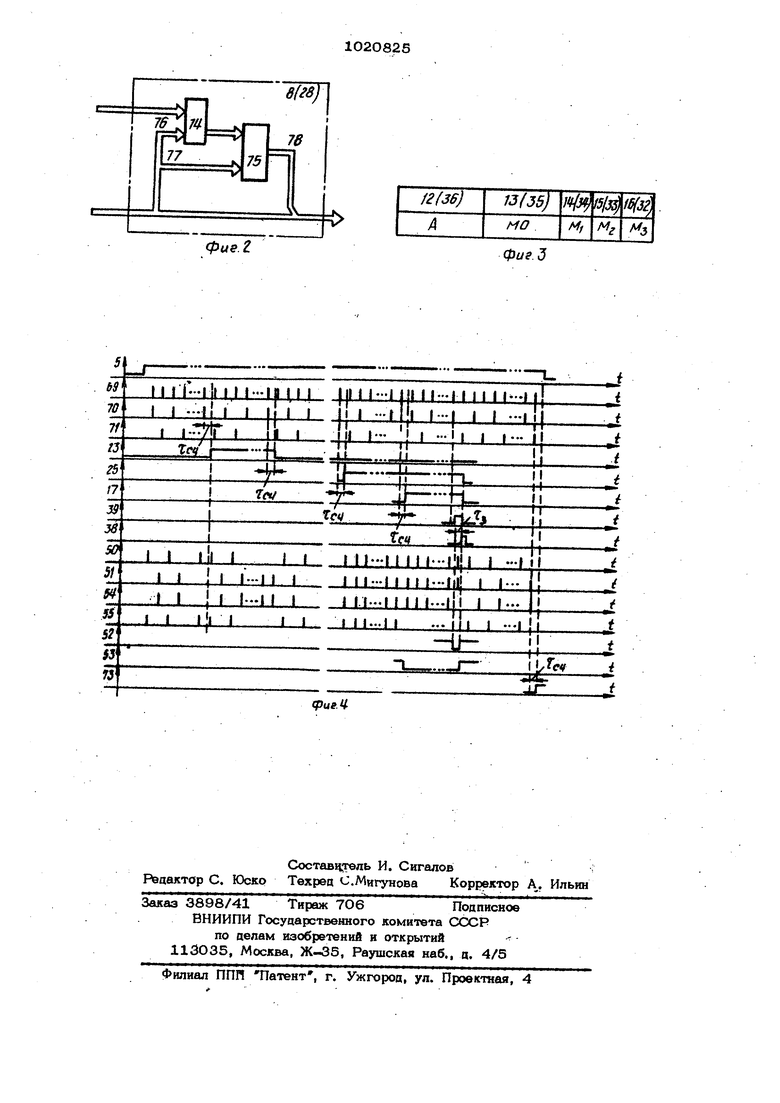

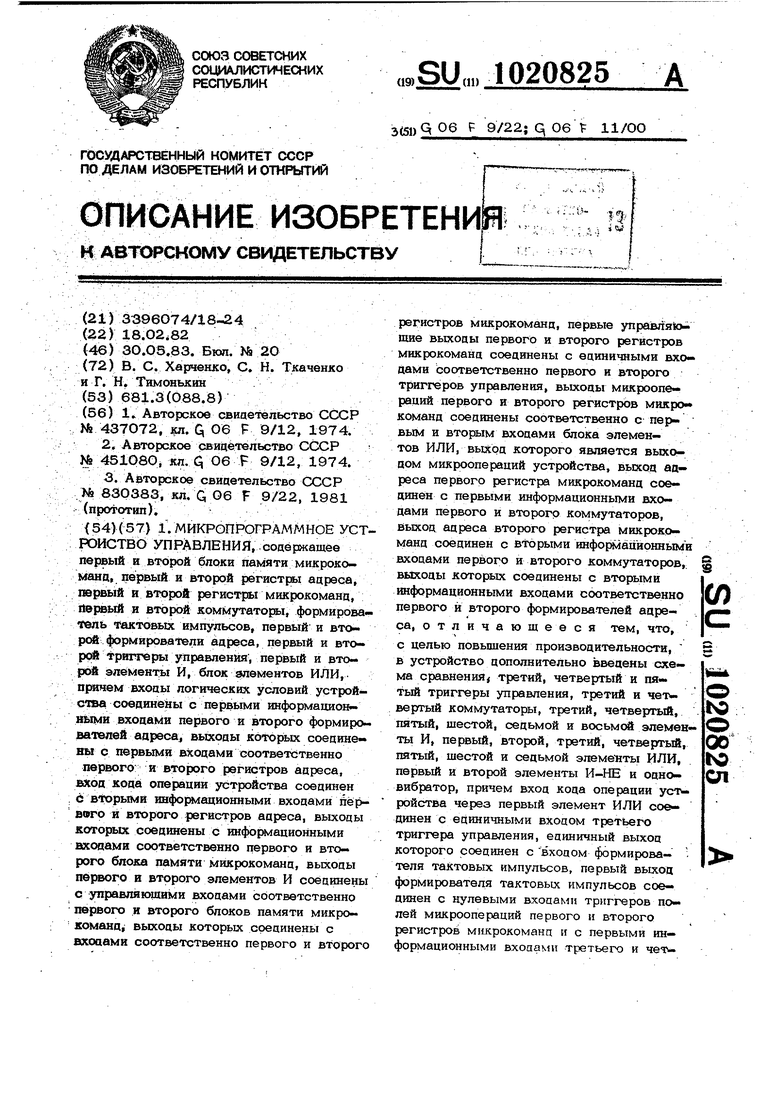

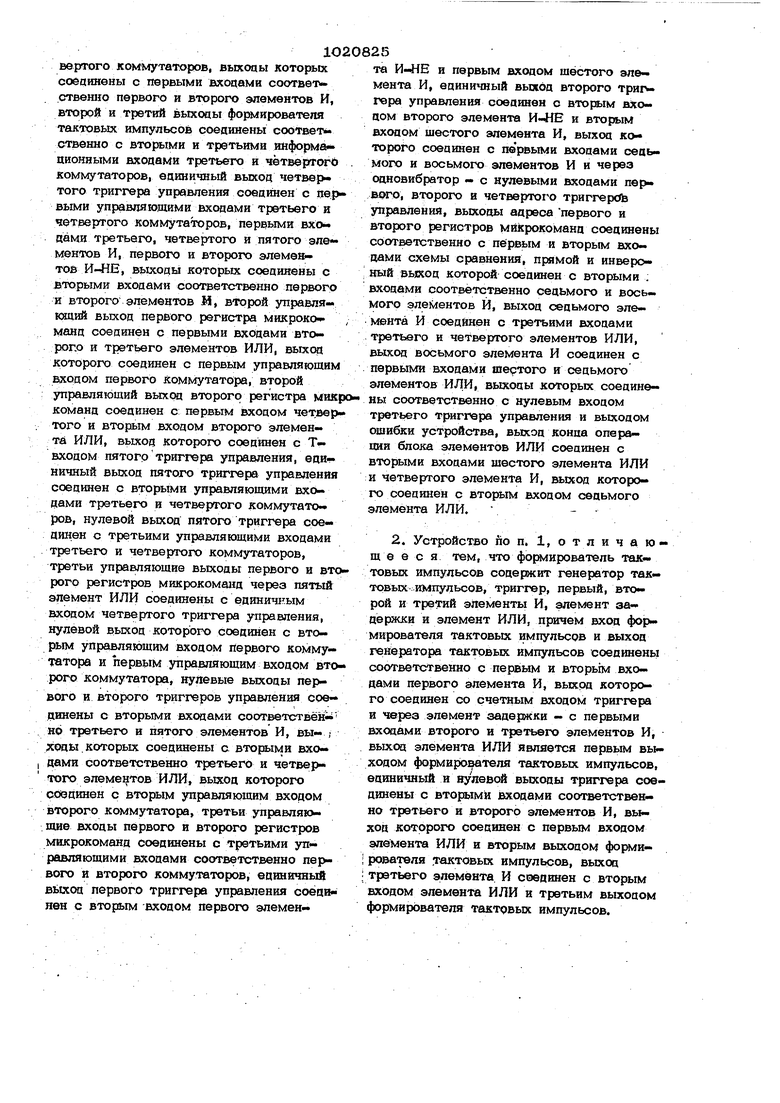

2. Устройство поп. 1, отличающ е ее я тем, что формирователь тактовых импульсов содержит генератор так- импульсов, триггер, первый, второй и третий элементы И, элемент задержки и элемент ИЛИ, причем вход формирователя тактовых импульсов и выход генератора тактовых импульсов соединены соответственно с первым и вторьгм входами первого элемента И, выход которого соединен со счетным входом триггера и через элемент задержки - с первыми входами второго и третьего элементов И выход элемента ИЛИ является первым выходом формирователя тактовых импульсов единичный и нулевой выходы триггера соединены с вторыми входами соответственно третьего и второго элементов И, выход которого соединен с первым входом элемента ИЛИ и вторым выходом форми; решателя тактовых импульсов, выход ; третьего элемента И соединен с вторым входом элемента ИЛИ и третьим выходом формирователя тактрвых импульсов. Изобретение относится к цифровой вычислительной технике и может быть иопользовано при разработке микропрограмм миых устройств управления параллельных вычислительных и управлякших систем. Известно микропрограммное устройство управления, сЬцержашее блоки памяти, регистры микрокоманд и регистры аареса, формирователи адреса, триггеры, элемейты И . Известно Микропрограммное устройство управления, содерисашее блоки памяти, регистры йареса, ксллмутаторы, триггеры, элемен№1 И 2} . Неаостатками ibSB©c«Htbix устройств являются низкая {1ро с оаятельность и узкие функниональвьсе )зможности, что обусловлено неаройзёосцителшыми затратами времени при иесзйхойимости повторного считывания информации из одного блока памяти, когай после четной (нечетной) микрокоманды следует четная (нечетная) микрокоманда. Кроме того, структура аналогов не позволяет реализовать параллельные микропрограмм мы и йе обеспечивает оперативный контроль функционирования. Наиболее близким к предлагаемому является микропрограммное устройство управления, содержащее первый и второй блоки памяти микрокоманд, первый и второй регистры аареса, первый и вторсй регистры Микрокоманд; первый и второй комк таторы, формирователь тактовых импульсов, первый и второй формировате ли адреса, первый и второй триггеры уп- равления, первый и второй элементы И, блок элементов ИЛИ, причем входы логических условий устройства соединены с первыми информационными входами перво ГО и второго формирователей адреса, выходы которых соединены с первыми входами соответственно первого и второго регистров адреса, вход кода операции устройства .соединен с вторыми инфорьмационными входами первого и второго регистров адреса, выходы которых соеди нены с инфо1я ациош1ыми входами соот ветственно первого и второго блоков п/ мяти микрокоманд, выходы первого и второго элементов И соединены с управляющими вхсщами соответственно первого и второго блоков памяти микрокоманд, выходы которых соединены с входами соответственно первого и второго регист ров микрокоманд, первые управлякшхие выходы пе{жого и второго регистров мик команд соединены с единичными входами - соответственно первого и второго тригеров управления, выходы микроопераций первого и второго регистров микрокоманд оединены соответственно с первым и вторым входами блока элементов ИЛИ, пыход оторого является выходом микроопераий устройства, выход адреса первого регистра микрокоманд соединен с первыми информационными входами первого и вто- рого коммутаторов , выход .адреса второго. V регистра микрокомана соединен с вторыми информационными входами первого и второго KOMMyTaTopOBj выходы которых соединены с вторыми информационными входами соответственно первого и второго формирователей адреса з . Недостатком устройства является низкая прЬиэвоаительность, которая обусловлена отсутствием технических средств, обеспечивающих реализацию параллельных микропрограмм и возможность изменения последовательности поступления тактовьрс импульсов схемы при последовательном выполнении двух четных (нечетных) MHKpOi команд. При этом под параллельной понимается микропрограмма, в которой в одном такте ф ормироваться две и более микрокоманд. Для реализадии параллельных микропрограмм необходимы техничео : кие средства, реализующие операторы распараллеливания, отсутствие которых и обуславливает низкую производительность. Кроме того, дополнительное снижение производительности вызвано тем, что прт наличии в последовательных участках то чек схождения в микропрограмму аолжны вводиться специальные пустые микрокоманды, которые обеспечивают выравнивание участков по четности. Это связано с реализацией жесткой синхронизации, т.е. к каждому блоку памяти постоянно привязан один и тот же импульс. Цель изобретения - повышение прошэ- водительности устройства, i Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее первый в второй, блоки памяти микрокоманд, первый и вто рой регистры адреса, первый и второй регистры микрокоманд, первый и вторсЛ коммутаторы, формирователь тактовых импульсов, первый и второй формирователи адреса, первый и второй триггеры управления, первый и второй элементы И, блок элементов ИЛИ, причем входы логически : условий устрсАства соединены с первыми информационными входами первого и второго формирователей адреса, выходы которых соединены с первыми входами соответ ственно первого и второго регистров адреса, вход кода операции устройства сое- цинен с вторыми информационными входа i ми первого и второго регистров адреса, выхоаы которых соединены с информааионными. входами соответственно первого второго блоков памяти микрокоманд, выходы первого и. второго элементов И соединены о управляющими входами со ответственно первого и второго блоков памяти микрокоманд, выходы KOTopbt соединены с входами соответственно первогчэ и второго регистров микрокоманд первые управляющие вьрсоды первого и второго регистров микрокоманд соединены с единичными входами соответственно первого и-второго триггеров управле- ния, выходы микроопераций первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход которого является выходом микроопераций устройства, Bbixoa адреса первого регистра микрокоманд соединен с первы-. ми информационными входами первого и второго коммутаторов, вькод адреса вто- рого регистра микрокоманд соединен с вторыми информационными входами перво го и второго коммутаторов, выходы которых соединены с вторыми информационны ми входами соответственно первого и второго формирователей адреса, дополнительно введены схема сравнения, третий/ четвертый и пятый триггеры управления, третий и четвертый коммутаторы, третий четвертый, пятый, шестой, седьмой и восьмой элементы И, первый, второй, третий, четвертый пятый, шестой и седьмой элементы ИЛИ, первый и второй эпе менты И-ЛЕ и одновибратор, причем вход кода операции устройства через первый элемент ИЛИ соединен с единичным входом третьего триггера управления, единичный выход которого соединен с входом формирователятактовых импульсов, первый вькод формирователя тактовых импульсов соединен с нулевыми входами триггеров палей микроопераций первого и второго регистров микрокоманд и с , первыми информационными входами третьего и четвертого коммутаторов, выходы которых соединены с первыми входами соответственно первого и второго элементов И, второй и третий выходы фо{ мирователя тактоввт импульсов соединены соответственно с вторыми и третьими информационными входами третьего и чет вертого коммутаторов, единичный выход четвертого триггера управления соединен с первыми управляющими входами третьего и четвертого коммутаторов, первыми входами третьего, четвертого и пятого элементов И, первого и второго элементов , выходы которых соединены с вторьши вхрцами соответственно первого и второго элементов И, вторсЛ управляющий выход первого регистра микрокоманд соединен с первыми входами второго и третьего элементов ИЛИ, выход которого соединен с первым управляющим входом первого коммутатора, второй управляющий выход второго регистра микрокоманд соединен с первьп, входом четвертого и вторым входом второго эле- мюнта ИЛИ, выход которого соединен с Т-еходом пятого триггера управления, единичный выход пятого триггера управления соединен с вторыми управляющими входами третьего и четвертого коммутаторов, нулевой выход пятого триггера соединен с третьими управляющими входами третьего и четвертого коммутаторов, третьи управляющие выходы первого и второго регистров микрокоманд через пятый элемент ИЛИ соединены с единичным входом четвертого триггера управления, нулевой выход которого соединен с вторым управляющим входом первого коммутатора и первым управлякмцим входом второго коммутатора, нулевое выходы первого и второго триггеров управления соединены с вторыми входал« соответственно третье- го и пятого элементов И, выходы которых соединены с вторыми входами соответственно третьего и четвертого элемен- тов ИЛИ, выход которого соединен с вторым управляющим входом второго коммутатора, третьи управляющие выходы первого и второго регистров микрокоманд .соединены с третьими управляющими входами соответственно первого и второго коммутаторов, единичный выход первого триггера управления соединен с вторым входом первого элемента И-НЕ и первым входом шестого элемента И, единичный выход второго триггера управления соединен с вторым входом второго элеменга И-НЕ и вторым входом шестого элемента И, выход которого соединен с первыми входами седьмого и восьмого элементов И и через одновибратор - с нулевыми входами первого, второго и четвертого триггеров управления, выходы адреса первого и второго регистров микрокоманд соединены соответственно с первым и вторым входами схемы сравнения, прямой и инверсный выход которс соединен с вторыми входами соответственно седьмого элементов И, выхоц седьмого и восьмого соединен с третьими входами элемента И третьего и четвертого элементов ИЛИ, выход восьмого 1 лемента и соединен с первыми входами шестого и седьмого эле ментов ИЛИ, выходы которых соединены ; соответственно с нулевым входом третьего триггера управления и выходом ошибки устройства, выхоц конца операции блока элементов ИЛИ соединен с вторыми вхоцеалк шестого элемента ИЛИ и четвертого элемента И, выхоц которюго соединен с втбрым BXOdOM седьмого элемента ИЛИ. Кроме того, формирователь тактовых импульсов содержит генератор тактовых импульЬов, триггер, первый, второй и тре тий элементы И, элемент задержки и элемент ИЛИ, причем вход формирователя тактовых импульсов и вькоц генератор тактовых импульсов соединены соответ ственно с первым и вторым входами первого элемента И, выход которого соединен со счетным входом триггера и через элемент задержки - с первыми входами второго и третьего элементов И, выход элемента ИЛИ является первым выходом формирователя тактовых импульсов, единичный и нулевой выходы триггера сое- . диНены с вторыми входами соответствен- йо третьего и второго элементов И, выхо .которого соединен с первым входом эле-« мента ИЛИ и вторълм выходом формирователя тактовых импульсов, выход третьего элемента И соединен с вторым входом элемента ИЛИ и третьим выходом формирователя тактовых импульсов. Сущность изобретения состоит в повышении производительности устройства пу. тем реализации как последова-гельных, так и параллельных микропрограмм, управления синхр ониэацией считывания микр окоманд,органнаав Ий оперативного контроля правильности вьшолнения параллельных микропрограмм. Ст гктура устрсй1ства позволяет реали эовать либо одну последовательную микро программу, либо вьшош1ить параллельную Мйкрсздрограмму. Для выполнения параллельных ветвей в микропрограмме введена специальная метка - микрооперация, реализующая опе ратор распараллеливания и обеспечивающа управление перестройкой:структуры из исходной двухплечевой в параллельную. Кроме того, для реализации оператора объединения параллельных ветвей также введена специальная мепса, указывающая на окончание параллельной микропрограммы. Управление С1шхронизацией устройства осуществляется путем формирования сигнала микрооперации окончания последовательной ветви перед точкой схождения, если после четной (нечетной) микрокоманды выполняется четная (нечетная) микрокоманда. Для организации оперативного контроля использованы две специфические особенности параллельных микропрограмм: адресные части последних микрокоманд параллельно выполняемых микропрограмм должны совпадать, сигнал Конец операции может быть выдан только в последовательной части параллельной микропрограммы. Организация контроля, основанного на проверке вьшолнения этих двух правил, позволяет повысить достоверность функционирования параллельного микропрограммного устройства управления благодаря возможности обна{оокения искажений функции переходов (адресных цепей) при выполнении параллельных участков. На фиг. 1 приведена функциональная схема микропрограммного устройства управления на фиг. 2 - функциональная схема первого и второго формирователей адреса; на фиг. 3 - формат микрокоманд; на фиг. 4 - временная диаграмма работы устройства. Функциональная схема параллельного микропрограммного устройства управления с контролем (фиг. 1) содержит схему 1 сравнения, седьмой 2 и восьмой 3 элементы И, шестой элемент ИЛИ 4, jrpeTHft триггер 5 управления, третий эле- ; мент ИЛИ 6, первый коммутатор 7, первый формирователь 8 адреса; первый регистр 9 адреса, первый блок 10 памяти микрокоманд, первый регистр 11 микрокомайд, в состав которого входят поля 12 i адреса, поля 13 микрооперашй, пола 14 метки конца параллельной микроподпрограммы, поля 15 метки начала параллельной микропрограммы и поля 16 метки управления синхронизацией, первый Tjacrгер 17 управления, шестой элемент И 18, седьмой элемент ИЛИ 19, третий элемент И 2О, первый 21 и второй 22 элементы ИЛИ, пятый триггер 23 управления, пятый элемент ИЛИ 24, четвертый триггер 25 управления, четвертый элемент ИЛИ 26, вторые коммутатор 27, формирователь 28 адреса, регистр 2& адреса, блок 30 памяти микрокоманд и регистр 31 микрокоманд, в состав ко- трро.го входят метки 32 управления синхронизацией, метки 33 начала парал- т10 далшой микропоапрограммы, метки 34 - 36 конца параллельной микропоцпрограммы, микроопераций и адреса, блок элементов ИЛИ 37, оцновибратор 38, второй триггер 39 управления, четвертый 40 и пятый 41 элементы И,, формировя ; тель 42 тактовых импульсов, состоящий из генератора 43 тактовых импульсов, первого элемента И 44, триггера 45, второго 46 и третьего 47 элементов И ;и элемента ИЛИ 48; линия задержки 49, третий 50 и четвертый 51 коммутаторы, второй 52 и третий 53 элементы И-НБ, второй 54 и первый 55 элементы И, вхоц 56 логических условий, вход 57 кода операции и выход 58 ошибки уст ройства соответственно; выход 59 (60) поля метки управления синхронизаЦиа ей 16 (32) регистра 11 (31), первый (второй) вход второго элемента ИЛИ 22, первый вход третьего (четвертого) элемента ИЛИ 6 (26), выход 61 третьего (пятого 62) элемента И 20 (41), второй вход третьего (четвертого) элемента ИЛИ 6 (26); единичный выход 63 первого (второго 64) триггера управления 17 (39), первый (второй) вход элемента И 18, второй вход первого (вто рого) элемента И-НЕ (53 (52); ециничный 65 (нулевой 66) выход пятого триггера 23 управления, третий (второй) управляющий вход третьего коммутатора 50 второй (третий) управляющий вход чвт вертого коммутатора 51; выход 67 второго (первого 68) элемента И 54 (55), управляющий вход первого (второго) блока 10 (30) памяти микрокоманд; первый выход 69 формирователя тактовых импуль сов и втфой 70 (третий 71) выход формирователя тактовых импульсов, второй V7«J..n Л Vf OMV niVJlljr«lD / 9| О VJ wJCl (третий) информационный вход третьего 5 и четвертого 51 коммутаторов; выход 72 микроопераций устройства, выход 73 микроопераций операции. На фиг. 2 представлен блок 74 элементов И, сумматор 75 по модуто два, вход 76 кода логических условий . вход 77 модифицируемой части адреса, вход 78 модифицированных разрядов адреса. Формат микрокоманды (фиг. 3) содержит поле адреса А, микроопераций МО и. меток М., М, и М, причем: fl, если микрокоманда является М,, последней в параллельной микро1 программе; Ш, в противном случае; 5 , если микрокоманда предшествуJ ет началу параллельной микропрогграммы;0, в противном случае; , если после нечетной (четнсй) I должна следовать нечетная (четI ная) микрокоманда; LO, в противном случае. Нумерация полей на фиг. 3 cooTBeiv ствует юс нумерации, пряшятой на фиг. 1. На временной диаграмме (фиг, 4) показаны изменения сигналов в наиболее харбктерньрс точках схемы. Числа на оси ординат указьюают номера точек схемы выходов элементов, ;5 , 154-время считывания микрокоманд из блоков 1О (ЗО) памяти и задержки сигнала на одновибраторе 38. В устройство условно могут быть выделены средства хранения и считывания микрокоманд, пуска и синхронизации, управления синхронизацией, управления адресацией и распараллеливанием, контроля и хранения и считывания микрокоманд. К средствам хранения и считьшания микрокоманд относится формирователи 8 и 28 адреса, регистры 9 и 29 адреса, блсжи 1О и 30 памяти микрокоманд, регистры 11 и 31 микрокоманд, блок 37 элементов ИЛИ. Эти узлы обеспечивают хранение последовапгельных и параллельных микроподпрограмм, формирование адресов очередных микрокоманд в зависимости от кода и значений логических условий, а также формирование начального адреса в соответствии с кодом операции. Средства пуска и синхронизации включают формирователь 42 тактовых импуль сов, триггер 5, элементы ИЛИ 4 ef 21. Эти средства выполняют функции пуска устройства после прихода кода операции, формирование тактовых импульсов и остановка устройства при появлении сигнала ш1ибки или конца операции. К средствам управления синхронизацией относятся триггер 23, коммутаторы 5О и 51, элементы И-ЛЕ 52 и 53, элементы И 54 и 55, элемент ИЛИ 22. Указанные элементы обеспечивают управление синхрон1}зацией в зависимости от режима работы. При выполнении последователшых микроподпрограмм осуществляется попеременное считывание информации из блоков памяти 1О и 30. В точках изменения последовательности тактовых импульсов, когда после четнсЛ (нечетаой) микрокоманды должна идти четная (нечетная), по метке Мд производится измевение привязки номера синхроимпуль са к номеру блока памяти. При этом из оаного блока памяти подряа считывается ове микрокоманаы. Срецства управления адресацией я распараллеливанием состоят из коммутаторов 7 и 27, триггеров 17, 25 и 39, эдементов И 18, 20 и 41, элемен Toj ИЛИ 6, 24 и ooHOKtit Topa 38, кощр/ыд вьтопияют якшш зтравления v : варесвьали цепями в. йвисимости от режшищ работы (ропрограммы; |вая« аш ш|ййр||| распараллеливания №р№ ) 1C |%4подвен1ш параллельных ш«1|юек в|( реализации операций оёЫ1ШШвН1{8 в точках схожаения параяЯ1в1Ш1 {ИКрО1Юапрограмм. К среаствам контроля устройства от носятся схеме 1 сравнения, элементы И 3 и 4О, элемент ИЛИ 19. Указанные элементы осзпаествпяют оперативный конт роль функционироазния устройства при выполнении параллед1шых микропоцпроп- рамм. Схема 1 сравнения произвоцит сравнение адресных частей микрокоманд, которые являются последними в параллельных микроподпрограммах, и формируе сигнал ошибки при их несовпадении. Элемент И 4О ксмтролирует выдачу микро- операций Конец операции , который должен выдаваться только при выполнении прследс@ательной части микропрограммы Элемент ИЛИ 19 формирует сигнал ошиб ки. Преалагаемое уст ройство работает в двух режимах реализации последовательной и па|)аллелы1Ой части микропрограмм Реализация последовательньос микроподпрограмм. В исходном состоянии все элементы памяти находятся в нуле. Вход начальной установки условно по схеме не показаны. После прихода кода операции яа вход 57 сигнал с выхода элемента ИЛИ 21 устанавливает триггер 5 в единичное состояние, который разрешает формирование тактовых имрульсов формирователем 42. При этом открьавается элемент И 44 импульсы с генератора 4 поступают на триггер 45, а затем в за- вшЬимости от его состояния с выходом элементов И 46, 47 и ИЛИ 48 вьщаютс на выходы 69-71 этого фо ыирователя (фиг. 4). Перед считыванием очередной микрокоманды тактовый импульс с выхода 69 производит обнуление операцися1ных полей регистров 11 и 31. . Тактовый импульс с выхода 70 (71) через коммутатор 5 О (51), эле- мент И 55 (54) поступает на управлжо щий вход 67 (68) блока 10 (ЗО) памяти микрокоманд и в соответствии с адресом, записанным в регистре 9 (29), из этого блока считывается микрокоманда. Адресная часть микрокоманды. (включая код логических условий) из поля 12 (36) регистра 11 (31) через коммутатор 27(7) передается в формирователь адреса 28 (8). В формирователе (. 2) осуществляется модификация адреса. Блок элекюнтов И 74 осу- :шествляет маскирование значений погичео ких условий в соответствии с кодом на входе 76, а сумматор 75 по модулю два производит модификацию переменной части адреса, поступающей на вход 77. . С выхода формирователя 28 (8) адрес следующей микрокоманды заносится в регистр 29 (9). По очередному тактовому импульсу с выхода 71 (70) формирователя 42 очередная микрокоманда считывается из блока 30 (1О). Если после нечетной (четной) макрокоманды из блока 10 (30) вновь должна быть считана нечетная (четная) микроксманда, то в поле 16 (32) этой микрокоманды записывается единица, по которой затем триггер 23, устанавливается в единичное состояние. В результате на выходе 65 коммутатора 5О (51) появляется разрешающий сигаал, который разрешает прохождение тактового 1)мпульса. с выхода 70 (71) формирователя 42 через данный коммутатор и элемент И 55 (54) на управляюйшй вход 67 (68) блока 10 (ЗО) тшмяти. Таким образом, вэ этого блока цамяти считьивается подрва две микрокоманды и происходит измене ние последовательности тактовых вмпулы сов, т.е. привязка синхроимпульсов х соответствующему блоку памяти без потери одного микротакта и введения попоюнител1Л10й пустой микрокоманды. При атом адрес следующей нечетной () микрокоманды в поля 12 (36) регист и ра 11 (31) через открытый сигнал с / , выхода элемента ИЛИ 6 (26) коммутатор 7 (27) поступает в формирователь адреса 8 (28). При П01явлевии очередной мёткв в поле 16 (32) вновь осуществляется перетактовка и из одного блока памяти ПОДР5Щ считывается две микрокоманды, а затем работа продолжается аналогично описанному выше: из блоков 1О и 30 поочередно считываются очередные микрокоманды. При появлении метки в поле 15 (33) регистра (31) устройство переходит во второй режим работы. Реализация параллельных микроподпрограмм. После считывания метки единичным сигналом, проходящим через элемент ИЛИ 24, триггер 25 устанавливается в единичное состояние, открывая элементы И 20 и 41, а также коммутаторы 5О и 51 цля прохождения тактовых импульсов с выхода 69. Причем до момента срабатывания триггера 25 адрес из поля 12 (36) регистра 11 (31) проходит через коммута тор 27 (7) в регистр 29 (9). С задерж кой на время переключения двух элементов эта цепь прохождения адреса блокируется и тот же самый адрес поступает из поля 12 (Зе) через коммутатор 7 (2 в регистр 9 (29). Поступление адреса ПО этой цепи разрешается вследствие появления единичного сигнала на выходе элемента И 2Q (41), а затем элемента ИЛИ 6 (26), Содержимое поля адреса 36 (12) при этом в регистр 29 (9) не поступает вследствие блокирования этой адресной цепи сигналом с выхояа поля 15 (33). Таким обрезом, перед считыванием первых микрокоманд параллельных микроподпрограмм в регистрах 9 и 29 записаны одинаковые коды, посту- пившие из адресного поля 12 (36) регистра 11 (31). Т.е. начальные адреса параллельных микроподпрограмм, начинающихся в одной теяке разветвления, совпадают. По этимь адресам затем по перь вому тактовому импульсу, проход5паему с выхода 69 формирователя;-42 через ко мутаторы 50 и 51, элементы И 55 и 54, на блоков 10 и 30 памяти соответственно, стпсронно считываются микрокоманды параллельных микроподпрограмм. Операционные их части чер элементы ИЛИ 37 поступают на выход 7 устройства, а адресные части из попей 1 и 36 параллельно записьшаютсЯ через коммутаторы 7 и 27 соответственно в регистры 9 и 29. Очередным тактовым импульсом с выхода 69 формирователя 4 происходит параллельное считывание микрокоманд из блоков 1О и 30 памяти. В дальнейшем эта два канала продолжают свою работу параллельно и нёзавиеямо. После окончания одной из мнкроподпрограмм (например, первой, которая хра нится в блоке 1О памяти) в поле 14 регистра 11 появляется метка М и триггер 17 устанавливается в единичное состояние (фиг. 4). Элемент И 55 блокируется нулевым сигналом с выхода элемента И-ЛЕ 53 и тактовые импульсы на управляющий вход 67 блока Ю памяти не подаются. Данный канал переходит в режим ожидания и находится в нем до окс91чания выполнения второй микропоц- программы. После появления метки М в поле 34 регистра 31 устанавливается в единичное состояние триггер 39, пооле чего сигналом с выхода элемента И 18 осуществляется сравнение содержимого полей 12 и 36 схемой 1. Если адресные части последних микрокоманд совпадают, то сигналом с выхода элемента И 2, проходящим через элементы ИЛИ 6 и 26, разрешается передача адреса в регистры 9 и 29i Затем с задержкой одновибратор 38 производит обнуление триггеров 17, 25 и 39, открываются элементы И 54 и 55 и первым тактовым импульсом с выхода 70 или 71 (это зависит от того, по какому импульсу произведено считывание последней микрокоманды второй параллельной микроподпрограммы) происходит считывание первой микрокоманды очередной последовательной микроподпрограммы. Эта макрокоманда записана в блоках 10 и ЗО памяти по одному адресу, что исзитючает потерю такта при считывании. Операционнью и адресные частя этих микрокоманд совпадают, отличаются они только значением .метки М. В дальнейшем работа устройства продолжается в первом режиме в соответствии с описанным выше алгоритмом. Рассмотрим особенности работы средств контроля устройства при реализации параллельных микроподпрограмм. После установки триггеров 17 и 39 в единичное состояние производится сравнение адресных частей микрокоманд регистров 11 и 31. В случае их неравенства сигнал с выхода элемента И 3, проходя через элемент ИЛИ 4, производит обнуление триггера 5, который блокирует подачу тактовых импульсов от генератора 43. Кроме того, на выходе 58 злемен. га ИЛИ 19 формируется сигнал ошибки,, свидетельствующий о нарушении работы устройства. Сигнал ошибки формируется также и в случае, когда микрооперация Конец операции на выходе 73 появляется при выполнении параллельного участка микропрограммы. При этом сигнал проходит через открытый элемент И 4О и элемент ИЛИ 19, оповещая об искажении мгскропрограммы. Таким образом, срецства контроля поэ вотают обнаруживать сбои и отказы ацресиьк цепей устройства, приводящие к перехопу из зон последовательных микропоцпрограмм в зону параллельных микропоапрограмм и наоборот. Преплагаемое микропрограммное устрсАство управления в отличии от извест ного позволяет реализовать как последовательные, так и параллельнью цисципЛИНЫ вьй1бянения микропрсдрамм, что аает возможность сократить общее время их, вьшолнения. lO 25 Кроме того, осуществляется управление синхронизацией, что позволяет сократить потери времени и памяти на переход i от нечетных (четных) к нечетным (че-сь. ным) микрокомандам, а организация контроля параллельных микроподпрограмм, реализованная в устройстве, позволяет уменыиить время между возникновением. и обнаружением отказа, а следовательно, уменыиить общее время выполнения микропрограмм за счет сокращения времен их восстановления, что, соответственно, повыщает производительность.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1166110A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Устройство для управления и диагностирования | 1984 |

|

SU1174930A1 |

1. МИКРОПРОГРАММ НОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти микрокоманп первый и второй регистры адреса, 1Ю1)вый и второй регистры микрокоманд, ilepebdi и второй коммутаторы, формировагепь тактовых импульсов, первый и вторсй формирователи адреса, первый и второй триггеры управления, первый и второй элементы И, блок алеиентов ИЛИ,, причем входы логических условий устройства соединены с первыми информационШьши входами первого и второго формирователей адреса, выходы которых соединены с первыми входами соответЬтвенно первого: и второго регистров адреса, вход кода операции устройства соединен . с вторыми информационными входами йёрвшго и второго регистров адреса, выходы которых соединены с информационными входами соответственно первого и второго блока памяти микрокоманд, выходы первого и второго элементов И соединены с управляющими входами соответственно 1юрвого и второго блоков памяти микрокоманд, выходы которых соединены с входами соответственно первого и второго регистров микрокоманд, первые управляю шие выходы первого и второго регистров микрокоманд соединены с единичными входами соответственно первого и второго триггеров управления, выходы микроопераций первого и второго регистров микро команд соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход которого является выходом микроопераций устройства, выход адреса первого регистра микрокоманд соединен с первыми информационными входами первого и второго коммутаторов, выход адреса второго регистра микрокоманд соединен с вторыми информационными входами первого и второго коммутаторов,; выходы которых соединены с вторыми (Л информационными входами соответственно первого и второго формирователей адреса, отличающееся тем, что, с целью повьщ1ения производительности, в устройство дополнительно введены схема сравнения, третий, четвертый и пятый триггеры управления, третий и вертый коммутаторы, третий, четвертый, о пятый, шестой, седьмой и восьмс элемен00 ты И, первый, второй, третий, четвертый, ю гштый, шестой и седьмой элементы ИЛИ, первый и второй элементы И-НЕ и одноСП вибратор, причем вход кода операции ycTV ройства через первый элемент ИЛИ соединен с единичными входом третьего триггера управления, единичный выход которого соединен с входом формирова- . теля тактовых импульсов, первый выход формирователя тактовых импульсов соединен с нулевыми входами триггеров полей микроопераций первого и второго регистров микрокоманд и с первыми информационными вхопами третьего и чеч%

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1972 |

|

SU437072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-05-30—Публикация

1982-02-18—Подача