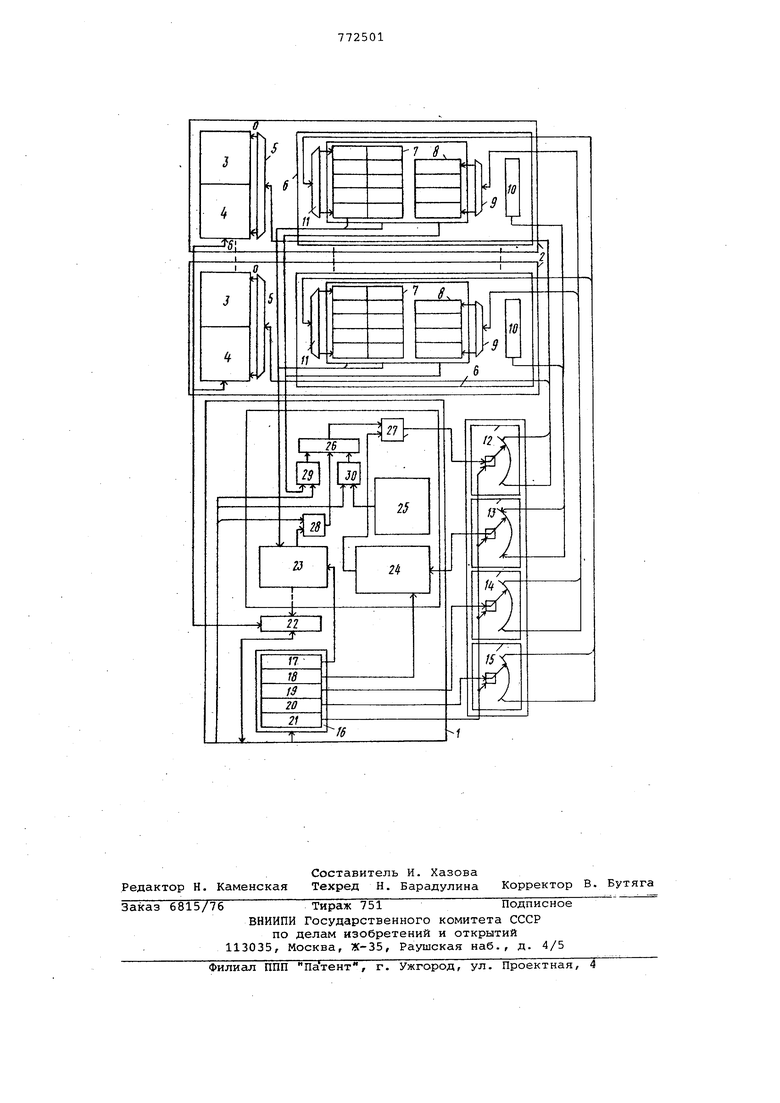

Изобретения относится к области вычислительной техники. Известна вычислительная система l}, содержащая процессор, селектор ные каналы, внешние устройства с блоками управления. Недостатками системы являются недостаточные функ циональные возможности и гибкость. Наиболее близким к данному изобретению по технической сущности является устройство 2 , состоящее из одного компьютера с процессором и с запоминающим устройством для хранения программ и данных, где функции переключательного оборудов ния контролируются компьютерами так же, как и данные о состоянии исполнительных переключательных пр боров хранятся в форме командных колонок в запоминающем устройстве для программ и в форме групп данны в запоминающем устройстве для хран ния данных и адресуются, обрабатываются и изменяются посредством процессора. Недостатком такого уст ройства являются недостаточные воз можности при адресации к внешним устройствам. Целью изобретения является расш рение функциональных возможностей за счет обеспечения управления независимо от изменения значения адресных параметров устройств обработки . Поставленная цель -достигается тем, что в компьютер, солержашиП центральный процессор и устройства обработки данных, каждоа из которих содержит блок управления, вве;сны селектор адреса, селектор состояний, селектор номера перехода, селектор номера переменной, а каждый из блоков управления со юржит память программ, память данных, дешифратор адреса и перепрограммируямую память, состоящую из регистров данных и регистров переходов, дешифратора номера переменной, де-, шифратора номера перехода и регистра кодовых состояний, причем выходы дешифратора адреса соединены с адресными входами памяти программ и памяти данных, выходы дешифратора номера переменной соединены со входами регистров данных, выходы дешифратора номера перехода соединены со входами регистров переходов, причем процессор содержит регистр., операционных параметров, информлционный регистр, формировато-чъ алрсса, память состояний, арифметический блок, регистр номера адреса и элементы И, причем выход памяти состо ний соединен с первым входом перво го элемента и, второй вход которого соединен с выходом регистра номера адреса, а выход - через селек тор адреса с входами дешифраторов адреса всех блоков управления, выход регистра номера индекса соединен с первым входом формирователя адреса, второй вход которого соеди нен с выходами регистров данных вс блоков управления, выход формирова теля адреса через второй элемент И соединен с первым входом регистра номера адреса, второй и третий вхо ды которого соединены с выходами третьего и четвертого элементов И, входы которых соединены соответственно с выходами арифметического блока и выходами регистров переходов всех блоков управления, выход регистра управляющего номера соеди нен со вторым входом памяти состоя ний, выход регистра номера переход через селектор номера перехода сое динён со входами дешифраторов номе ра перехода всех блоков управления выход регистра номера переменной через селектор номера переменной со единен со входами дешифраторов номе ра переменной всех блоков управлени выход регистра номера блока соедине с управляющими входами всех селекто ров , выходы регистров кодовых состо яний всех блоков управления через селектор состоянии соединены со вхо дом памяти состояний, цепи записисчитывания памяти данных соединены с информационным регистром, второй вход которого соединен со вторым выходом формирователя адреса. Схе} ла компьютера приведена на чертеже. Она содержит центральный процессор 1, устройства обработки данных с блоками управления 2, память прогpa 1M 3, память данных 4, дешифраfор адреса 5, перепрограммируемую память 6, регистры данных 7, регист ры переходев 8, дешифратор номера перехода 9, регистр кодовых состояний 10, дешифратор номера переменной -11, селектор адреса 12, селектор состояний 13, селектор номера перехода 14, селектор номера переменной 15, регистры операционных параметров 16, включающие регистр номера индекса 17, регистр управляющего номера 18, регистр номера перехода 19, регистр номера переменной 20, регистр номера блока 21 информационный регистр 22, формирователь адреса 23, память состояний 24, арифметический блок 25, регистр номера адреса 26, элементы И 27, 28, 29, 30. Каждый блок управления 2 независимо от его принадлежности к компьютеру, или собственно к системе, управляемой компьютером, содержит свою собственную память программ 3 и память данных 4 с адресными входами, цепями записи и считывания, которые связаны с информационным регистром 22 процессора. Каждый блок управления содержит также перепрограк-1мируемую память б, связанную с процессором. Для того, чтобы стало возможным формирование адресных входов памяти программ и данных иным способом, а не посредством перепрограммируемой памяти, адресные сигналы декодируются известным способом в адресном дешифраторе 5. Что касается взаимодействия устройств 2 и перепрограм лируемкх памятей 6, то основная идея этого заключается в том, что каждая перепрограммируемая память содержит регистры, в которых хранятся границы параметров адресации в структуре данных соответствующей памяти программ и данных и, которые необходимы для вычисления адресов в кзмандах и словах. Так как методы вычисления адреса являются одними и теми же для всех блоков управления, то для всех перепрограммируемых памятей имеется селекторное устройство и блок вычисления адреса, которое содержит арифметический блок 25 (например сумматор +1), регистр номера адреса 26 и формирователь адреса 23. Блоки управления распределя отся с помощью блочных номеров, а селектор устанавливается с помощью номера блока, которые записываются с помощью процессора в регистр номера блока 21. Посредством этого один из блоков управления вызывается для операции по обработке данных. Процессор 1 включает ряд регистров операционных параметров 16, из которого операционные параметры передаются к блоку вычисления адреса. Благодаря комбинации параметров адресации и операционных параметров в блоке вычисления адреса, последний вычисляет номер адреса команды или слова в памяти программ или данных, вызванного блока управления. Вычисленный номер адреса регистрируется во время текущей работы в регистре номера адреса 26 и передается через селектор адреса 12 к соответствующему адресному дешифратору 5. Состояние соответствующего устройства обработки данных регистрируется в форме двоичного кода на регистраторе кодовых состояний 10, с помощью которого, например, можно определить, что блок находится в нормальном рабочем состоянии, что па;Г1 ь i;|;: 1;ул:,& :з;иру):саетс; колонко

команд, что переменные обновляются, ччо Олик исиь 1ывается. Селектор состояния 13 связывает состояние

регистра кодовых состояний 10 вызванного блока с памятью состояний 24 в процессоре 1. Память состоянии открывающая или запрещающая элемент И 27, определяет благодаря существующему состоянию блока и управляющему числу, может.ли номер адреса быть передан к дешифратору 5 вызванного блока управления. Во вспомогательном регистре 18 процессора указывается управляющий номер, который заключает в себе номер вызванного блока. Регистр 26 связан через элемент И 27 с селектором адреса 12 выходы которого соединены с дешифраторами 5 блоков управления.

В данном компьютере так называемая глобальная команда переходасодержит операционные параметры, которые указывают к какому блоку управления должен быть сделан переход и с позиции в переходе внутри колонки команды должна быть начата обработка данных. Однако, позиция перехода выражается не посредством номера адреса, а посредством так называемого номера перехода. Преимущество использования номеров перехода состоит в том, что в связи с конструированием и изменением блока управления без учета структуры колонок команд, определенно доказывается, что вхождение в переход быть сделано при работе с помощью определения соответствующего номера перехода. Вышеуказанная операция вхождения в переход является одной из функций, которая выполняется блоком управления и остается неизменной даже при перестройке, операция получает новый серийный номер в колонке команд соответствующей памяти програм.м 3. Регистр номера перехода 19 связан с селектором номера перехода 14, который передает номер перехода к дешифратору ноперепрограммируемои

-,мера перехода

памяти выбранного блока управления. Дешифратор номера перехода 9 связан с регистрами переходов 8 таким образом, чтобы считывался тот регистр перехода, который принадлел ит к передаваемому номеру перехода. В регистрах перехода 8 регистрируются серийные номера, каждый из которых определяет в соответствии с колонкой команды различие межлу номером адреса для первой команды, номера адресной колонки, и адресом для вхождения в позицию перехода, определяемым одним из номеров перехода. Выходы считывания всех регистров перехода во всех перепрограммируемых памятях 6 связаны с адресных вычислений. Однако, если .

предположить, что номер адресной колонки каждой памяти программ находится в состоянии О, то регистры перехода 8 связыЕвются непосредственно с регистром номера адреса 26, который работает взаимосрязанно с блоком 25. В соответствии с номером перехода, регистр 26 получает и регистрирует номер адреса, который после передачи через элемент И 27 и селектор адреса 12 к адресноoму дешифратору 5 вызванного блока управления, адресует команду с предназначенным номером перехода.

В данном компьютере команда считывания или записив память данных

5 4 содержит не только номер блока в запросе, но и операционные параметры, которые указывают семейства командной переменной, и, для групповых переменных индексный номер устройства обработки.

0

Род переменной определяется с помощью так называемого номера пе- . ременной. Преимущество использования номеров переменных заключается в том, что команды считывания и запи5си остаются Е еизменными, если деление изменяется внутри запоминаю щих областей пере енных и групп переменных вызванной памяти данных. Регистр номера переменной

0 ,20 через селектор номера переменкой 15 связан с выбранным блоком управления, селектор номера переменной --ередает номер переменной дешифратору номера переменной 11,

5 который соединен с регистром дан-, ных 7, в результате чего, регистр данных считывает то, что относится к передаваемому номеру переменной, и который согласно вышеописанному,

0 регистрирует номер адреса памяти данных, который содержит начало группы переменных, определяемое в соответствии с номером переменной и числом бит в переменной в д;;нной группе. Содержимое выбранного ре5гистра данных и содержимое регистра номера индекса 17 передается к формирователю адреса 23, который передает на регистр 26 номер адреса слова, которое должно быть счи0тано или записано и определяет позиции бит соответствующей переменной в информационном регистре 22,

Таким образом данное изобретение

5 позволяет расширить функциональные возможности компьютера за счет обеспечения управления внешними устройствами независимо от изменений значений адресных параметров устройств обработки.

0

Формула изобретения

Управляющий компьютер, содер-каи111й .центральный процессор и устройства

Обработки данных, каждое из которы содержит блок управления, отличающийся тем, что, с целью

расширения функциональных возможностей за счет обеспечения управления независимо от изменения значений адресных параметров, он содержит селектор адреса, селектор состоний, селектор номера перехода, селектор номера переменной, а каждый из блоков управления содержит пдмять программ, память данных, дешифратор адреса и перепрограммируемую память, состоящую из регистров данных, регистров переходов, дешифратора номера переменной, дешифратора номера перехода и регистра кодовых состояний, причем выходы дешифратора адреса соединены с адре ными входами памяти программ и памяти данных, выходы дешифратора номера переменной соединены со входами регистров данных, выходЬл дешифратора номера перехода соединены со входами регистров переходов, причем центральный процессор содержит регистры операционных параметров, информационный регистр, формирователь адреса, память состояний, арифметический блок, регистр номера адреса и элементы И, причем выход памяти состояний соединен с первым входом, первого элемента И, второй вход которого соединен с выходом регистра номера адреса, а выход - через селектор адреса с входами дешифраторо

адреса всех блоков управления, выхо регситра номера индекса соединен с первым входом формирователя адреса, второй вход которого соединен

с выходами регистров данных всех блоков управления, выход формирователя адреса через второй элемент И соединен с первым входом регистра номера адреса, второй и третий входы , которого соединены с выходами третьего и четвертого элементов И, входы которых соединены соответственно с выходами арифметического блока и выходами регистров переходов всех

6ЛС1КОВ управления, выход регистра

управляющего номера соединен со вторым входом памяти состояний,вйход регистра номера перехода через селектор номера перехода соединен со входами дешифраторов номера перехода всех блокоп управления, выход регистра номера переменной через селектор номера переменной соединен со входами дешифраторов номера переменной всех блоков управле0 НИН, выход регистра номера блока

соединен с управляющими входами всех селекторов, выходы регистров кодовых состояний всех блоков управления через селектор состояний соединены

5 со входом памяти состояний, цепи

записи-считывания памяти данных соединены с информационным регистром, второй вход которого соединен со вторым выходом формирователя адре.. са.

Источники информации,

принятые во внимание при экспертизе

1.Флорес А. Организация ВМ, М., Мир, 1972, гл. 9, рис.9.2.1,

2.Журнал Японская телекоммуни5 кация Об. т. 13, 3 и т. 14, № 1, .

Электронная переключающая система Д-10.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между процессором и периферийными устройствами | 1983 |

|

SU1167615A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Устройство для отладки программ | 1979 |

|

SU849218A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для сопряжения магистрали ЭВМ с магистралью внешних устройств | 1984 |

|

SU1246105A1 |

| Процессор ввода-вывода с коррек-циЕй ОшибОК | 1979 |

|

SU849221A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

Авторы

Даты

1980-10-15—Публикация

1974-04-08—Подача