00

о

00

ю

ю

Изобретение относится к области вычислительной техники и может быть использовано в управляющих системах и системах сбора информации.

Цель изобретения - повышение быстродействия.

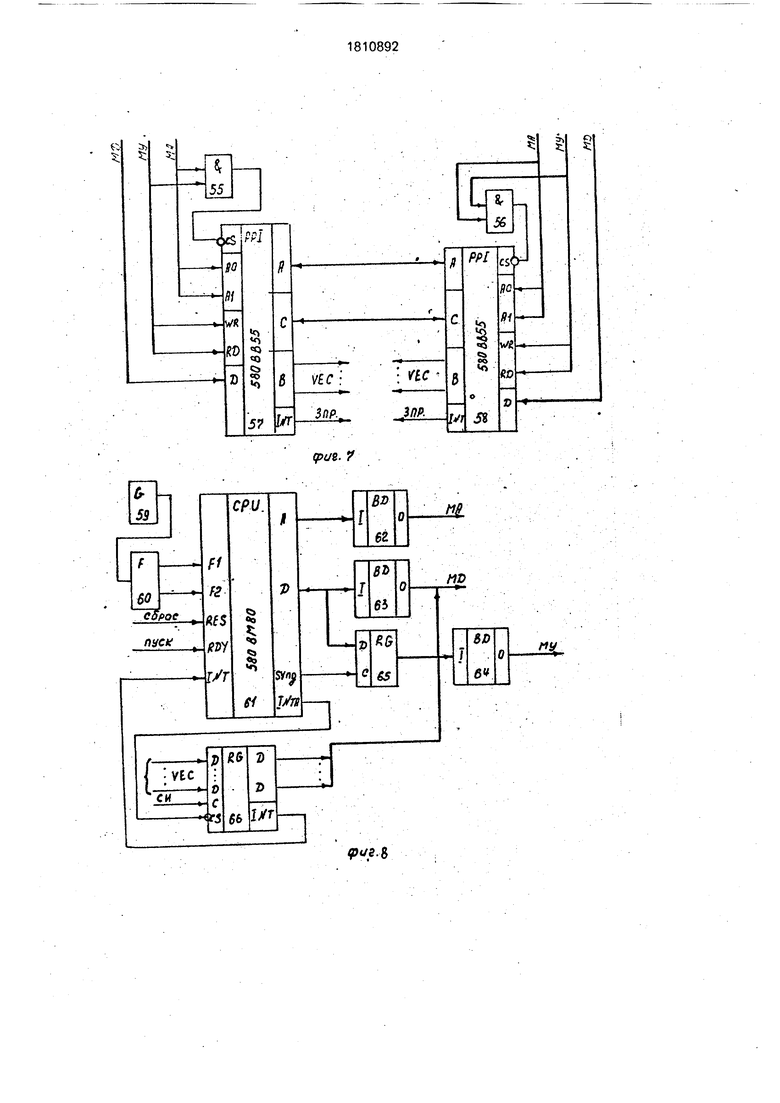

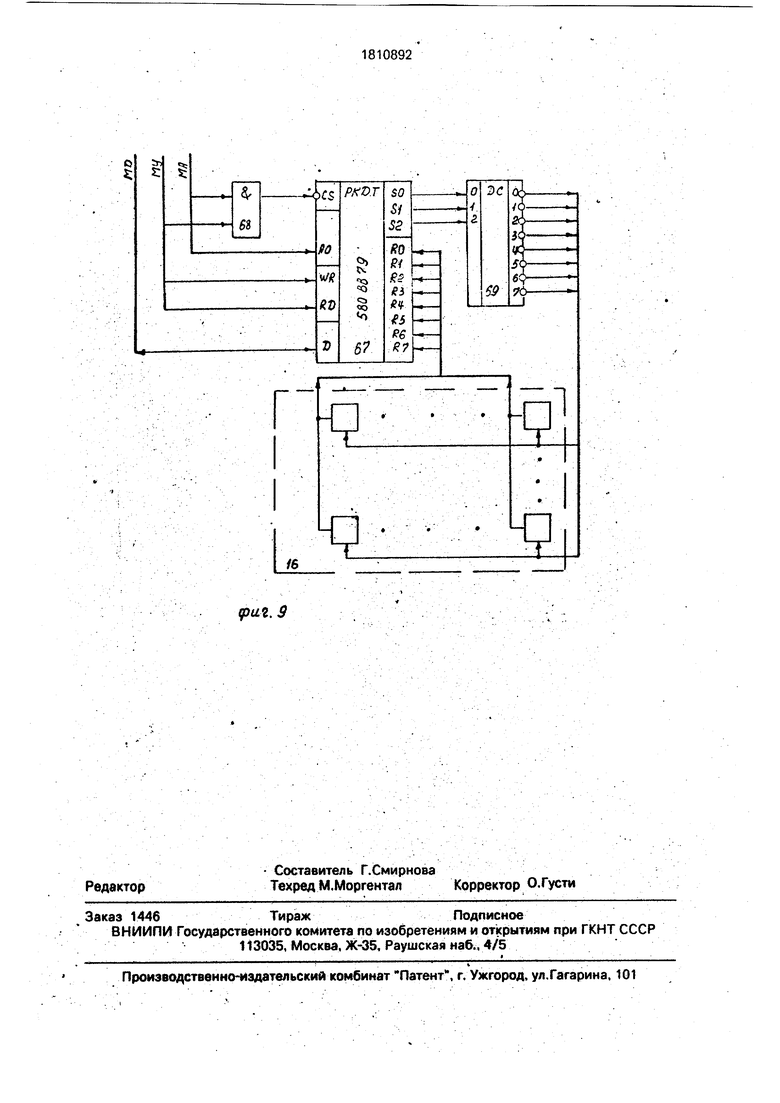

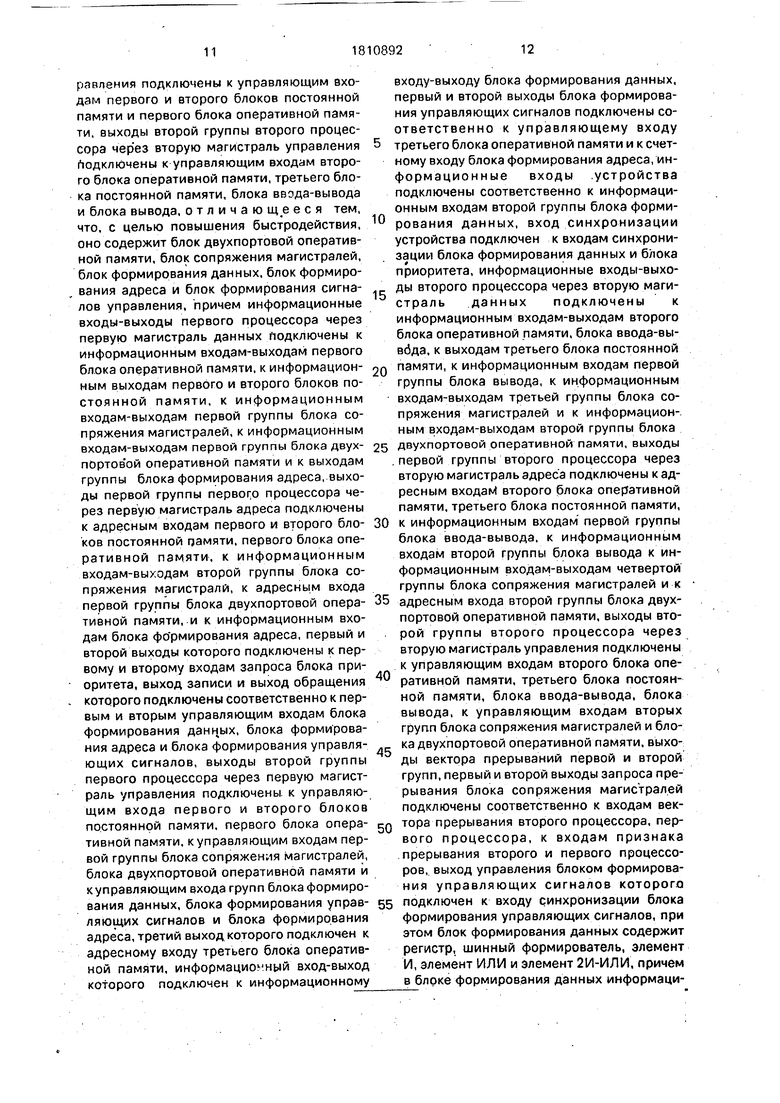

На фиг.1 представлена блок схема микропроцессорного устройства; на фиг.2 - функциональная схема блока формирования данных; на фиг.З - функциональная схема блока формирования управления; на фиг.4 - функциональная схема блока формирования адреса; на фиг.5 - функциональная .схема первого процессора; на фиг.б - функциональная схема двухпортового ОЗУ; на фиг.7 - функциональная схема блока сопряжения магистралей; на фиг.8 - функциональная схема второго процессора; на фиг.9

-функциональная схема блока сопряжения с клавиатурой и сама клавиатура.

Микропроцессорное устройство содержит блок формирования данных 1. формиро- вания сигналов управления 2, формирования адреса 3, первый блок оперативной памяти 4, блок приоритета 5, пер вый процессор 6, первый блок постоянной памяти 7, сегменты кода (CS), второй блок постоянной памяти сегмента прерываний 8, второй блок оперативной памяти 9 сегмента стека, блок двухпортовой оперативной памяти 10, блок сопряжения магистралей 11, второй процессор 12, третий блок оперативной памяти 13, третий блок постоянной памяти 14, блоки ввода и вывода 16, 15. блок сопряжения с индикаторной панелью 17, индикаторную панель 18, электронику МС- 6205, блок сопряжения с печатающим устройством 19, печатающее устройство 20. Кроме того на фиг.1 приведены следующие обозначения: МД - магистраль данных, МА

- магистраль адреса, МУ - магистраль управления.

Процессоры 6 и 12 через магистрали данных (МД) управления (МУ) и адреса (МА) соединены с входами двухпортового ОЗУ-10 и входами блока сопряжения 11, выходы которого соединены со входами запроса прерывания и входами векторов прерывания процессоров 6 и 12.

Первый процессор 6 через магистрали данных, управления и адреса соединен с блоками постоянной памяти 7, 8 оперативной памяти 9 и с блоками формирования адреса 3, магистралью управления, с блоком 2 формирования сигналов управления и магистралями управления и данных, с блоком 1 формирования даннч, имеющим информационные входы и вход

синхроимпульсов, при этом вход-выход блока 1 соединен с входом-выходом блока 4 буферного ОЗУ, два других входа которого соединены с выходами блоков формирова- ния 2 и 3.

Вход синхроимпульсов блока 5 приоритета соединен с входом синхроимпульсов устройства, входы требования Тр 1, Тр 2

-с выходами блока 3 формирования адреса, а выходы записи Зап и обращения Обр

- с входами блоков формирования данных 1, управления 2 и адреса 3, счетный G вход которого соединен с выходом блока 2, вход

g тактовой частоты (т.ч.) которого подключен к соответствующему выходу процессора 6.

Процессор 12 магистралями адреса,: данных и управления соединен с блоком оперативной памяти 13 и блоком постоян0 ной памяти 14 и с устройствами ввода-вывода (блоки 15, 17, 19).

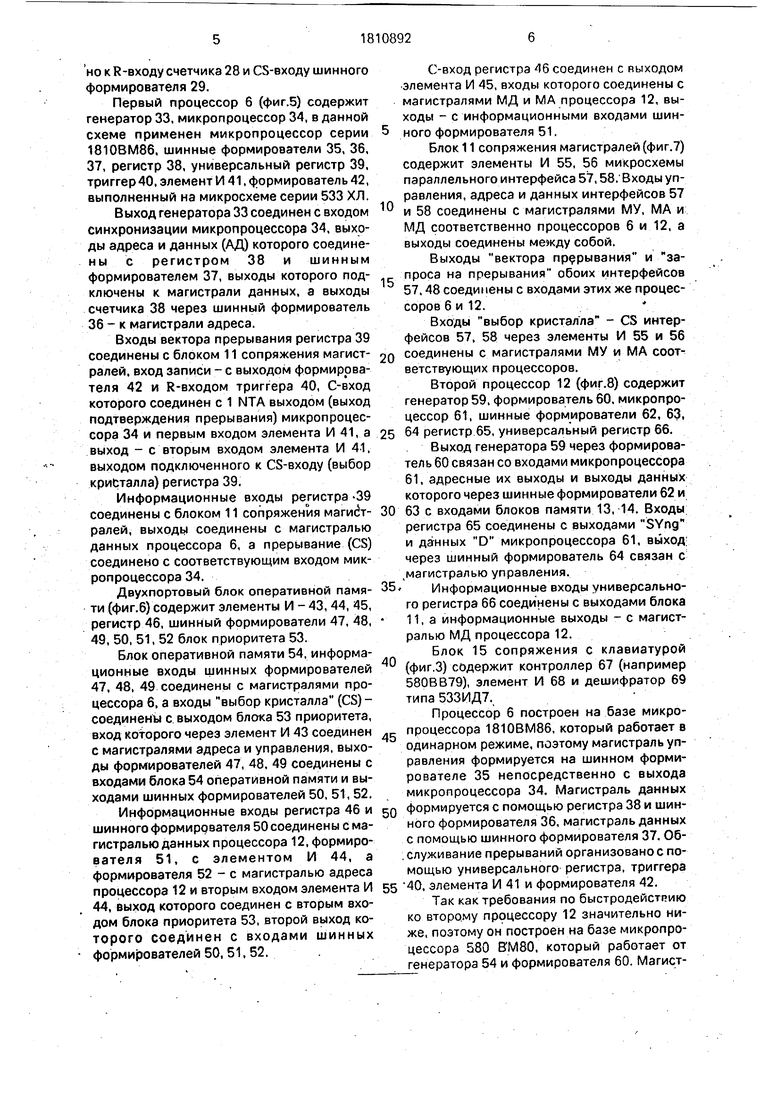

Блок 1 формирования данных (фиг.2) содержит регистр 2.1, элемент коммутации 22, . элемент ИЛИ 23, элемент И 24, шинный

5 формирователь 25, в качестве которого может быть применен шинный формирователь.

Разрядные входы и вход синхронизации регистра 21 появляются информационными

0 входами устройства, выходы всех разрядов подключены через элемент коммутации 22 или шинный формирователь 25, к входу блока ОЗУ-4, вход CS соединен с выходом элемента ИЛ И 23, а вход IE с выходом элемента

5 и 24.

Входы элемента коммутации 22, элемента ИЛИ 23 и элемента И 24 - с блоком приоритета 5.

Блок 2 формирования сигналов управления (фиг.З) содержит распределитель им- пульсов 26, который через элемент коммутации 27, например микросхема серии 533АЛ, подключен ко входу управления 5 блока ОЗУ-4.

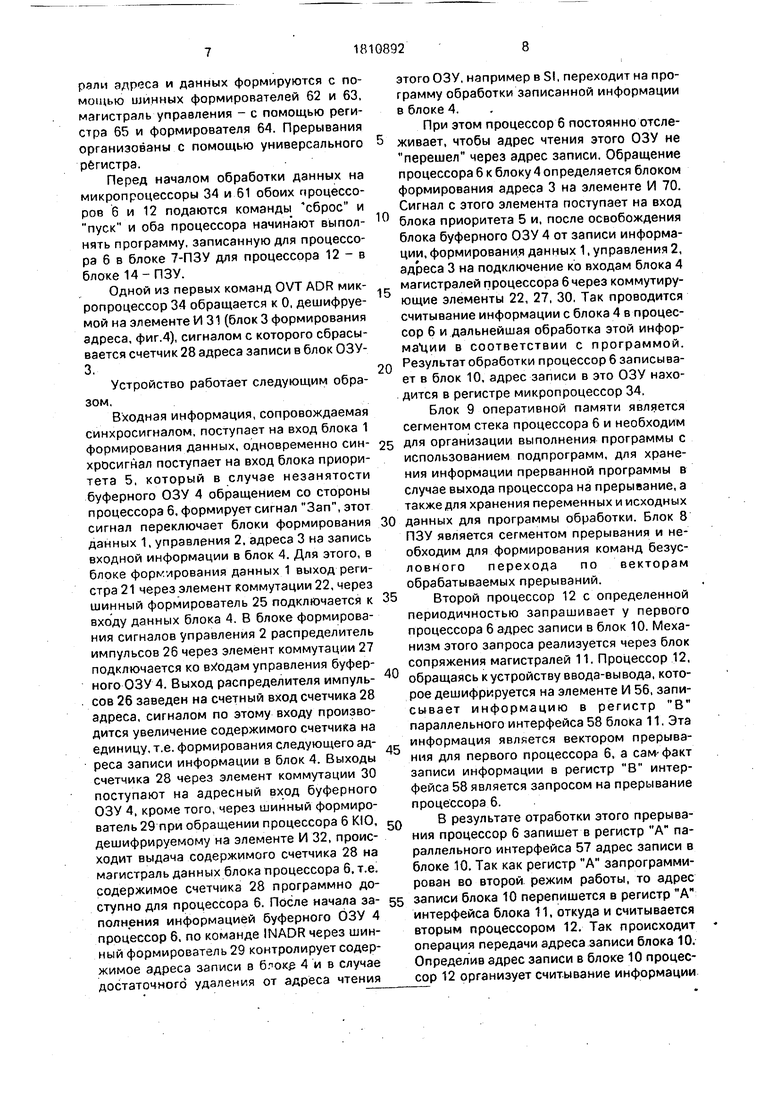

Блок 3 формирования адреса (фиг.4) содержит-счетчик 28, шинный формирователь 29, элемент коммутации 30, элементы И 31, 32.70.

0 Счетный вход счетчика 28 соединен с блоком 2 формирования управления, разрядные выходы через элемент коммутации 30 соединены с блоком 4, а шинный формирователь 29 соединены с магистралью дан- 5 ных(МД).

Первые входы элементов И 31, 32, 70 соединены с магистралью данных, а вторые

- с магистралью управления, выходы элементов И 31, 32 подключены соответствен0

но к R-входу счетчика 28 и CS-входу шинного формирователя 29.

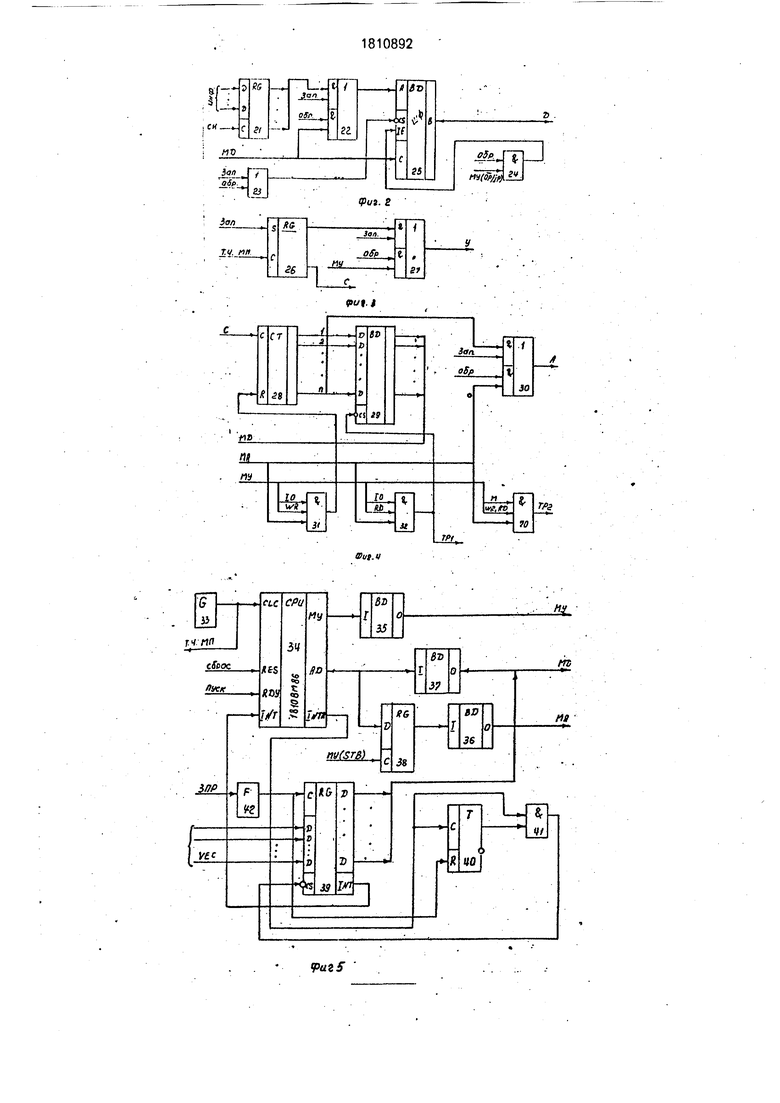

Первый процессор 6 (фиг.5) содержит генератор 33, микропроцессор 34, в данной схеме применен микропроцессор серии 1810ВМ86, шинные формирователи 35, 36, 37, регистр 38, универсальный регистр 39, триггер40, элемент И 41, формирователь 42, выполненный на микросхеме серии 533 ХЛ.

Выход генератора 33 соединен с входом синхронизации микропроцессора 34, выходы адреса и данных (АД) которого соедине- ны с регистром 38 и шинным формирователем 37, выходы которого подключены к магистрали данных, а выходы счетчика 38 через шинный формирователь 36 - к магистрали адреса.

Входы вектора прерывания регистра 39 соединены с блоком 11 сопряжения магистралей, вход записи - с выходом формирователя 42 и R-входом триггера 40, С-вход которого соединен с 1 NTA выходом (выход подтверждения прерывания) микропроцессора 34 и первым входом элемента И 41, а выход - с вторым входом элемента И 41, выходом подключенного к CS-входу (выбор кристалла) регистра 39.

Информационные входы регистра-39 соединены с блоком 11 сопряжения магисЧ- ралей, выходы соединены с магистралью данных процессора 6, а прерывание (CS) соединено с соответствующим входом микропроцессора 34.

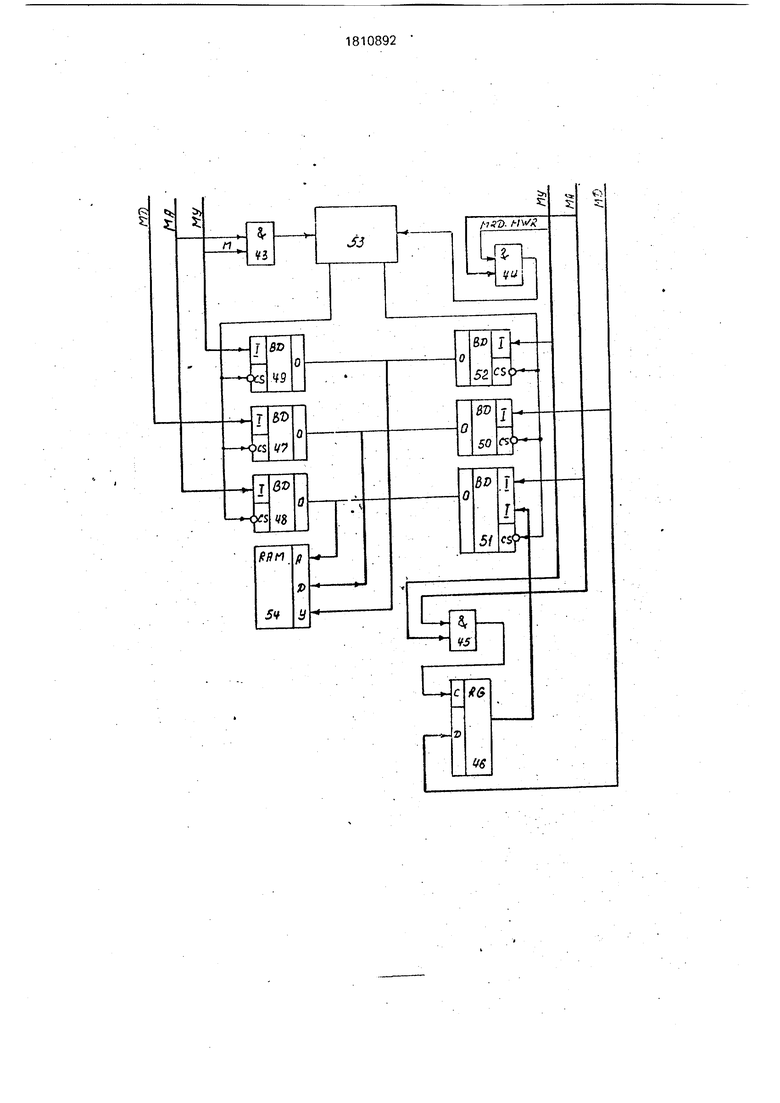

Двухпортовый блок оперативной памяти (фиг.6) содержит элементы И - 43, 44, 45, регистр 46, шинный формирователи 47, 48, 49, 50, 51, 52 блок приоритета 53.

Блок оперативной памяти 54, информационные входы шинных формирователей 47, 48, 49 соединены с магистралями процессора 6, а входы выбор кристалла (CS) - соединены с выходом блока 53 приоритета, вход которого через элемент И 43 соединен с магистралями адреса и управления, выходы формирователей 47, 48, 49 соединены с входами блока 54 оперативной памяти и выходами шинных формирователей 50, 51, 52.

Информационные входы регистра 46 и шинного формиррвателя 50 соединены с магистралью данных процессора 12, формирователя 51, с элементом И 44, а формирователя 52 - с магистралью адреса процессора 12 и вторым входом элемента И 44, выход которого соединен с вторым входом блока приоритета 53, второй выход которого соединен с входами шинных формирователей 50, 51, 52.

5

С-вход регистра 46 соединен с выходом элемента И 45, входы которого соединены с магистралями МД и МА процессора 12, выходы - с информационными входами шин- 5 ного формирователя 51.

Блок 11 сопряжения магистралей (фиг.7) содержит элементы И 55, 56 микросхемы параллельного интерфейса 57,58. Входы управления, адреса и данных интерфейсов 57 ® и 58 соединены с магистралями МУ, МА и МД соответственно процессоров 6 и 12, а выходы соединены между собой.

Выходы вектора прерывания и запроса на прерывания обоих интерфейсов 57.48 соединены с входами этих же процессоров 6 и 12.

Входы выбор кристалла - CS интерфейсов 57, 58 через элементы И 55 и 56 0 соединены с магистралями МУ и МА соответствующих процессоров.

Второй процессор 12 (фиг.8) содержит генератор 59, формирователь 60, микропроцессор 61, шинные формирователи 62, 63, 5 64 регистр 65, универсальный регистр 66.

Выход генератора 59 через формирователь 60 связан со входами микропроцессора 61, адресные их выходы и выходы данных которого через шинные формирователи 62 и 0 63 с входами блоков памяти 13, 14. Входы регистра 65 соединены с выходами SYng и данных D микропроцессора 61, выход; через шинный формирователь 64 связан с .магистралью управления. 5 Информационные входы универсального регистра 66 соединены с выходами блока 11, а информационные выходы - с магистралью МД процессора 12.

Блок 15 сопряжения с клавиатурой (фиг.3) содержит контроллер 67 (например 580В В79), элемент И 68 и дешифратор 69 типа533ИД7.

Процессор 6 построен на базе микро- .. процессора 1810ВМ86, который работает в

Ь

одинарном режиме, поэтому магистраль управления формируется на шинном формирователе 35 непосредственно с выхода микропроцессора 34. Магистраль данных

Q формируется с помощью регистра 38 и шинного формирователя 36, магистраль данных с помощью шинного формирователя 37. 06- , служивание прерываний организовано с помощью универсального регистра, триггера

5 40, элемента И 41 и формирователя 42.

Так как требования по быстродействию ко второму процессору 12 значительно ниже, поэтому он построен на базе микропроцессора 580 ВМ80, который работает от генератора 54 и формирователя 60. Магистрали адреса и данных формируются с помощью шинных формирователей 62 и 63, магистраль управления - с помощью регистра 65 и формирователя 64. Прерывания организованы с помощью универсального регистра.

Перед началом обработки данных на микропроцессоры 34 и 61 обоих процессоров 6 и 12 подаются команды сброс и пуск и оба процессора начинают выполнять программу, записанную для процессора 6 в блоке 7-ПЗУ для процессора 12 - в блоке 14-ПЗУ.

Одной из первых команд OVT ADR микропроцессор 34 обращается к 0, дешифруемой на элементе И 31 (блок 3 формирования адреса, фиг.4), сигналом с которого сбрасывается счетчик 28 адреса записи в блок ОЗУ- 3.

Устройство работает следующим образом.

Входная информация, сопровождаемая синхросигналом, поступает на вход блока 1 формирования данных, одновременно синхросигнал поступает на вход блока приоритета 5, который в случае незанятости буферного ОЗУ 4 обращением со стороны процессора 6, формирует сигнал Зап, этот сигнал переключает блоки формирования данных 1, управления 2, адреса 3 на запись входной информации в блок 4. Для этого, в блоке формирования данных 1 выход регистра 21 через элемент коммутации 22, через шинный формирователь 25 подключается к входу данных блока 4. В блоке формирования сигналов управления 2 распределитель импульсов 26 через элемент коммутации 27 подключается ко вводам управления буферного ОЗУ 4. Выход распределителя импульсов 26 заведен на счетный вход счетчика 28 адреса, сигналом по этому входу производится увеличение содержимого счетчика на единицу, т.е. формирования следующего адреса записи информации в блок 4. Выходы счетчика 28 через элемент коммутации 30 поступают на адресный вход буферного ОЗУ 4. кроме того, через шинный формирователь 29 при обращении процессора 6 KIO, дешифрируемому на элементе И 32, происходит выдача содержимого счетчика 28 на магистраль данных блока процессора 6. т.е. содержимое счетчика 28 программно доступно для процессора 6. После начала заполнения информацией буферного ОЗУ 4 процессор 6, по команде INADR через шинный формирователь 29 контролирует содержимое адреса записи в блоке 4 и в случае достаточного удаления от адреса чтения

этого ОЗУ, например в SI, переходит на программу обработки записанной информации в блоке 4.

При этом процессор 6 постоянно отслеживает, чтобы адрес чтения этого ОЗУ не перешел через адрес записи. Обращение процессора 6 к блоку 4 определяется блоком формирования адреса 3 на элементе И 70. Сигнал с этого элемента поступает на вход

блока приоритета 5 и, после освобождения блока буферного ОЗУ 4 от записи информации, формирования данных 1, управления 2, адреса 3 на подключение ко входам блока 4 j. магистралей процессора 6 через коммутирующие элементы 22, 27, 30, Так проводится считывание информации с блока 4 в процессор 6 и дальнейшая обработка этой инфор- матдии в соответствии с программой.

Q Результат обработки процессор 6 записывает в блок 10, адрес записи в это ОЗУ находится в регистре микропроцессор 34.

Блок 9 оперативной памяти является сегментом стека процессора 6 и необходим

5 для организации выполнения программы с использованием подпрограмм, для хранения информации прерванной программы в случае выхода процессора на прерывание, а также для хранения переменных и исходных

0 данных для программы обработки. Блок 8 ПЗУ является сегментом прерывания и необходим для формирования команд безусловного перехода по векторам обрабатываемых прерываний.

5 Второй процессор 12с определенной периодичностью запрашивает у первого процессора 6 адрес записи в блок 10. Механизм этого запроса реализуется через блок сопряжения магистралей 11. Процессор 12,

обращаясь к устройству ввода-вывода, которое дешифрируется на элементе И 56,записывает информацию в регистр В параллельного интерфейса 58 блока 11. Эта информация является вектором прерывания для первого процессора 6, а сам- факт записи информации в регистр В интерфейса 58 является запросом на прерывание процессора 6.

Q В результате отработки этого прерывания процессор 6 запишет в регистр А параллельного интерфейса 57 адрес записи в блоке 10. Так как регистр А запрограммирован во второй режим работы, то адрес

5 записи блока 10 перепишется в регистр А интерфейса блока 11, откуда и считывается вторым процессором 12. Так происходит операция передачи адреса записи блока 10. Определив адрес записи в блоке 10 процессор 12 организует считывание информации

5

из этого блока и вывод ее на печатающее устройство и индикаторную панель Электроника МС-6205, Так как второй процессор 12 построен на микропроцессоре 580ВМ80, магистраль адреса которого меньше (16 разрядов) магистрали адреса 1810ВМ86, которая имеет 20 разрядов, то. для формирования адреса считывания из блока 1.0 старшие разряды адреса считывания записываются в его регистр как в 10 с помощью элемента И 45, а младшие разряды берутся непосредственно из магистрали адреса процессора 12. В блоке 10 с помощью блока приоритета 53 разрешаются спорные ситуации при одновременном обращении к нему двух процессоров путем их последовательного подключения. За счет высокого быстродействия этого ОЗУ последовательное обслуживание запросов не отражается на работе обоих процессоров. В случае, если блок 10 предоставляется первому процессору 6, то через его шинные формирователи 47,48, 49 входы собственного блока памяти подключаются к магистрали первого процессора 6, если блок 10 предоставляется второму процессору 12, то к блоку памяти подключаются магистрали второго процессора. Программа работы процессора 12 хранится в блоке 14 - постоянной памяти (ПЗУ), а стек организован на базе блока 13 оперативной памяти (ОЗУ).

Набор исходных данных для обработки входной информации производится с клавиатуры 16 и блока сопряжения с клавиатурой 15.

Этот блок состоит из контроллера клавиатуры 580ВВ79-67 и дешифратора 69, обращение к контроллеру клавиатуры производится с помощью элемента И 68.

В процессе набора исходных данных производится их индикация на панели 18, в случае обнаружения ошибки программа набора исходных данных эта информация переписывается в двухпортовое ОЗУ 10 через магистраль данных, затем формируется команда прерывания первому процессору 6 (по описанной схеме). В результате обработки этой команды процессор 6 прочитает исходные данные в ОЗУ 10, преобразует их к виду, удобному для процесса обработки информации и перепишет в верхнюю часть сегмента стека, блок 9 ОЗУ. После окончания этой работы процессор 6 переходит на обработку входной информации и в свою очередь дает прерывание процессору 12 через блок сопряжения магистралей 11. По этому сигналу прерывания процессор 12 индицирует на панели 18 сообщение о начале обработки информации и переходит в режим ее документального представления с одновременным отображением на панели 18.

Таким образом, весь поток информации записывается в блоке 4 для исключения потерь при неравномернее.™ обработки во времени и первый процессор б считывает из ОЗУ 4 информацию, определяет вид этой

информации, наиболее важную (время и сообщение об изменении режима) сразу через процессор 12 передает на индикацию. Следовательно, первый процессор ведет обраt. ботку всего потока информации в темпе поступления ее.

Второй процессор 12 обеспечивает вывод информации на печать и отображение, при этом информация считывается из блока

n 10 и преобразовывается к виду, удобному для вывода. Т.к. эти процессы медленно изменяющиеся, то и требования по быстродействию ко второму процессору ниже.

25

Формула изобретения

Устройство обработки информации, содержащее первый и второй процессоры, с первого по третий блоки постоянной памяти, с первого по третий блоки оперативной памяти, блок приоритета, блок ввода-вывода и блок вывода, причем информационные входы-выходы первого процессора подключены через первую магистраль данных к инч} ормационному входу-выходу первого

блока оперативной памяти и к выходам первого и второго блоков постоянной памяти,

информационные входы-выходы второго

процессора подключены через вторую магистраль данных к информационным входам- выходам второго блока оперативной памяти, к выходам третьего блока постоянной памяти, к информационным входам-выходам блока ввода-вывода и к информационным входам первой группы блока вывода, выходы первой группы первого процессора через первую адресную магистраль подключены к адресным входам

первого и второго блоков постоянной памяти и первого блока оперативной памяти, выходы первой группы второго процессора через вторую адресную магистраль подключены к адресным входам второго блока оперативной памяти, третьего блока постоянной памяти, к информационным входам первой группы блока ввода-вывода и к информационным входам второй группы блока вывода, выходы второй группы первого процессора через первую магистраль управления подключены к управляющим входам первого и второго блоков постоянной памяти и первого блока оперативной памяти, выходы второй группы второго процессора через вторую магистраль управления подключены к управляющим входам второго блока оперативной памяти, третьего блока постоянной памяти, блока ввода-вывода и блока вывода, отличаю щ%е е с я тем, что, с целью повышения быстродействия, оно содержит блок двухпортовой оперативной памяти, блок сопряжения магистралей, блок формирования данных, блок формирования адреса и блок формирования сигналов управления, причем информационные входы-выходы первого процессора через первую магистраль данных подключены к информационным входам-выходам первого блока оперативной памяти, к информационным выходам первого и второго блоков постоянной памяти, к информационным входам-выходам первой группы блока сопряжения магистралей, к информационным входам-выходам первой группы блока двух- портов ой оперативной памяти и к выходам группы блока формирования адреса, выходы первой группы первого процессора через первую магистраль адреса подключены к адресным входам первого и второго блоков постоянной памяти, первого блока оперативной памяти, к информационным входам-выходам второй группы блока сопряжения магистрали, к адресным входа первой группы блока двухпортовой оперативной памяти,.и к информационным входам блока формирования адреса, первый и второй выходы которого подключены к первому и второму входам запроса блока приоритета, выход записи и выход обращения которого подключены соответственно к первым и вторым управляющим входам блока формирования данных, блока формирования адреса и блока формирования управляющих сигналов, выходы второй группы первого процессора через первую магистраль управления подключены, к управляющим входа первого и второго блоков постоянной памяти, первого блока оперативной памяти, к управляющим входам первой группы блока сопряжения магистралей, блока двухпортовой оперативной памяти и к управляющим входа групп блока формирования данных, блока формирования управляющих сигналов и блока формирования адреса, третий выход которого подключен к адресному входу третьего блока оперативной памяти, информационный вход-выход которого подключен к информационному

0

5

0

5

0

5

0

5

0

5

входу-выходу блока формирования данных, первый и второй выходы блока формирования управляющих сигналов подключены со- ответственно к управляющему входу третьего блока оперативной памяти и к счетному входу блока формирования адреса, информационные входы .устройства подключены соответственно к информационным входам второй группы блока формирования данных, вход синхронизации устройства подключен к входам синхронизации блока формирования данных и блока приоритета, информационные входы-выходы второго процессора через вторую магистраль данных подключены к информационным входам-выходам второго блока оперативной памяти, блока ввода-вывода, к выходам третьего блока постоянной памяти, к информационным входам первой группы блока вывода, к информационным входам-выходам третьей группы блока сопряжения магистралей и к информацион-, ным входам-выходам второй группы блока двухпортовой оперативной памяти, выходы .первой группы второго процессора через вторую магистраль адреса подключены к адресным входам второго блока оперативной памяти, третьего блока постоянной памяти, к информационным входам первой группы блока ввода-вывода, к информационным входам второй группы блока вывода к информационным входам-выходам четвертой группы блока сопряжения магистралей и к адресным входа второй группы блока двухпортовой оперативной памяти, выходы второй группы второго процессора через вторую магистраль управления подключены к управляющим входам второго блока оперативной памяти, третьего блока постоянной памяти, блока ввода-вывода, блока вывода, к управляющим входам вторых групп блока сопряжения магистралей и блока двухпортовой оперативной памяти, выходы вектора прерываний первой и второй групп, первый и второй выходы запроса прерывания блока сопряжения магистралей подключены соответственно к входам вектора прерывания второго процессора, первого процессора, к входам признака прерывания второго и первого процессоров, выход управления блоком формирования управляющих сигналов которого подключен к входу синхронизации блока формирования управляющих сигналов, при этом блок формирования данных содержит регистр, шинный формирователь, элемент И, элемент ИЛИ и элемент 2И-ИЛИ, причем в блоке формирования данных информационные входы первой группы блока формирования данных подключены к информационным входам шинного формирователя и к входам первой группы элемента 2И-ИЛИ, выход которого подключен к первому управляющему входу шинного формирователя, информационные входы-в ыходы которого подключены соответственно к информационным входам-выходам блока формирования данных, информационные входы второй группы и вход синхронизации которого подключены соответственно к информационным; входам .и к входу записи- считывания регистра, выходы которого подключены соответственно к входам второй группы элемента 2И-ИЛИ, первый управляющий вход блока формирования данных подключен к первому входу элемента 2И-ИЛИ, к первому входу элемента ИЛИ, выход которого подключен к инверсному входу синхронизации шинного формирователя, второй управляющий вход блока формирования данных подключен к второму входу элемента ИЛИ, к второму входу элемента 2И-ИЛИ и к входу элемента И, группа входов и выход которого подключены соответственно к управляющим входам группы блока формирования данных и к второму управляющему входу шинного формирова - теля, при этом блок формирования сигналов управления содержит распределитель импульсов и элемент 2И-ИЛИ, причем в блоке формирования сигналов управления первый управляющий вход подключен к входу запуска распределителя импульсов и к первому входу элемента 2И-ИЛИ, выход которого подключен к первому выходу блока формирования сигналов управления, второй управляющий вход и вход синхронизации которого подключены соответственно к второму входу элемента 2И-ИЛИ и к входу синхронизации распределителя импульсов, группа выходов и выход которого подключены соответственно к входам первой группы элемента 2И-ИЛИ и к второму выходу блока формирования сигналов управления, управляющие входы группы которого подключены к входам второй группы элемента

2И-ИЛИ, при этом блок формирования адреса содержит счетчик, шинный формирователь, элемент 2И-ИЛИ и три элемента И, причем в блоке формирования адреса информационные входы подключены к входам первых групп первого, второго и третьего элементов И и элемента 2И-ИЛИ, управляющие входы группы блока формирования адреса подключены к входам вторых групп первого, второго и третьего элементов И, выход первого элемента И подключен к входу установки в О счетчика, информационные выходы которого подключены к входам второй группы элемента 2И-ИЛИ и к информационным входам шинного формирователя, выходы которого подключены соответственно к выходам группы блока формирования адреса, счетный вход которого подключен к счетному входу счетчика, выход второго элемента-И подключен к инверсному управляющему входу шинного формирователя и к первому выходу блока формирования адреса, выход третьего элемента И подключен к второму выходу блока формирования адреса, первый и второй управляющие входы которого подключены соответственно к первому и второму входам элемента 2И-ИЛИ, выход которого подключен к третьему выходу блока.

5

0

5

0

5

.С

K6

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сбора информации | 1988 |

|

SU1605273A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Многоканальное устройство передачи информации со сжатием | 1989 |

|

SU1665399A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Двухпортовое устройство сопряжения в вычислительной системе | 1982 |

|

SU1156080A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для контроля вычислительного процесса ЭВМ | 1988 |

|

SU1596332A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении управляющих систем и систем сбора информации. Цель изобретения - повышение быстродействия. Поставленная цель-достигается тем, что устройство содержит блок 1 формирования данных, блок 2 формирования сигналов управления, блок 3 формирования адреса, приоритета, первый процессор 6, блоки оперативной памяти 4, 9, и 13, блоки постоянной памяти 7, 8 и 14, блок 10 двухпортовой оперативной памяти, второй процессор 12, блоки ввода и вывода 16, 15, блок 17 сопряжения с индикаторной панелью, индикаторную панель 18, блок 19 сопряжения с печатающим устройством и печатающее устройство 20. 9 ил.

, СИ --4Si

ПУСК

/Г

ГУЯ

wttrA) .

3ffft ,

«&

2)

We

T

.

yaaJ

3

JPC

44

/w

3s

v/

40

(put. 7

,g

& 58

CS

Л

wj «Z

фи. 9

so 5/ SS

ЭС

КО Kl RS «3

/Рб

IB

69

| 0 |

|

SU169909A1 | |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-04-23—Публикация

1989-01-02—Подача