(54) УСТГОЙСТВО ДЛЯ КОНТЮЛЯ ЛОГИЧЕСКИХ БЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для контроля постоянной памяти | 1979 |

|

SU777742A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1195392A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1184014A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

1

Изобретение относится к контрольно-измерительной технике и может быть использовано в сервисной аппаратуре электронно-вычислительных машин.

Известно устройство 1, в котором подача входных воздействий на объект контроля и оценка результатов производятся оператором.

К недостаткам этого устройства относятся низкая надежность и малое его быстродейстБне.

Наиболее близким по технической сущности к предлагаемому является устройство 2, принятое за прототип, содержащее генератор импульсов, выход которого подключен к входу синхронизации первого регистра, группа выходов которого подсоединена к соответствующей группе входов согласующего блока и группе первых информационнь1х входов первого сумматора по модулю два, выход которого подключен к информационному входу первого регистра, группа выходов согласующего блока подсоединена к группе входов блока индикации, элементы ИЛИ и элементы ИЛИ -НЕ, установочные входы которых подключены к

входу Сброс устройства, а установочные выходы - к установочным входам коммутатора соответственно.

Недостатком этого устройства является малое быстродействие, связанное с обработ1сой результатов на каждом выходе объекта контроля.

Цель изобретения - повыщение быстродействия устройства.

10

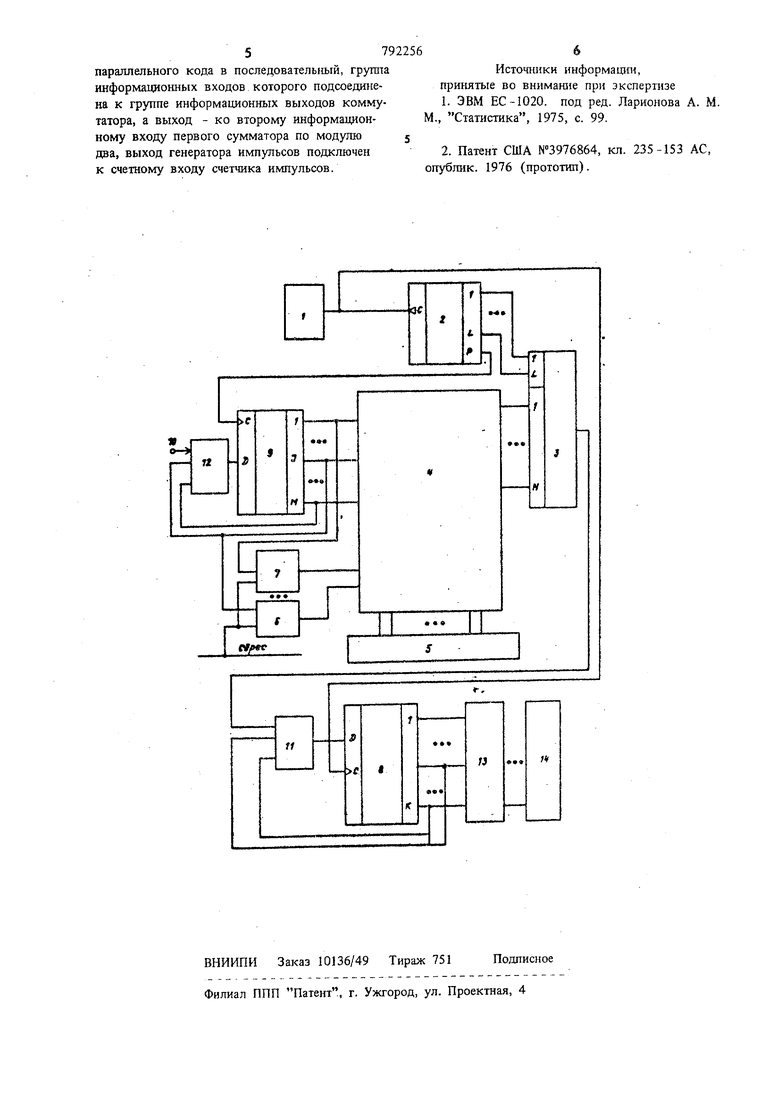

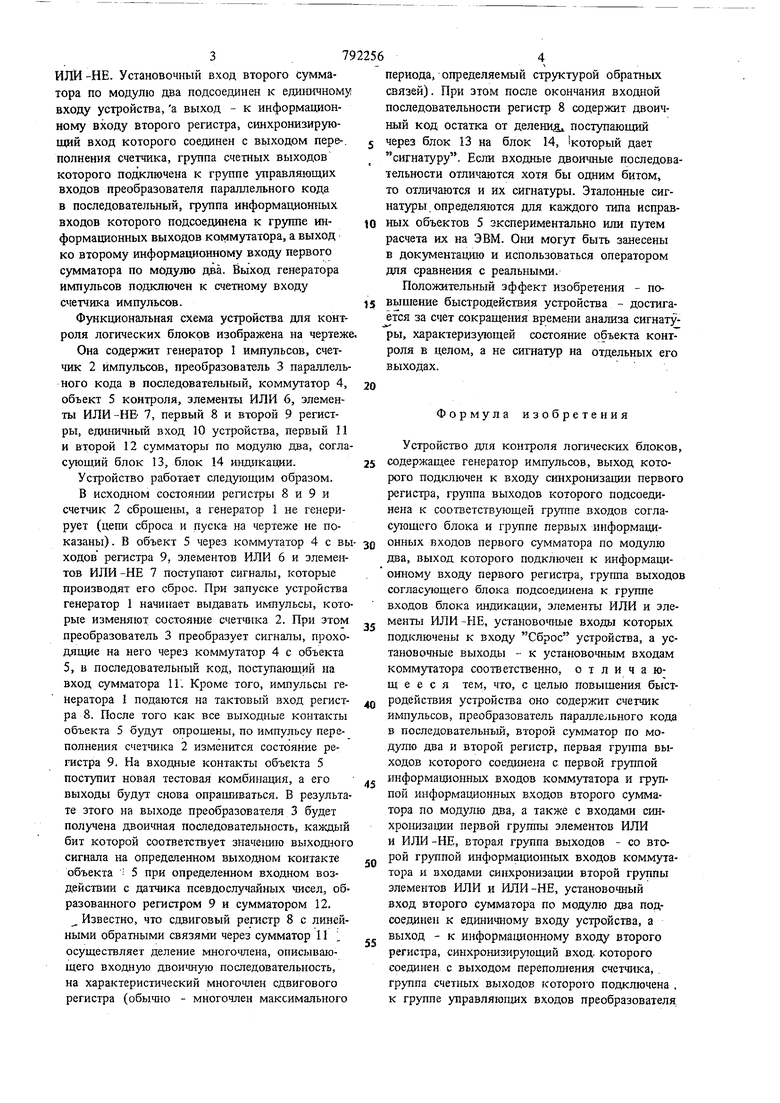

Указанная цель достигается тем, что устройство для контроля логических блоков содержит счетчик импульсов, преобразователь параллельного кода в последовательный, второй сумматор по модулю два и второй регистр, первая группа выходов которого соединена с первой грудпой информационных входов коммутатора н группой информацио1шых .к входов второго сумматора по модулю два, а также с входами синхронизации первой груп20пы элементов ИЛИ и ИЛИ - НЕ, вторая группа выходов - со второй грзшпой информационных входов коммутатора и входами синхронизащш второй группы элементов ИЛИ и 379 ИЛИ -НЕ. Установочный вход второго сумматора по модулю два подсоединен к eAfflOiMHOMy входу устройства, а выход - к информационному входу второго регистра, синхронизирующий вход которого соединен с выходом пере-, полнения счетчика, группа счетных выходов которого погцслючена к группе управляющих входов преобразователя параллельного кода в последовательный, группа икформациошшхх входов которого подсоединена к группе информационных выходов коммутатора, а выход ко второму информационному входу первого сумматора по модулю два. Выход генератора импульсов подключен к счетному входу счетчика импульсов. Функциональная схема устройства для контроля логических блоков изображена на чертеже Она содержит генератор 1 импульсов, счетчик 2 импульсов, преобразователь 3 параллельного кода в последовательный, коммутатор 4, объект 5 контроля, элементы ИЛИ 6, элементы ИЛИ -НЕ- 7, первый 8 и второй 9 регистры, еди1шчный вход 10 устройства, первый 11 и второй 12 сумматоры по модзлю два, согласующий блок 13, блок 14 индикации. Устройство работает следу ощим образом. В исходном состояшш регистры 8 и 9 и счетчик 2 сброшены, а генератор 1 не генерирует (цепи сброса и пуска на чертеже не показаны) . В объект 5 через коммутатор 4 с вы ходов регистра 9, элементов ИЛИ 6 и элементов ИЛИ -НЕ 7 поступают сигналы, которые производят его сброс. При запуске устройства генератор 1 начинает выдавать импульсы, кото рые изменяют состояние счетчика 2. При этом преобразователь 3 преобразует сигналы, проходящие на него через коммутатор 4 с объекта 5, в последовательный код, 1юсг пающий на вход сумматора И. Кроме того, импульсы генератора 1 подаются на тактовый вход регистра 8. После того как все выходные контакты объекта 5 будут опрошены, по импульсу переполнения счетчика 2 изменится состояние регистра 9. На входные контакты объекта 5 поступит новая тестовая комбинация, а его выходы будут снова опрахшгеаться, В результате этого на выходе преобразователя 3 будет получена двоичная последователыюсть, каждый бит которой соответствует значегшю выходного сигнала на определенном выходном контакте объекта 5 при определенном входном воздействии с датчика псевдослучайных чисел, образованного регистром 9 и сумматором 12. Известно, что сдвиговый регистр 8 с линейными обратными связями через сумматор 11 1 осуществляет деление многочлена, описывающего входную двоичную последовательность, на характеристический многочлен сдвигового регистра (обычно - многочлен максимального периода, определяемый структурой обратных связей). При этом после окончания входной последовательности регистр 8 содержит двоичный код остатка от делениа поступающий через блок 13 на блок 14, {который дает сигнатуру. Если входные двоичные последовательности отличаются хотя бы одним битом, то отличаются и их сигнатуры. Эталонные сигнатуры определяются для каждого типа исправных объектов 5 экспериментально шш путем расчета их на ЭВМ. Они могут быть занесены в документацию и использоваться оператором для сравнения с реальными. Положительный эффект изобретения - повышение быстродействия устройства - достигатся за счет сокращения време1ш анализа сигнатуры, характериз тощей состояние объекта контроля в целом, а не сигнатур на отдельных его выходах. Формула изобретения Устройство для контроля логических блоков, содержащее генератор импульсов, выход которого подключен к входу С1шхронизации первого регистра, группа выходов которого подсоединена к соответствующей грутша входов согласующего блока и группе первых информационных входов первого сумматора по модулю два, выход которого подключен к информационному входу первого регистра, группа выходов согласующего блока подсоедднена к группе входов блока индикации, элементы ИЛИ и элементы ИЛИ -НЕ, установомые входы которых подключены к входу Сброс устройства, а установочные выходы - к установочным входам коммутатора соответственно, отличающееся тем, что, с целью повыщения быстродействия устройства оно содержит счетчик импульсов, преобразователь параллельного кода в последовательный, второй сумматор по модугао два и второй регистр, первая гp)щa выходов которого соед}щена с первой группой информациогшых входов коммутатора и группой информационных входов второго сумматора по модулю два, а также с входами синхронизации первой группы элементов ИЛИ и ИЛИ -НЕ, вторая группа выходов - со второй группой информащюш1ых входов коммутатора и входами синхронизации второй группы элементов ИЛИ и ИЛИ -НЕ, установочный вход второго сумматора по модулю два подсоединен к единичному входу устройства, а выход - к информационному входу второго регистра, синхронизирующий вход, которого соединен с выходом переполнения счетчика, группа счетных выходов которого подключена , к группе управляющих входов преобразователя

параллельного кода в последовательный, группа информацио1шых входов которого подсоедтюна к группе информационных выходов коммутатора, а выход - ко второму информационному входу первого сумматора по модулю два, выход генератора импульсов подключен к счетному входу счетчика импульсов.

7922566

Источники информащш, принятые во внимание при экспертизе 1. ЭВМ ЕС-1020. под ред. Ларионова А. М. М., Статистика, 1975, с. 99.

Авторы

Даты

1980-12-30—Публикация

1979-01-08—Подача