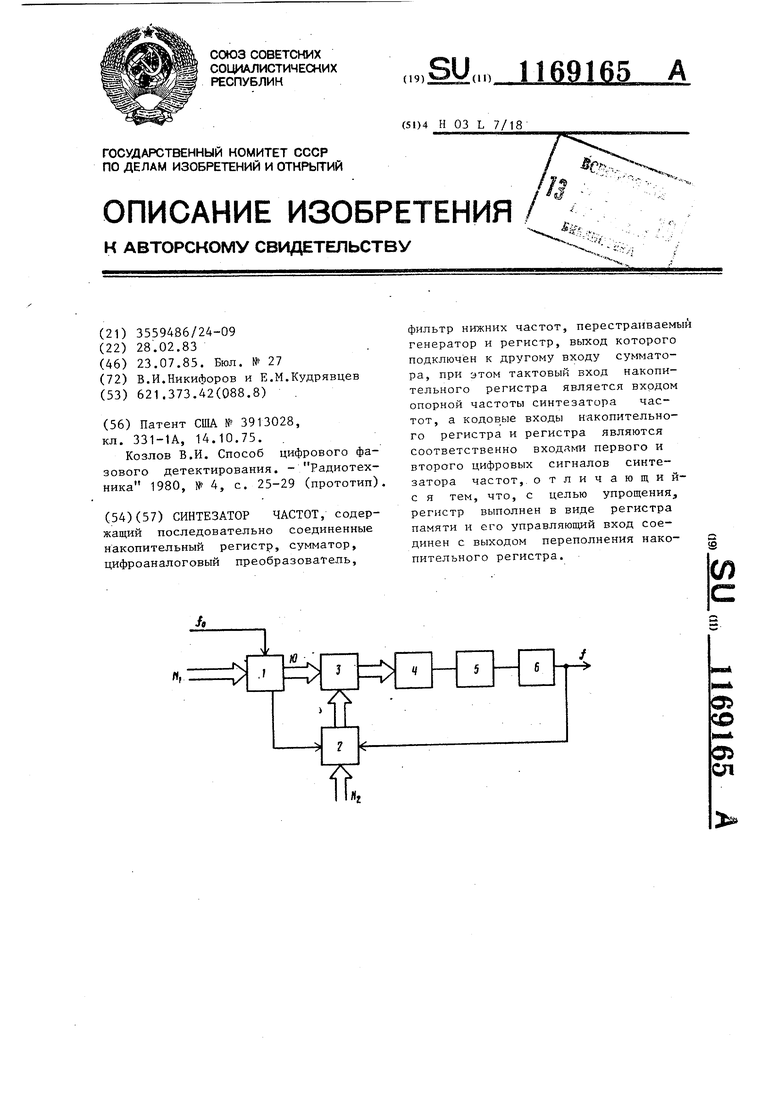

1 Изобретение относится к радиотех нике и может быть использовано для получения сетки стабильных частот в радиопередающей и измерительной аппаратуре. Цель изобретения - упрощение уст ройства. На чертеже изображена структур ная электрическая схема синтезатора частот. Синтезатор частот содержит накопительный регистр 1, регистр 2 п мяти, сумматор 3, цифроаналоговый преобразователь (ЦАП) 4, фильтр 5 нижних частот (ФНЧ), перестраиваемый генератор 6. Синтезатор частот работает следующим образом. Первый цифровой сигнал, соответствующий числу N) , поступает на кодовый вход накопительного регистра 1, который суммирует это число с содержимым памяти в момен ты прихода импульсов опорной частоты fy на тактовый вход накопительного регистра 1. Так как емкость памяти накопительного регистра 1 ограничена величиной Q 2 , где п - число двоич ных разрядов накопительного регис ра 1, то при ее переполнении соде жимое памяти уменьшается на Nj единиц, где ( Nj 5 Q , а процесс сложения вновь повторяется Очевидно, что область Значений, пр нимаемых числовой последовательностью, ограничена числом N ,которое принимается равным отношени опорной частоты к шагу сетки си тезируемых частот Д F . Средняя частота переполнения емкости памяти fp. N/ N2 . Однако в связи с тем, что отношение N в общем случае не равно целому числу, то образуется остаток, который накап ливается в течение нескольких циклов переполнения, пока не достигне величины NJ . В этом случае длител ность цикла переполнения увеличи вается на один период опорной частоты fp . в моменты переполнения емкости памяти накопительный регистр 1 формирует на выходе переполнения импульс. Полученная числовая последовательность не может быть использована непосредственно для управления частотой перестраи ваемого генератора 6, так как пос 52 тоянно накапливаемая ошибка не скомпенсирована в цифровом виде,i. Для зто-: го используется сумматор 3, на другой вход которого поступает сигнал с выхода регистра 2 памяти. Регистр 2 памяти выдает число N 2 при подаче импульсов с выхода переполнения накопительного регистра 1 и сбрасывает информацию на выходе в О при поступлении с выхода перестраиваемого генератора 6. ЦАП 4 преобразует результат сложения сумматора 3 в аналоговый сигнал, который после усреднения ФНЧ 5 поступает на управляющий вход перестраиваемого генератора 6. Момент выдачи регистром 2 памяти числа NJ совпадает по времени с уменьшением содержимого памяти первого накопительного регистра 1 на ту же величину NJ . В результате на выходе сумматора 3 числовая последовательность продолжает нарастать не изменяя шага и знака. В момент прихода импульса с перестраиваемоу го генератора 6 число Nj заменяется О, и сумма слагаемых на выходе сумматора 3 уменьшается на величину N- . В режиме синхронизма частота перестраиваемого генера-тора 6 постоянна, поэтому и сигнал, подаваемый на вход ЦАП4, также имеет постоянный период. Причем кольцо автоподстройки автоматически обеспечивает компенсацию временной неравномерности цифрового сигнала, сформированного накопительным регистром 1, этом необходимо выполнить условия ,чтобы обеспечить синхронизацию системы автоподстройки в широкой полосе частотных расстроек.Остальные параметры выбираются из следующих соотношений: о f f, N2 f-0 /t ; / F-fMa«/ F; -N f N, N, , МПИ «aКС Q 2 , у-чft W , где f,, , .c- соответственно минимальная и максимальная частоты диапазона. Время, в течение которого регистр 2 памяти выдает число Nj изменяется от периода к периоду пропорционально накапливаемой накопительным регистром 1 ошибке, а выходной сигнал сум3матора 3 имеет постоянный период Т 1/f ,причем средние значения 1169165. 4 постоянной составляющей равны в каждом периоде. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1983 |

|

SU1202054A1 |

| Синтезатор частот | 1982 |

|

SU1067603A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Синтезатор частот | 1987 |

|

SU1501265A1 |

| Синтезатор частот | 1988 |

|

SU1656680A1 |

| Синтезатор частот | 1982 |

|

SU1117839A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Синтезатор частот | 1980 |

|

SU868973A1 |

СИНТЕЗАТОР ЧАСТОТ, содержащий последовательно соединенные накопительный регистр, сумматор, цифроаналоговый преобразователь. фильтр нижних частот, перестраиваемый генератор и регистр, выход которого подключен к другому входу сумматора, при этом тактовый вход накопительного регистра является входом опорной частоты синтезатора частот, а кодовые входы накопительного регистра и регистра являются соответственно входами первого и второго цифровых сигналов синтезатора частот,, отличающийс я тем, что, с целью упрощения, регистр выполнен в виде регистра памяти и его управляющий вход соединен с выходом переполнения накоS пительного регистра. (Л

| Патент США № 3913028, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Козлов В.И | |||

| Способ цифрового фазового детектирования | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

Авторы

Даты

1985-07-23—Публикация

1983-02-28—Подача