информационным входом соответствующего D-триггера, выход - с соответст вуюищм входом элемента ИЛИ, четвертый вход - с инверсным выходом соответствующего D-триггера, причем информационный вход Ксзждого последующего D-триггера кроме первого соединен с прямым выходом предьщущего.

а информационный вход первого D-Tpnr-t гера соединен с выходом делителя частоты и с вторым входом элемента третий вход которого соединен с инверсным выходом первого из п D-триггеров, выход - с первым выходом управляемого фазовращателя,второй выход которого соединен с выходом элемента ИЛИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| Устройство для формирования тестов | 1987 |

|

SU1444781A1 |

| Фазовращатель | 1986 |

|

SU1406514A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1986 |

|

SU1420615A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Устройство для ввода информации | 1985 |

|

SU1327087A1 |

1. ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий генератор импульсов, выходную шину, первый блок управления, выход которого соединен с входом первого блока памяти, выход которого соединен с первым врсодом первого сумматора, второй вход которого соединен с выходом второго блока памяти, выход - с первым входом второго сумматора, выход которого . соединен с информационным входом второго блока памяти, второй вход - с первым выходом преобразователя кодов, первый вход которого соединен с первым выходом первого блока сравнения кодов, второй вход - с первым входом второго блока сравнения кодов и с выходом третьего блока памяти, вход которого соединен с выходом второго блока управления, второй вход второго блока сравнения кодов соединен с выходом счетчика импульсов, вход установки которого- соединен с входом ус-, тановки второго блока памяти и с выходом второго блока сравнения кодов, отличающийся тем, что, с целью повышения точности, в ,-него введены буферный регистр, блок сумматоров, третий сумматор и управляемый фазовращатель, первый вход которого соединен с выходом генератора импульсов,, второй вход - с входом буферного регистра, первый выход - с выходной шиной, второй выход - со счетным входом счетчика импульсов, с входами управления второго блока памяти и буферного регистра, инфор-. мационный вход которого соединен с вторым выходом первого блока сравнег ния кодов, первый вход которого сое(Л динен с выходом третьего сумматора, первый вход которого соединен с втос рым выходом преобразователя кодов, второй вход - с выходом первого сума матора, первый вход которого соедис нен с входом блока сумматоров, выход которого соединен с вторым входом . первого блока сравнения кодов. 2. Делитель по п.1, отличаю щ и и с я тем, что управляеО) мый фазовращатель содержит сдвиговый регистр из п D-триггеров, элемент И, группу из п элементов И, элемент ИЛИ и делитель 4acTotM, счетный вход которого соединен с входами управления каждого из п D-триггеров, с первыми входами элементов И группы из п элементов И, с первым входом элемента И и с первым входом .управляемого фазовращателя, второй вход которого имеет п входных шин, каждая из которых соединена с вторым входом соответствующего элемента И группы из п элементов И, третий вход каждого из которых соединен с

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, а также в синтезаторах частоты.

Цель - повышение точности работы устройства.

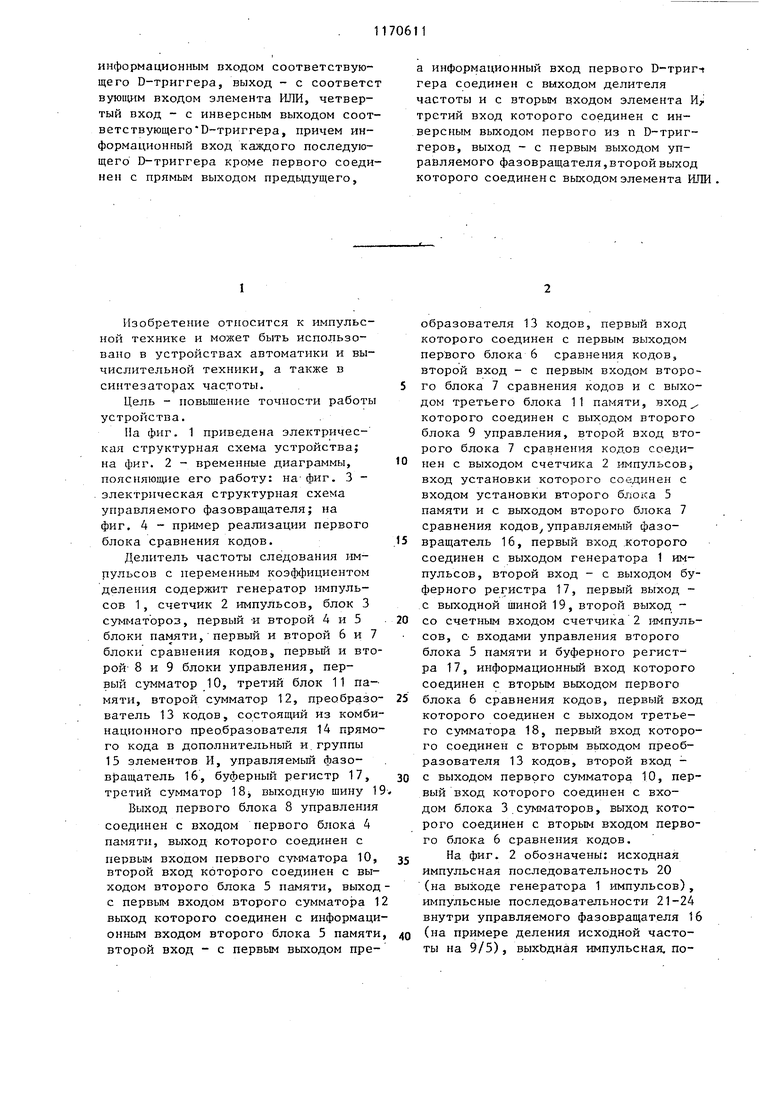

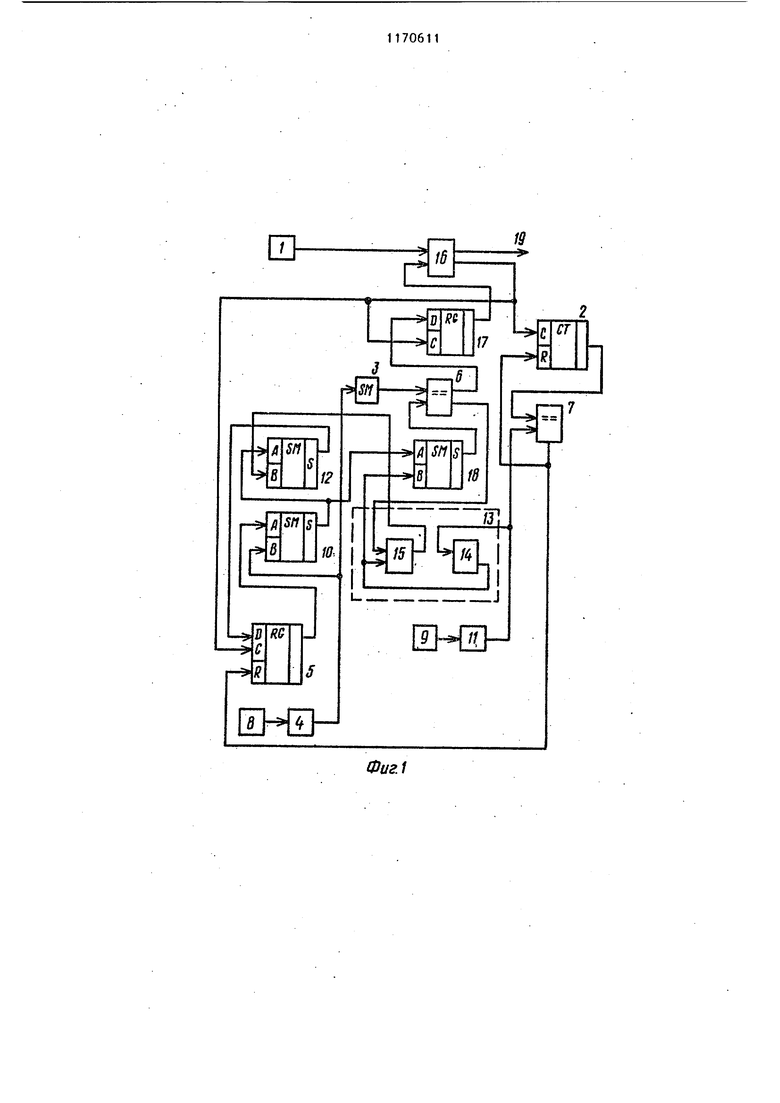

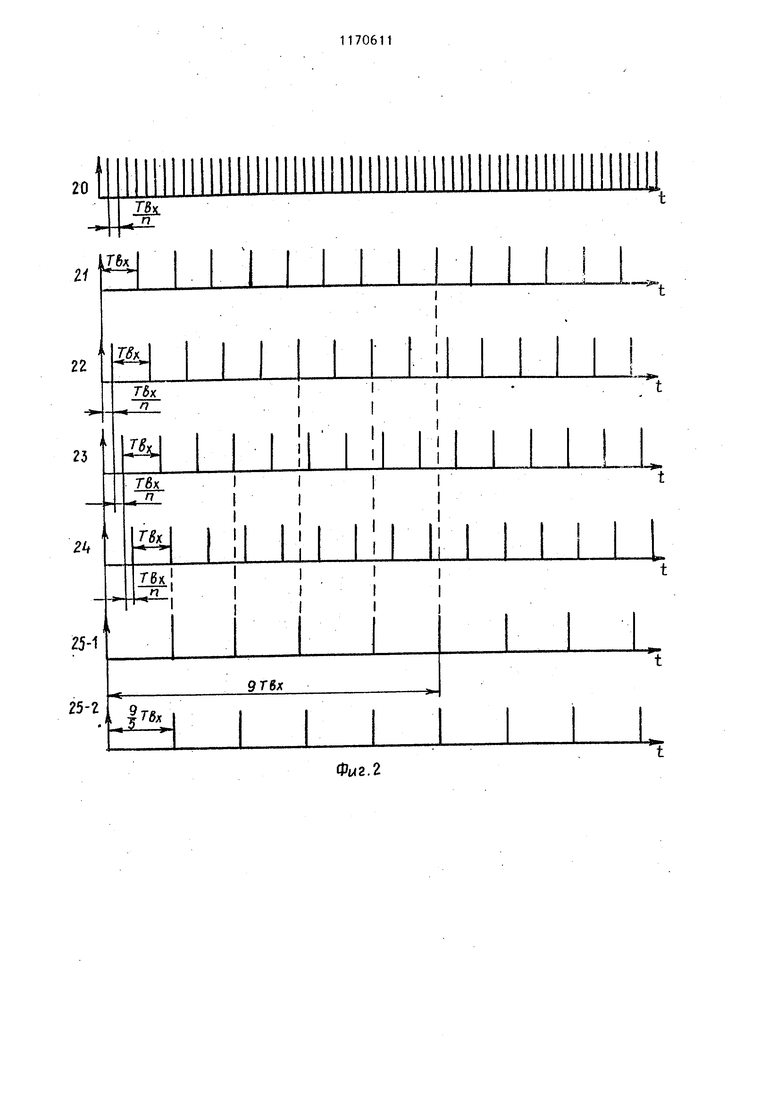

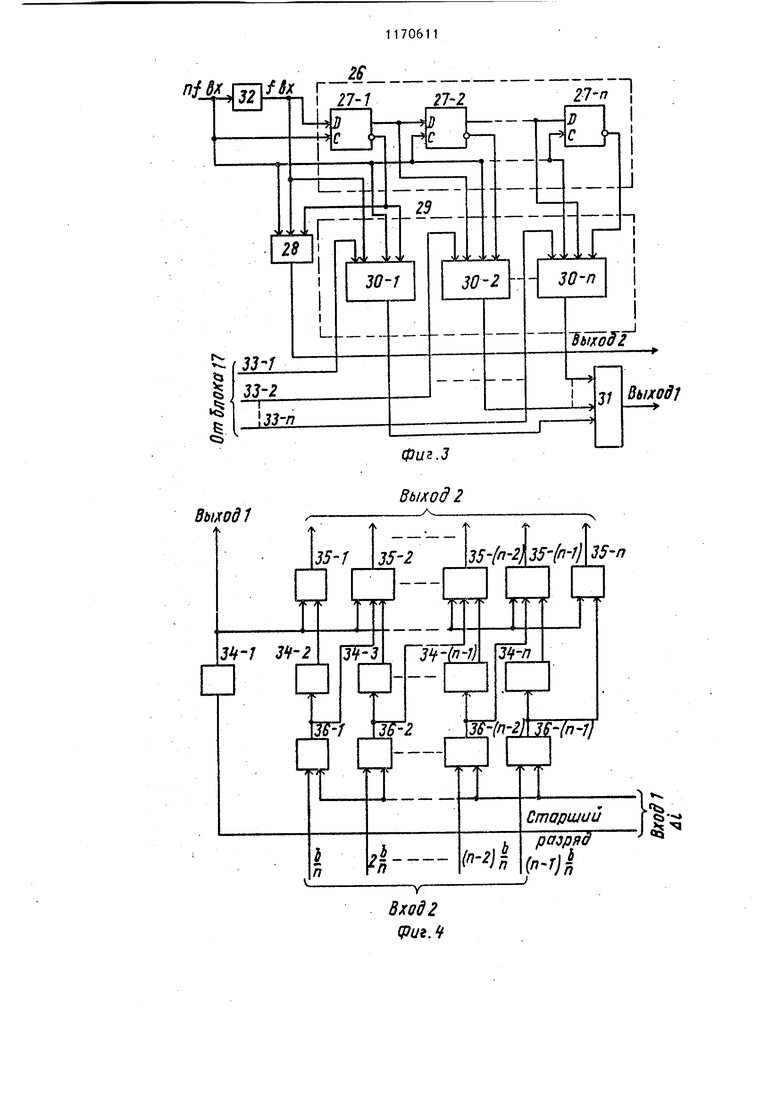

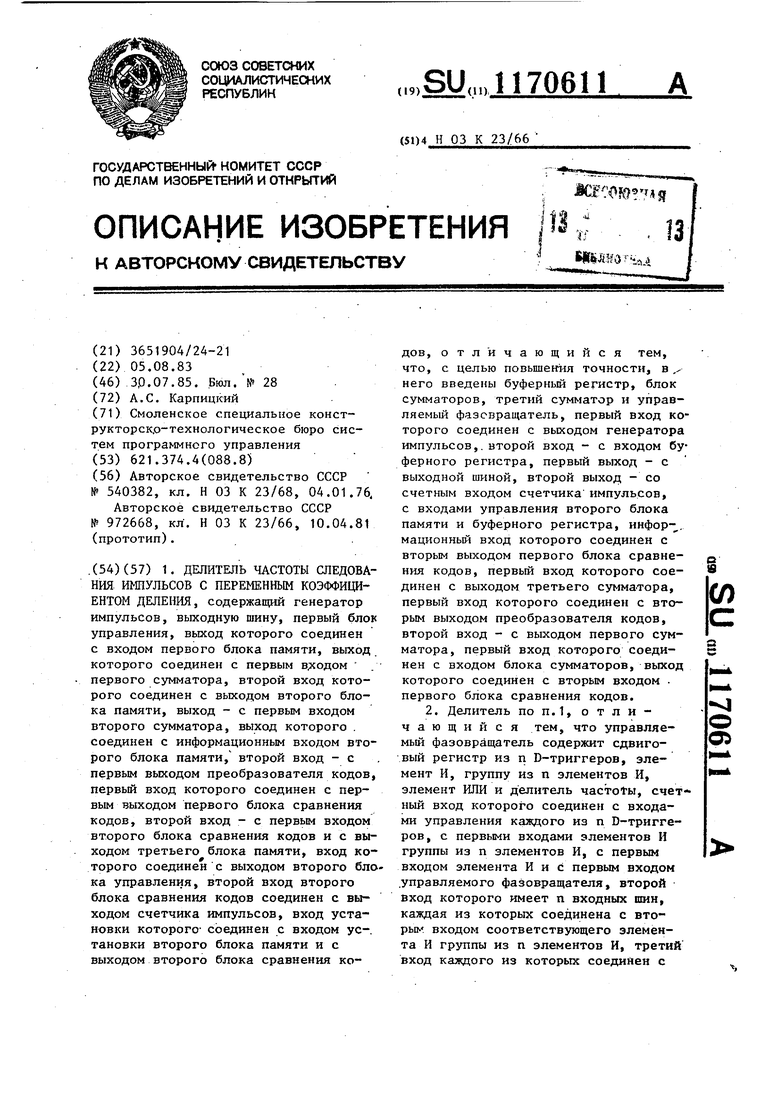

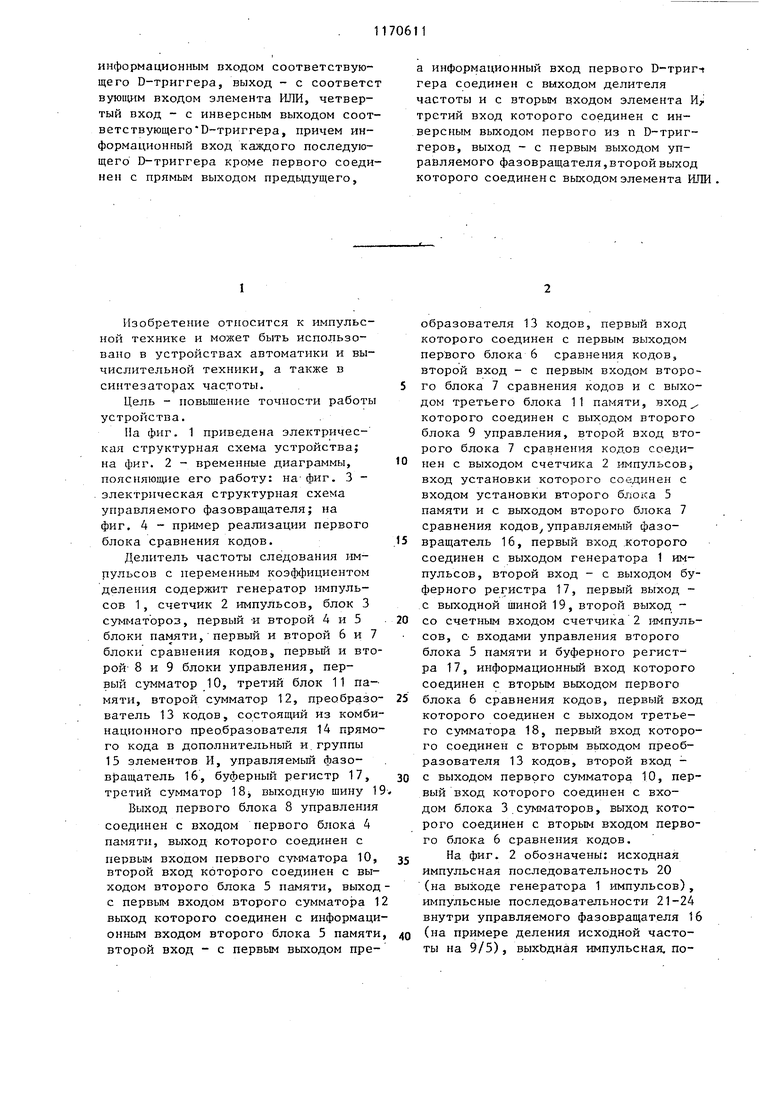

Па фиг. 1 приведена электрическая структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу: на-фиг. 3 электрическая структурная схема управляемого фазовращателя; на фиг. 4 - пример реализации первого блока сравнения кодов.

Делитель частоты следования импульсов с переменным )ициентом деления содержит генератор импульсов 1, счетчик 2 импульсов, блок 3 сумматороз, первый -и второй А и 5 блоки памяти,первый и второй 6 и 7 блоки сравнения кодов, первьш и второй 8 и 9 блоки управления, первый сумматор 10, третий блок 11 памяти, второй сумматор 12, преобразователь 13 кодов, состоящий из комбинационного преобразователя 14 прямого кода в дополнительный и.группы 15 элементов И, управляемый фазовращатель 16, буферный регистр 17, третий сумматор 18 выходную шину 19

Выход первого блока 8 управления соединен с входом первого блока 4 памяти, выход которого соединен с

первым входом первого сумматора 10, второй вход которого соединен с выходом второго блока 5 памяти, выход с первым входом второго сумматора 1 выход которого соединен с информационным входом второго блока 5 памяти второй вход - с первым выходом преобразователя 13 кодов, первый вход которого соединен с первым выходом первого блока 6 сравнения кодов, второй вход - с первым входом второго блока 7 сравнения кодов и с выходом третьего блока 11 памяти, вход которого соединен с выходом второго блока 9 управления, второй вход второго блока 7 сравнения кодов соединен с выходом счетчика 2 т мпульсов, вход установки которого соединен с входом установки второго блока 5 памяти и с выходом второго блока 7 сравнения кодов управляемый фазовращатель 16, первый вход которого соединен с выходом генератора 1 импульсов, второй вход - с выходом буферного регистра 17, первый выход с выходной шиной 19, второй выход со счетным входом счетчика 2 импульсов, о входами управления второго блока 5 памяти и буферного регистра 17, информационный вход которого соединен с вторым выходом первого блока 6 сравнения кодов, первый вход которого соединен с выходом третьего сумматора 18, первый вход которого соединен с вторым выходом преобразователя 13 кодов, второй вход с выходом первого сумматора 10, первый вход которого соединен с входом блока 3.сумматоров, выход которого соединен с вторым входом первого блока 6 сравнения кодов.

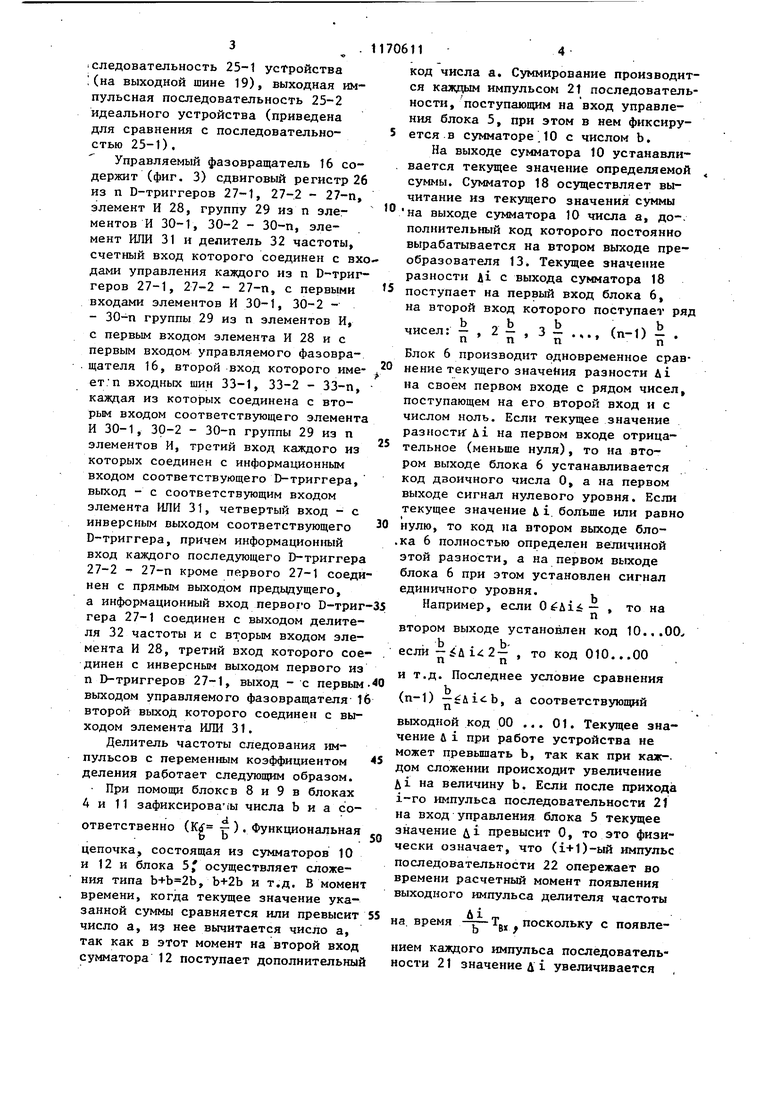

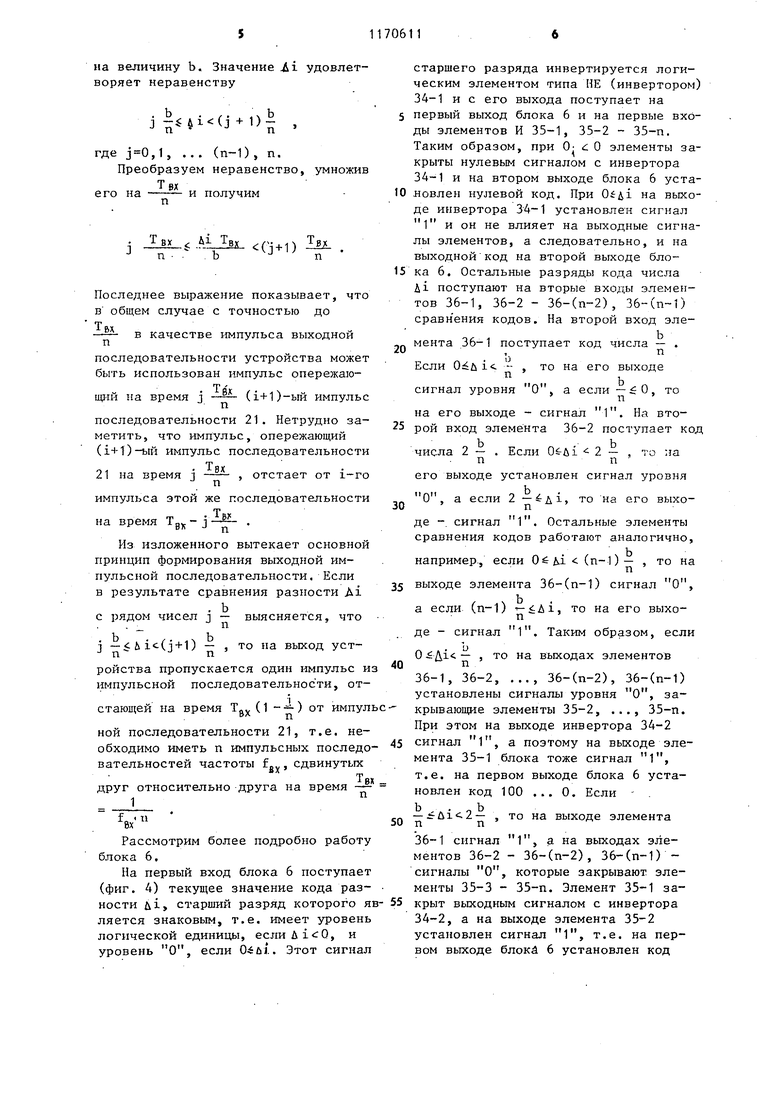

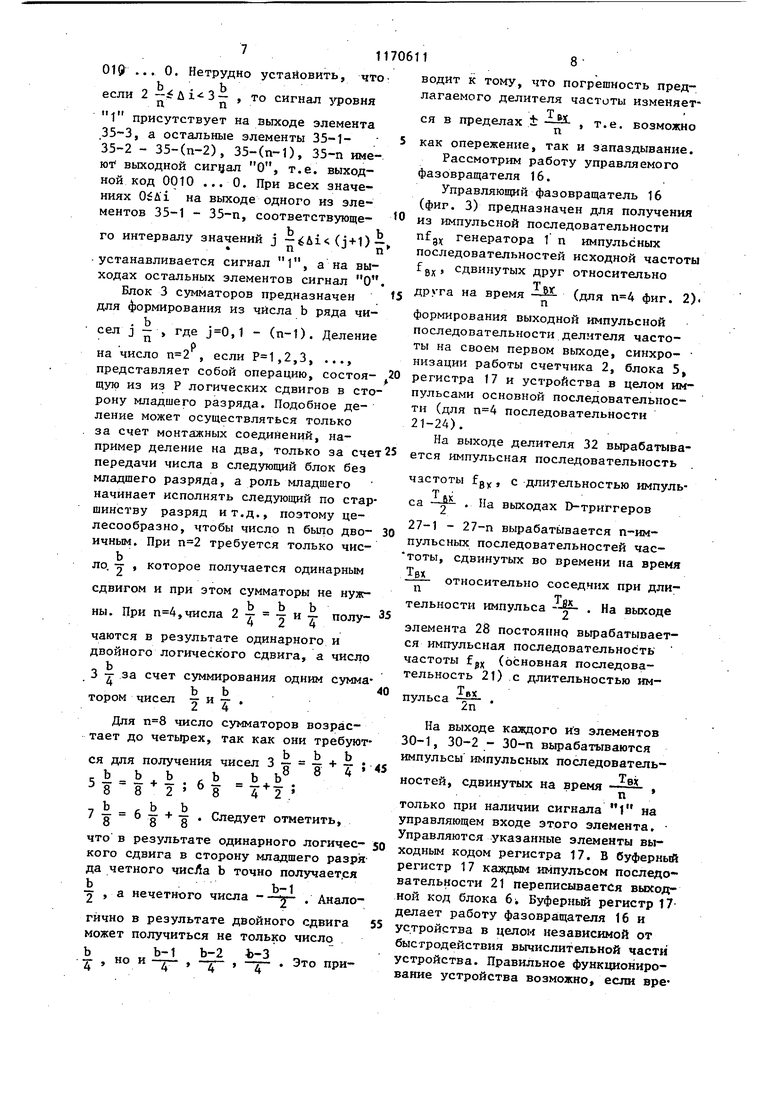

На фиг. 2 обозначены: исходная импульсная последовательность 20 (на выходе генератора 1 импульсов), импульсные последовательности 21-24 внутри управляемого фазовращателя 16 (на примере деления исходной частоты на 9/5), выхЬдная импульсная, по3 . 1 Следовательность 25-1 устройства (на выходной шине 19), выходная импульсная последовательность 25-2 идеального устройства (приведена для сравнения с последовательностью 25-1), Управляемый фазовращатель 16 содержит (фиг. 3) сдвиговый регистр 26 из п D-триггеров 27-1, 27-2 - 27-п, элемент И 28, группу 29 из п элементов И 30-1, 30-2 - 30-п, элемент ИЛИ 31 и делитель 32 частоты, счетный вход которого соединен с вхо дами управления каждого из п D-триггеров 27-1, 27-2 - 27-п, с первыми входами элементов И 30-1, 30-2 - 30-п группы 29 из п элементов И, с первым входом элемента И 28 и с первым входом управляемого фазовра. щателя 16, второй вход которого имеет; п входных шин 33-1, 33-2 - 33-п, каждая из которых соединена с вторым входом соответствующего элемента И 30-1, Зр-2 - 30-п группы 29 из п элементов И, третий вход каждого из которых соединен с информационным входом соответствующего D-триггера, выход - с соответствующим входом элемента ИЛИ 31, четвертый вход - с инверсным выходом соответствующего D-триггера, причем информационный вход каждого последующего D-триггера 27-2 - 27-п кроме первого 27-1 соеди нен с прямым выходом предццущего, а информационный вход первохо D-тpиг гера 27-1 соединен с выходом делителя 32 частоты и с вторым входом элемента И 28, третий вход которого сое динен с инверсным выходом первого из п ГЬтриггеров 27-1, выход - с первым выходом управляемого фазовращателя 1 второй выход которого соединен с выходом элемента ИЛИ 31. Делитель частоты следования импульсов с переменным коэффициентом деления работает следующим образом. При помощи блоков 8 и 9 в блоках А и 11 зафиксированы числа Ь и а соответственно (К ТГ Функциональная цепочка, состоящая из сумматоров 10 и 12 и блока 5 осуществляет сложения типа , b+2b и т.д. В момеи времени, когда текущее значение указанной суммы сравняется или превысит число а, из нее вычитается число а, так как в этот момент на второй вход сумматора 12 поступает дополнительны 11 код числа а. Суммирование производится каждым импульсом 21 последовательности, поступающим на вход управления блока 5, при этом в нем фиксируется в сумматоре 10 с числом Ь. На выходе сумматора 10 устанавливается текущее значение определяемой суммы. Сумматор 18 осуществляет вычитание из текущего значения суммы на выходе сумматора 10 числа а, до-, полнительный код которого постоянно вырабатывается на втором выходе преобразователя 13. Текущее значение разности Ai с выхода сумматора 18 поступает на первый вход блока 6, на второй вход которого поступает ряд (п-,) i Ь „ Ь . Ь чисел: - , Блок 6 производит одновременное сравнение текущего значения разности Ai на своем первом входе с рядом чисел, поступающем на его второй вход и с числом ноль. Если текущее значение разности Ai на первом входе отрицательное (меньше нуля), то на втором выходе блока 6 устанавливается код двоичного числа О, а на первом выходе сигнал нулевого уровня. Если текущее значение & i. больше или равно нулю, то код на втором выходе блока 6 полностью определен величиной этой разности, а на первом выходе блока 6 при этом установлен сигнал единичного уровня. , Например, если , то на выходе установлен код 10...00 втором . Ь . . Ь, то код 010...00 если -iu 14 2 - п п т.д. Последнее условие сравнения (п-1) - Д1сЬ, а соответствующий выходной код 00 ... 01. Текущее значение Л i при работе устройства не может превышать Ь, так как при каж-. дом сложении происходит увеличение А на величину Ъ. Если после прихода i-ro импульса последовательности 21 на вход управления блока 5 текущее значение дг превысит О, то это физически означает, что (1+1)-ый импульс последовательности 22 опережает во времени расчетный момент появления выходного импульса делителя частоты Tg поскольку с появлена, время нием каждого импульса последовательности 21 значениедi увеличивается на величину b. Значение i удовлетворяет неравенству j|.i(j + 1) , где ,1, ... (п-1), п. Преобразуем неравенство, умножив Тех и получим е го на j .Iii. (j+i) I . .l-s Ti Последнее выражение показывает, что в общем случае с точностью до Твх в качестве импульса выходной последовательности устройства может быть использован импульс опережающ1-п 1 на время j -- (1+1)-ый импульс последовательности 21. Нетрудно заметить, что импульс, опережающий (1+Т)-ый импульс последовательности Тях 21 на время j , отстает от 1-го импульса этой же последовательности на время . Из изложенного вытекает основной принцип формирования выходной импульсной последовательности. Если в результате сравнения разности Л b с рядом чисел j выясняется, что j - iii(j + 1) - , то на выход устройства пропускается один импульс и импульсной последовательности, отстающей на время Т-у (1 - -) от импул вх ц ной последовательности 21, т.е. необходимо иметь п импульсных последо вательностей частоты f , сдвинутых друг относительно друга на время - Рассмотрим более подробно работу блока 6. На первый вход блока 6 поступает (фиг. 4) текущее значение кода разности л1, старший разряд которого я ляется знаковым, т.е. имеет уровень логической единиць, еслиЛ1 ;0, и уровень О, если Oiul. Этот сигнал старшего разряда инвертируется логическим элементом типа НЕ (инвертором) 34-1 и с его выхода поступает на первый выход блока 6 и на первые входы элементов И 35-1, 35-2 - 35-п. Таким образом, при О- : О элементы закрыты нулевым сигналом с инвертора 34-1 и на втором выходе блока 6 усталозлен нулевой код. При на выходе инвертора 34-1 установлен сигнал 1 и он не влияет на выходные сигналы элементов, а следовательно, и на выходной код на второй выходе блока 6. Остальные разряды кода числа д1 поступают на вторые входы элементов 36-1, 36-2 - 36-(п-2), 36-(п-1) сравнения кодов. На второй вход элет, .b мента 36-1 поступает код числа - . Если Оби i. - п то на его выходе сигнал уровня О а если - 5 О. то п на его выходе - сигнал 1. На второй вход элемента 36-2 поступает код Если Otui - 2 числа 2 - п его выходе установлен сигнал уровня О, а если 2 - 6д1, то на его выходе -. сигнал 1. Остальные элементы сравнения кодов работают аналогично, например, если (п-1) - , то на выходе элемента 36-(п-1) сигнал О, а если (п-1) , то на его выходе - сигнал 1. Таким образом, если О - Д1 - , то на выходах элементов 36-1, 36-2, ..., 36-(п-2), 36-(п-1) установлены сигналы уровня О, закрывающие элементы 35-2, ..., 35-п. При этом на выходе инвертора 34-2 сигнал 1, а поэтому на выходе элемента 35-1 блока тоже сигнал 1, т.е. на первом выходе блока 6 установлен код 100 ... 0. Если . то на выходе элемента п п 36-1 сигнал 1, а на выходах элементов 36-2 - 36-(п-2), 36-(п-1) сигналы О, которые закрывают элементы 35-3 - 35-п. Элемент 35-1 закрыт выходным сигналом с инвертора 34-2, а на выходе элемента 35-2 установлен сигнал 1, т.е. на первом выходе блоки 6 установлен код 71 019 ... 0. Нетрудно установить, что если 2 , то сигнал уровня п п 1 присутствует на выходе элемента 35-3, а остальные элементы 35-135-2 - 35-(п-2), 35-(п-1), 35-п имеюг выходной сигцал О, т.е. выходной код 0010 ... 0. При всех значениях на выходе одного из элементов 35-1 - 35-п, соответствующего интервалу значений j (j + 1) - устанавливается сигнал 1, а на выходах остальных элементов сигнал О Блок 3 сумматоров предназначен для формирования из числа b ряда чи сел j - , где ,1 - (п-1). Деление Р на число , если ,2,3, ..., представляет собой операцию, состоящую из из Р логических сдвигов в сто рону младшего разряда. Подобное деление может осуществляться только . за счет монтажных соединений, например деление на два, только за сче передачи числа в следующий блок без младшего разряда, а роль младшего начинает исполнять следующий по стар шинству разряд и т.д., поэтому целесообразно, чтобы число п было двоичньм. При требуется только чискоторое получается одинарным сдвигом и при этом сумматоры не нужны. При ,числа 2 т- Т получаются в результате одинарного и двойного логического сдвига, а число 3 т за счет суммирования одним сумма b b тором чисел у и -т- . Для число сумматоров возрастает до четырех, так как они требуют ся для получения чисел 3 + у ,,, , ..,-Ь Ь b . 42, 7 Следует отметить. 8 88 что в результате одинарного логического сдвига в сторону младшего разря да четного чисЛа b точно получает.ся b Ь-1 J , а нечетного числаj- .Аналогично в результате двойного сдвига может получиться не только число b b-1 b-2 Ъ-3 Это при-г , но и -Т- -Г 1 водит к тому, что погрешность предлагаемого делителя частоты изменяется в пределах t - , т.е. возможно как опережение, так и запаздывание. Рассмотрим работу управляемого фазовращателя 16.. Управляющий фазовращатель 16 (фиг. 3) предназначен для получения из импульсной последовательности nfg генератора 1 п импульсных последовательностей исходной частоты fвх сдвинутых друг относительно друга на время - (для фиг. 2). формирования выходной импульсной последовательности делителя частоты на своем первом выходе, синхро- низации работы счетчика 2, блока 5, регистра 17 и устройства в целом импульсами основной последовательности (для последовательности 21-24).. На выходе делителя 32 вырабатывается импульсная последовательность частоты fgy, с длительностью импульПа выходах D-триГгеров са 27-1 - 27-п вырабатывается п-импульсных последовательностей частоты, сдвинутых во времени на время относительно соседних при длительности импульса - . На выходе элемента 28 постоянно вьфабатывается импульсная последовательность частоты f j (основная последовательность 21) с длительностью импульсаНа выходе каждого из элементов 30-1, 30-2 - 30-п вырабатываются импульсы импульсных последовательностей, сдвинутых на время - , только при наличии сигнала 1 на управляющем входе этого элемента. Управляются указанные элементы выходным кодом регистра 17. В буферный регистр 17 каждым импульсом последовательности 21 переписывается выходной код блока 6, Буферный регистр 17делает работу фазовращателя 16 и устройства в целом независимой от быстродействия вычислительной части устройства. Правильное функционирование устройства возможно, если вре9мя вычисления не превьшает Т, а запаздывание в работе цепочки из регистра 17 и фазовращателя 16 не Тех превышает --- так как фазовращатель 16 должет быть готов пропустит на выход устройства импульс, отстаю щии во времени на время от импульса последовательности 22, Быстр действие вычислительной части в основном определяется быстродействием трех последовательно соединенных су маторов 12, 10 и 18. Быстродействие такой цепочки обы но в 6-10 раз ншке, чем быстродейст вие цепочки, состоящей из регистра и элемента И, в пределах одной элементной базы. Из изложенного видно, что увеличение п (числа импульсных последовательностей) не приводит к ужесточению требований к быстродействию вычислительной части устройства, а только приводит к ужесточению требо ваний к быстродействию фазовращателя 1 6 и регистра 17, что осуществить значительно проще. Рассмотрим работу предлагаемого устройства для случая, когда коэффициент деления , число импульсных последовательностей (п) пе риода Tpj равно А. В исходном состоянии число 5 зафиксировано.в блоке 4, число 9 - в блоке 5. В регистре 17 зафиксирован код 0000, при котором запрещается прохождение импульсов на выход устройства с пер вого выхода управляемого фазовращателя 16. На его втором выходе постоянно вырабатываются импульсы последовательности 21. На выходе груп пы 15 элементов И преобразователя 1 установлен нулевой код. В счетчик 2 записан код числа 1. Б блоке 5 зафи сйрован код числа 5 поэтому на выходе сумматора 10 установлен код числа , так как на первьш вхо его поступает код числа 5с выхода блока 4. В свою очередь на выходе сумматора 18 установлен код числа , так как на первый вход сумматора 18 поступает дополнительный код числа с второго выхода преобразователя 13. На второй вход бло ка 6 поступает ряд чисел , , , SS 1 11 Ь-1 2 2; 3 3 с выхода блока 3, а на первый вход поступает число 1. В результате сравнения Ь-1 . Ь-1 -т-о 1 -X- на втором выходе блока 6 появится код 0100, а на первом выходе сигнал 1. Под действием этого сигнала открывается группа 15 элементов И преобразователя 13, в результате на второй вход сумматора 12 начинает поступать дополнительный код числа 9, на первый вход поступает прямой код числа 10 с выхода сумматора 10. На выходе сумматора 12 устанавливается код числа . Такое состояние блоков устройства будет до прихода первого имнульса пачки из девяти импульсов последовательности 2 1 . По приходу первого импульса последовательности 21 на входы управления блока 5 и регистра 17 в них зафиксируются код числа 1 и код 0100 соответственно. Код числа 1, поступая на вход сумматора 10, суммируется кодом числа пять, поступающим на другой вход сум1 1атора 10 с выхода блока 11. На выходе су1«1матора устанавливается код числа , а на выходе сумматора 18 - код числа . ,, Так как -ЗлО, то на втором выходе блока 6 вырабатывается код 0000, а на первом выходе - сигнал нулевого уровня, закрывающий группу 15 и устанавливающий на ее выходе нулевой код. В результате на выходе сумматора 12 устанавливается код числа 6 (как и на выходе сумматора 10). В счетчике 2 фиксируется код числа 2. Код 0100, поступа:ощий на вход управления фазовращателя 16, предписывает ему пропустить- на выход устройства импульсную последовательность 24. За время между первым и вторым импульсами последовательности .21 на выход устройства пропускается один импульс последовательности 24 (фиг. 2, импульсн-ую последовательность 25) . По приходу второго импульса последовательности 21 на входы управления б.лока 5 и .регистра 17 в них зафиксируются код числа 6 и код 0000 соответственно. Код числа 6, поступая на вход сумматора 10, суммируется с кодом числа 5 и на выходе сумматора 10 устанавливается код числа 11. В результате, на выходе сумматора 18 устанавливаетПся код числа . Блок 6 производит сравнение -т- 2 s 2 -т- 3 и вырабатывает на своем втором выходе соответствующий код 0010, а на первом выходе - сигнал 1. Под действием этого сигнала открывается груп па- 15 элементов И, следовательно, на второй вход сумматора 12 поступа ет дополнительный код числа 9, на первый вход - прямой код числа 11 и на выходе устанавливается код чис ла . Так как в регистре 17 . зафиксирован код 0000, то на время между окончанием второго импульса и окончанием третьего импульса последовательности 21 фазовращатель за крыт для прохождения импульсов на выход устройства. В счетчике 2 фиксируется код числа 3. По приходу третьего импульса последовательност 21 на входы управления блока 5 и ре гистра 17 в них фиксируется код чис ла 2 и код 0010 соответственно. Код числа 2, суммируясь в сумматоре 10 с кодом числа 5, устанавливает на его выходе код числа , а на выходе сумматора 18 - код.числ . Так как , то на. втором выходе блока 6 устанавливается код 0000, а на первом выходе - сигнал нулевого уровня, вновь устанавливаю щий на выходе группы 15 нулевой код На выходе сумматора 12 поэтому уста навливается код числа 7 (как и на выходе сумматора 10). В счетчике 2 фиксируется код числа четыре. Код 0010, поступающий на вход управления фазовращателя 16, предписывает ему пропускать на выход устройства импульсную последовательность 23. За время между третьим и четвертым импульсами последовательности 21 на выход устройства пропускается один импульс последовательности 23. По приходу четвертого импульса последовательности 21 в блоке 5 и регистре 17 фиксируется код числа 7 и код 0000 соответственно. Код числа 7, суммируясь в сумматоре 10 с кодом числа 5, устанавливает на его выходе код числа , а на выходе сумматора.18 - код числа . Блок 6 сравнивает коды и вырабатывает на своем втором выходе соответствующий код 0001, на первом 1. Под выходе - сигнал уровня 11 действием этого сигнала открывается группа 15 и на выходе сумматора 12 устанавливается код числа . Код 0000 на выходе регистра 17 запрещает прохождение импульсов на выход устройства. В счетчике 2 устанавливается код числа 5. По приходу пятого импульса последовательности 21 в блоке 5 и регистре 17 фиксируется код числа 3 и код 0001 соответственно. Код числа 3, суммируясь в сумматоре 10 с кодом числа 5, устанавливает на его выходе код числа . , а на выходе сумматора - 18 код числа . Так как , то на. втором выходе блока 6 устанавливается код 0000, а на первом выходе - сигнал нулевого уровня, устанавливающий на выходе группы 15 нулевой код. На выходе сумматора 12 устанавливается код числа 8. Код 0001 на выходе регистра 17 предписывает фазовращателю 16 пропустить на его выход импульсную последовательность 22. За время между пятым и шестым импульсам последовательности 2 1 на выход устройства пропускается один импульс последовательности 22. В счетчике 2-фиксируется код числа 6. По приходу шестого импульСа последовательности 21 в блоке 5 и регистре 17 фиксируется код числа 8 и код 0000 соответственно. Код числа 8, суммируясь в сумматоре 10 с кодом, числа 5, устанавливает на его выходе код числа , а на выходе сумматора 18 - код числа . Блок 6 сравнивает коды -д-. 3 4 и вырабатывает на своем втором выходе соответствующий код 0001, а на первом вькоде - сигнал уровня 1.Под действием этого сигнала открьгоается группа 15 и на выходе сумматора 12 устанавливается код числа . Код 0000 на выходе регистра 17 запрещает прохождение импульсов на выход устройства до момента окончания седьмого импульса последовательности 21. В счетчике 2 фиксируется код числа 7. По приходу.седьмого импульса последовательности 21 в блоке 5 и регистре 17 фиксируются код числа 4 и код 0001 соответственно. Код числа 4, суммируясь в сумматоре 10 с кодом числа 5, устанавливает и на его выходе код числа а на выходе сумматора 18 - код числа

9-9 0. Блок 6 сравнивает коды и вырабатывает на своем вто

ром ыыходе соответствуюпрй код 1000, а на первом выходе - сигнал уровня 1 . Под действием этого сигнала открывается группа 15 и на выходах сумматора 12 устанавливается код числа 9-9.0./Код 0001 на выходе регистра 17 предписывает фазовращателю 16 пропустить на его выход импульсную последовательность 22. За время между седьмым и восьмым импульсами последовательности 21 на выход проходит один импульс последовательности 22. В счетчике 2 фиксируется код числа восемь.

По приходу восьмого импульса последовательности 21 в блоке 5 и регистре 17 фиксируется код числа О и код 1000 соответственно. Код числа О суммируясь в сумматоре 10 с кодом числа 5, устанавливает на его выходе код числа , а на выходе сумматора 18 - код -числа . Так как , то ja втором выходе блока 6 устанавливается код 0000, а на первом выходе - сигнал нулевого уровня, устанавливающий на выходе группы 15 нулевой код. На выходе сумматора 12 устанавливается код числа 5.

В счетчике 2 фиксируется код числа девять. В этот момент срабатывает блок 7, так как на оба его входа поступают коды числа девять. Импульсом с выхода блока 7 обнуляются счетчИк 2 и блок 5. Нетрудно заметить, что при правильной работе устройства в блоке 5 в момент его обнуления по входу R (установочному) и так залисан код числа 0. Но при работе возможны сбои, например при включени питания, из-за помех по питанию. Наличие счетчика 2 и блока 7 повышают надежность работы устройства в целом, синхронизируя его работу. Код 1000 на выходе регистра 17 предписывает фазовращателю 16 пропустить на его выход импульсную последовательность 21, поэтому девятый импульс этой последовательности проходит на выход устройства.

Этим девятым импульсом в блоке 5 фиксируется код числа 5, в реЛ1Стре 17 - код 0000. В .счетчике 2 фиксируется код числа один, т,.е. устройство возвращается в исходное состояние, повторяющееся через каждые 9 импульсов последовательности 21 ,при . коэффициенте деления .

Нетрудно заметить (фиг. 2 диаграм,мы последовательности 25-1 и 25--;, что наибольшая погрешность получается в тот момент, когда вырабатывается третий импульс ца выходе устройства, У идеального делителя он появляется через время 5,4 Tj,j, , а у предлагаемого через 5,25 Т. , Погрешность равна t- 0,15 Т, , т.е. максимальная погрешность не превьш1ает

0,25 Tg , при .

Таким образом, получено увеличение точности примерно в четыре раза по сравнению спрототипом (в общем случае в п раз) . Причем скот ncv-, работы вычислительной части ограничивается временем Тр, - периодом последовательности 21, у. эта скорость практически не зависит от

числа п.

-вх

Время - является ограничивающим

для скорости работы фазовращателя

16 и регистра 17, по существу оно регламентирует время срабатывание цепочки, состоящей из параллельного регистра, элемента И и элемента ИЛИ. Такую цепочку последовательно соединенных элементов можно сделать-весьма быстродействующей по сравнению с вычислительной частью и поэтому существует возможность повышать точность устройства за счет увеличения

числа п. Увеличивая число импульсных последовательностей п можно получить точность во много раз превышающую точность устройства, принятого за прототип, так как у предлагаемого устройства погрешность

, а у прототипа ..

равна

п

Фмг.2

| Устройство с регулируемым дробным коэффициентом деления последовательности импульсов | 1976 |

|

SU540382A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| . | |||

Авторы

Даты

1985-07-30—Публикация

1983-08-05—Подача