1

Изобретение относится к вычислительной технике и может быть использовано для хранения дискретной информации в цифровой форме.

Целью изобретения является повышение надежности устройства.

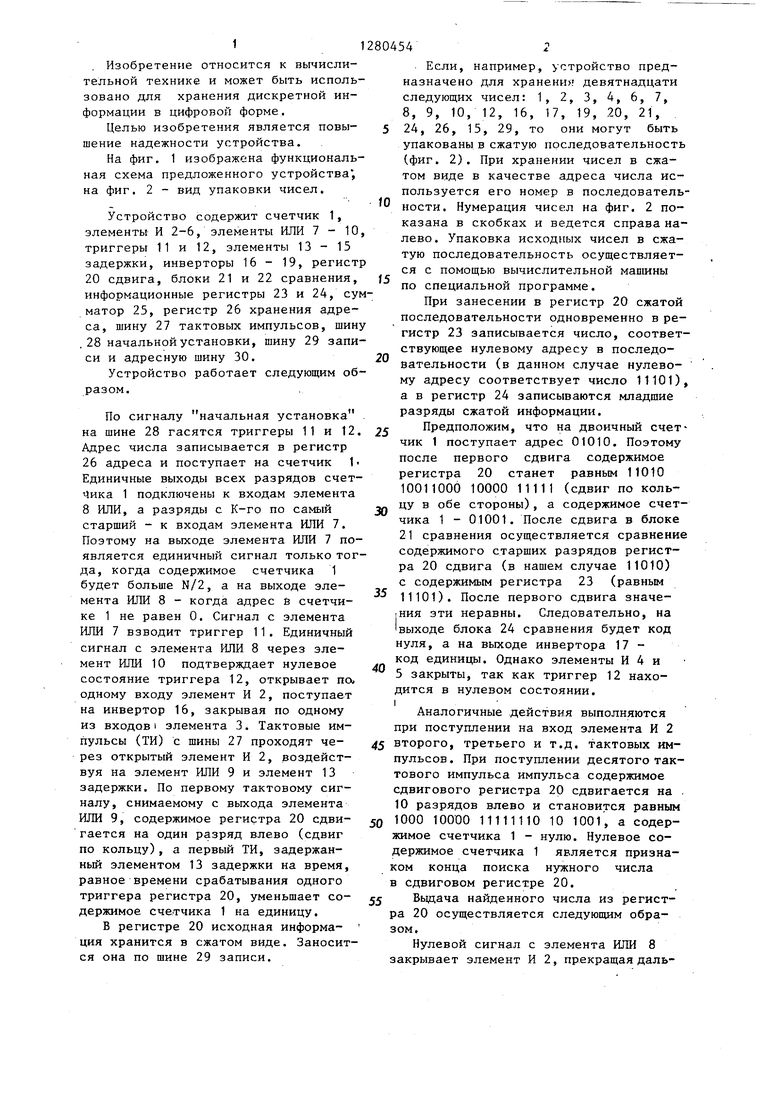

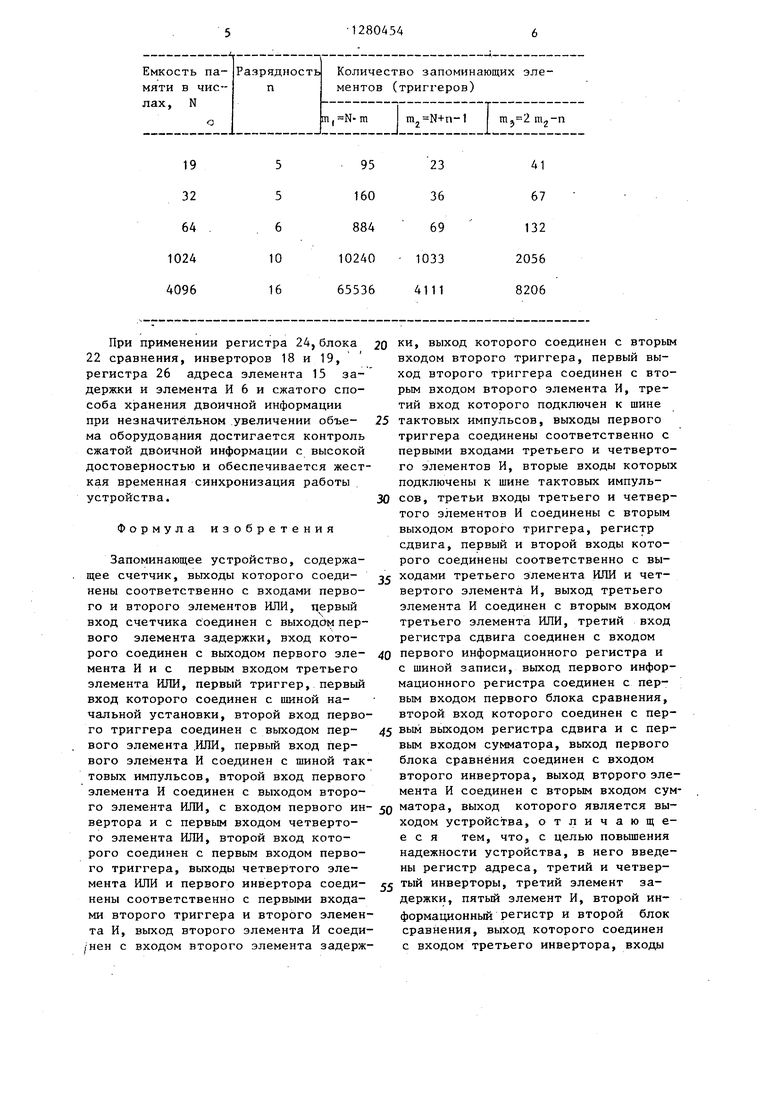

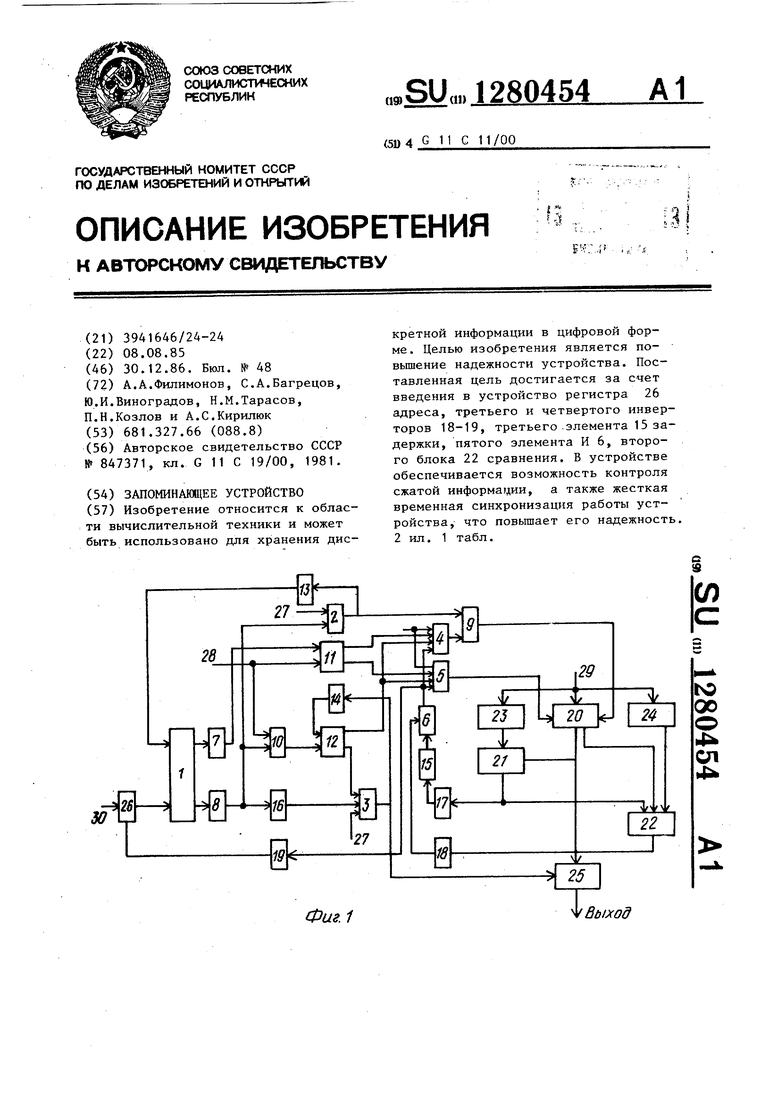

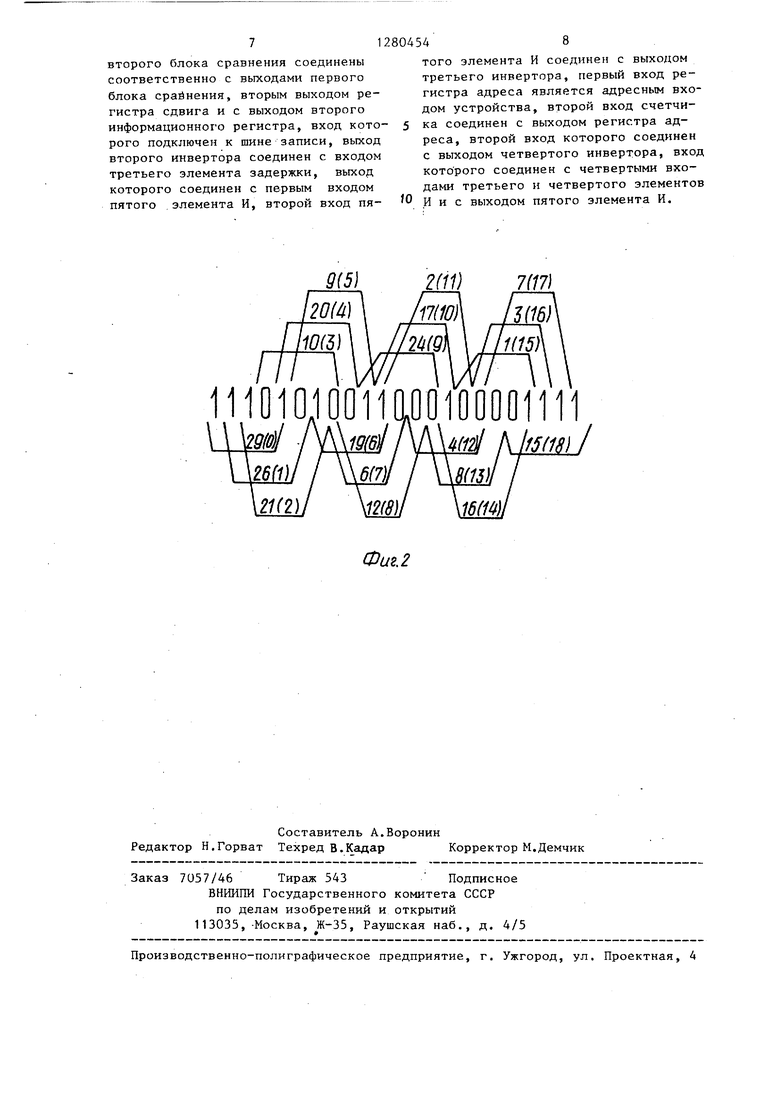

На фиг, 1 изображена функциональная схема предложенного устройства , на фиг. 2 - вид упаковки чисел.

Устройство содержит счетчик 1, элементы И 2-6, элементы ИЛИ 7 - 10 триггеры 11 и 12, элементы 13 - 15 задержки, инверторы 16 - 19, регистр 20 сдвига, блоки 21 и 22 сравнения, информационные регистры 23 и 24, сумматор 25, регистр 26 хранения адреса, шину 27 тактовых импульсов, шину , 28 начальной установки, шину 29 записи и адресную шину 30.

Устройство работает следующим образом.

По сигналу начальная установка на шине 28 гасятся триггеры 11 и 12. Адрес числа записывается в регистр 26 адреса и поступает на счетчик 1 Единичные выходы всех разрядов счет- Чика 1 подключены к входам элемента 8 ИЛИ, а разряды с К-го по самый старший - к входам элемента ИЛИ 7. Поэтому на выходе элемента ИЛИ 7 появляется единичный сигнал только тогда, когда содержимое счетчика 1 будет больше N/2, а на выходе элемента ИЛИ 8 - когда адрес и счетчике 1 не равен 0. Сигнал с элемента ИЛИ 7 взводит триггер 11. Единичный сигнал с элемента ИЛИ 8 через элемент ИЛИ 10 подтверждает нулевое состояние триггера 12, открывает по, одному входу элемент И 2, поступает на инвертор 16, закрывая по одному из входов i элемента 3. Тактовые импульсы (ТИ) с шины 27 проходят через открытый элемент И 2, воздействуя на элемент ИЛИ 9 и элемент 13 задержки. По первому тактовому сигналу, снимаемому с выхода элемента ИЛИ 9, содержимое регистра 20 сдвигается на один разряд влево (сдвиг по кольцу), а первый ТИ, задержанный элементом 13 задержки на время, равное времени срабатывания одного триггера регистра 20, уменьшает содержимое счетчика 1 на единицу.

В регистре 20 исходная информа- ция хранится в сжатом виде. Заносится она по шине 29 записи.

fO

f5

0

5

0

5

0

5

0

5

Если, например, устройство предназначено для хранения девятнадцати следующих чисел: 1, 2, 3, 4, 6, 7, 8, 9, 10, 12, 16, 17, 19, 20, 21, 24, 26, 15, 29, то они могут быть упакованы в сжатую последовательность (фиг. 2). При хранении чисел в сжатом виде в качестве адреса числа используется его номер в последовательности. Нумерация чисел на фиг. 2 показана в скобках и ведется справа налево. Упаковка исходных чисел в сжатую последовательность осуществляется с помощью вычислительной машины по специальной программе.

При занесении в регистр 20 сжатой последовательности одновременно в регистр 23 записывается число, соответствующее нулевому адресу в последовательности (в данном случае нулевому адресу соответствует число 11101), а в регистр 24 записываются младшие разряды сжатой информации.

Предположим, что на двоичный счет- чик 1 поступает адрес 01010. Поэтому после первого сдвига содержимое регистра 20 станет равньм 11010 10011000 10000 11111 (сдвиг по кольцу в обе стороны), а содержимое счетчика 1 - 01001. После сдвига в блоке 21 сравнения осуществляется сравнение содержимого старших разрядов регистра 20 сдвига (в нашем случае 11010) с содержимым регистра 23 (равным 11101). После первого сдвига значения эти неравны. Следовательно, на выходе блока 24 сравнения будет код нуля, а на выходе инвертора 17 - код единицы. Однако элементы И 4 и 5 закрыты, так как триггер 12 находится в нулевом состоянии. I

Аналогичные действия выполняются

при поступлении на вход элемента И 2 второго, третьего и т.д. тактовых импульсов. При поступлении десятого тактового импульса импульса содержимое сдвигового регистра 20 сдвигается на . 10 разрядов влево и становится равным 1000 10000 11111110 10 1001, а содержимое счетчика 1 - нулю. Нулевое содержимое счетчика 1 является признаком конца поиска нужного числа в сдвиговом регистре 20.

Вьщача найденного числа из регистра 20 осуществляется следующим образом.

Нулевой сигнал с элемента ИЛИ 8 закрывает элемент И 2, прекращая дальнейшин сдвиг сжатой последовательности в регистре 20, и приводит к образованию единичного сигнала на выходе

инвертора 16. Так как триггер 12 погашен, то по одиннадцатому тактовому сигналу на выходе элемента И 2 образуется единичный сигнал, по которому осуществляется выдача найденного числа 10001 из пяти старших разрядов сдвигового регистра 20 через сумматор 25. Этот же сигнал с элемента И 8 через элемент 14 задержки устанавливает триггер 12 в единичное состояние. Этим самым дается разрешение сжатой последовательности в сдвиговом регистре 20 в исходное (началь- ное) состояние. Для этой цели служат элементы И 4 и 5 и инвертор 18, блок 21 сравнения и триггер 11. Триггер 11 указывает направление сдвига сжатой последовательности для возвращения ее в исходное состояние кратчайшим путем. В частности, если триггер 11 установлен в единичное сфстояние, то ТИ поступают на регистр 20, через открытый элемент И 4, элемент ИЛИ 9 и сдвиг осуществляется справа налево по кольцу если триггер 11 пога

рез элемент И 5 и сдвиг выполняется слева направо тоже по кольцу. В обоих случаях сдвиг продолжается до тех пор, пока в старших разрядах регистра 20 не окажется число с нулевым адресом (таким числом является 11101). Так.как такое же число хранится в регистре 23, то на выходе блока 21 сравнения появляется единичный сигнал, а на выходе инвертора 17 - соответственно код нуля.

Совпадение старших разрядов информации, поступающих с первого выхода регистра 20, свидетельствует о том, что сжатая двоичная информация возвращена в начальное состояние. Кроме того, можно утверждать, что п старших разрядов регистра 20 переписаны правильно. Проверка остальных разрядов (младших) регистра 20 на совпа- .дение осуществляется с помощью регистра 24 и блока 22 сравнения. Еди- яичный сигнал с выхода блока 21 сравнения разрешает работу блока 22 сравнения и, если младшие разряды,снимаемые со второго выхода регистра 20 совпадают, то на выходе блока 22 по

/0

2804544

является единичный сигнал, который через инвертор 18 поступает на элемент И 6, на второй вход которого через элемент 15 задержки поступает код нуля с выхода инвертора 17.,При совпадении кодов нуля, поступаюшд х с инверторов 17 и 18, с выхода элемента 6 выдается сигнал, который запрещает работу элементов И 4 и 5. Тем самым прекращается сдвиг информации в регистре 20 и осуществляется контроль правильности перезаписи всех разрядов сжатой двоичной информации.

Одновременно запрещающий сигнал с выхода элемента 6 инвертируется инвертором 19 и производит считывание нового кода адреса, поступившего в регистр 20.

Таким образом, наличие регистра 20 обеспечивает временную синхронизацию работы устройства с работой

15

20

25

30

0

35

5

5

систем, обеспечивающих выработку адреса числа. Кроме того, такое построение устройства запрещает обращение к блоку памяти при наличии случайных ошибок в записи информации. На этом заканчивается цикл обращения к запоминающему устройству.

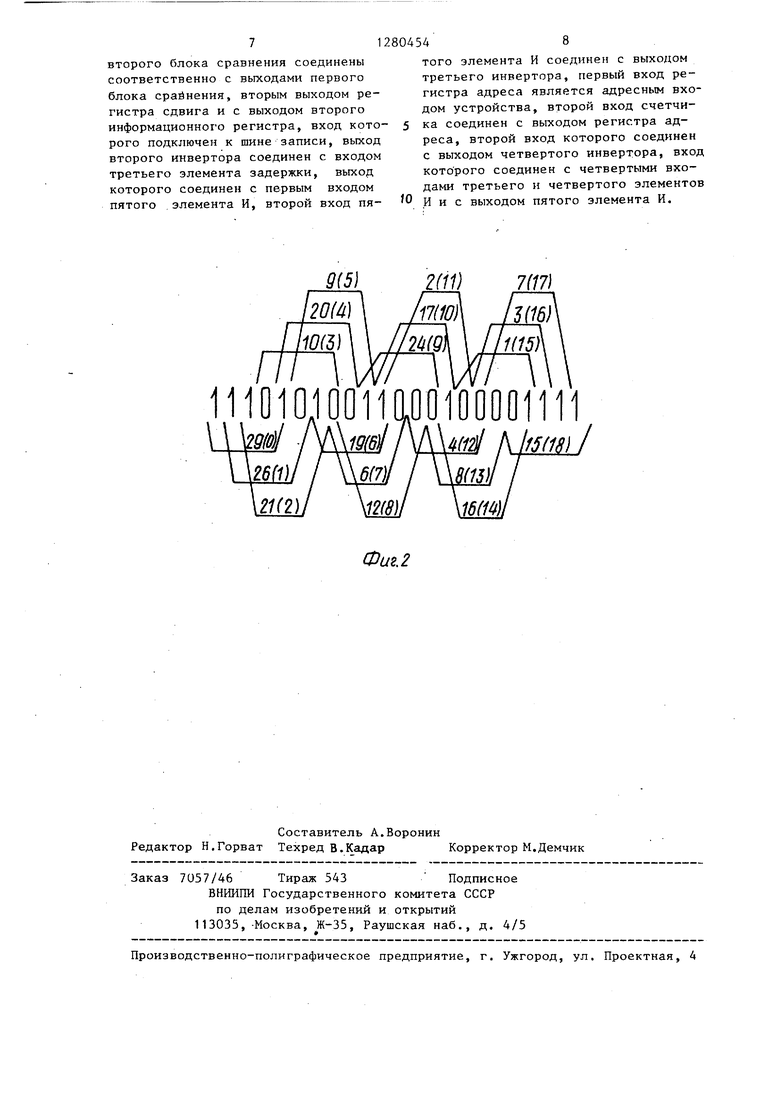

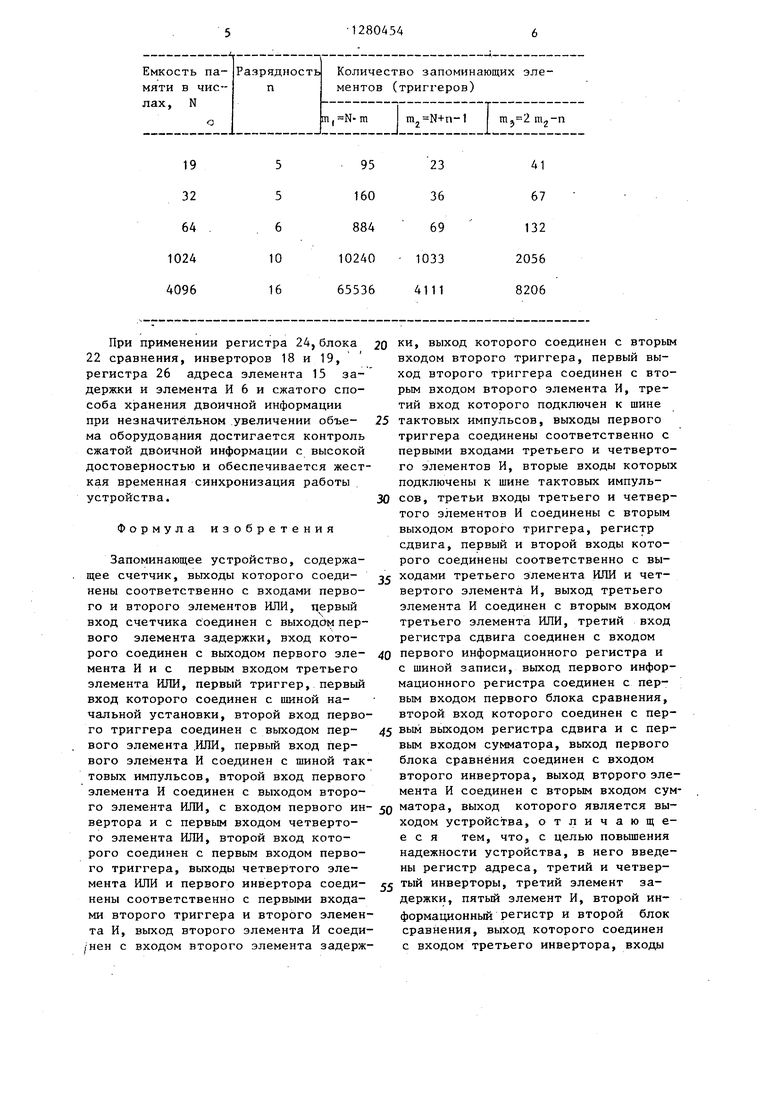

Из фиг. 2 в1щно, что для хранения девятнадцати пятиразрядных чисел необходимо иметь 23 запоминающих элемента. Количество запоминаюш 1х элементов определяется выражением

т N + п - 1 ,

где N - количество хранимых слов (числа) в запоминающем устройстве, п - разрядность хранимых чисел. С учетом контроля информации количество запоминающих элементов увеличивается незначительно по сравнению с обычным способом хранения чисел. Общее число элементов (триггеров) составит

m 1 2 m - п

Если хранить эти же числа обычным способом и не производить контроль информации на регистре 20 сдвига, то .потребуется запоминающих элементов

т, N-n,

т.е. для нашего примера 95 триггеров.

Сравнительные данные необходимого количества запоминающих элементов приведены в таблице.

При применении регистра 24,блока 22 сравнения, инверторов 18 и 19, регистра 26 адреса элемента 15 задержки и элемента И 6 и сжатого способа хранения двоичной информации при незначительном увеличении объема оборудования достигается контроль сжатой двоичной информации с высокой достоверностью и обеспечивается жесткая временная синхронизация работы устройства.

Формула изобретения

Запоминающее устройство, содержащее счетчик, выходы которого соединены соответственно с входами первого и второго элементов ИЛИ, первый вход счетчика соединен с выходд1 1 первого элемента задержки, вход которого соединен с выходом первого элемента И и с первым входом третьего элемента ШТИ, первый триггер, первый вход которого соединен с шиной начальной установки, второй вход первого триггера соединен с выходом первого элемента .ИЛИ, первый вход первого элемента И соединен с шиной тактовых импульсов, второй вход первого элемента И соединен с выходом второго элемента ИЛИ, с входом первого инвертора и с первым входом четвертого элемента ИЖ, второй вход которого соединен с первым входом первого триггера, выходы четвертого элемента ИЛИ и первого инвертора соединены соответственно с первыми входами второго триггера и второго элемента И, выход второго элемента И соеди- /нен с входом второго элемента задержки, выход которого соединен с вторым входом второго триггера, первый выход второго триггера соединен с вторым входом второго элемента И, третий вход которого подключен к шине

тактовых импульсов, выходы первого триггера соединены соответственно с первыми входами третьего и четвертого элементов И, вторые входы которых подключены к шине тактовых импульсов, третьи входы третьего и четвертого элементов И соединены с вторым выходом второго триггера, регистр сдвига, первый и второй входы которого соединены соответственно с выходами третьего элемента ИЖ и четвертого элемента И, выход третьего элемента И соединен с вторым входом третьего элемента ИЛИ, третий вход регистра сдвига соединен с входом

первого информационного регистра и с шиной записи, выход первого информационного регистра соединен с пер- Bbw входом первого блока сравнения, второй вход которого соединен с первым выходом регистра сдвига и с первым входом сумматора, выход первого блока сравнения соединен с входом второго инвертора, выход второго элемента И соединен с вторым входом сумматора, выход которого является выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены регистр адреса, третий и четвертый инверторы, третий элемент задержки, пятый злемент И, второй информационный регистр и второй блок сравнения, выход которого соединен с входом третьего инвертора, входы

71

второго блока сравнения соединены соответственно с выходами первого блока срайнения, вторым выходом регистра сдвига и с выходом второго информационного регистра, вход кото рого подключен к шине записи, выход второго инвертора соединен с входом третьего элемента задержки, выход которого соединен с первым входом пятого элемента И, второй вход пя804548

того элемента И соединен с выходом третьего инвертора, первый вход регистра адреса является адресным входом устройства, второй вход счетчи5 ка соединен с выходом регистра адреса, второй вход которого соединен с выходом четвертого инвертора, вход кото рого соединен с четвертыми входами третьего и четвертого элементов О И и с выходом пятого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Долговременное запоминающее устройство | 1979 |

|

SU847371A1 |

| Запоминающее устройство | 1989 |

|

SU1674255A2 |

| Запоминающее устройство | 1979 |

|

SU842967A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Многофункциональный анализатор случайных процессов | 1986 |

|

SU1399766A1 |

| ОБНАРУЖИТЕЛЬ ПАУЗ РЕЧИ В СИСТЕМЕ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2103826C1 |

| Медианный рекурсивный фильтр | 1988 |

|

SU1654837A1 |

| Генератор случайных последовательностей | 1983 |

|

SU1180887A1 |

| Устройство определения локальных экстремумов функции | 1984 |

|

SU1241227A1 |

| Устройство для определения локальных экстремумов функции | 1985 |

|

SU1290297A1 |

Изобретение относится к области вычислительной техники и может быть использовано для хранения дискретной информации в цифровой форме. Целью изобретения является повышение надежности устройства. Поставленная цель достигается за счет введения в устройство регистра 26 адреса, третьего и четвертого инверторов 18-19, третьего элемента 15 задержки, пятого элемента И 6, второго блока 22 сравнения. В устройстве обеспечивается возможность контроля сжатой информации, а также жесткая временная синхронизация работы устройства, что повьппает его надежность. 2 ил. 1 табл. (Л 21 Фиг.1 Т Выход

7(17}

01111

tsmJ

Фиг. 2

| Долговременное запоминающее устройство | 1979 |

|

SU847371A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-30—Публикация

1985-08-08—Подача