Изобретение относится к вычисли тельной технике и быть исполь зовано при построении быстродействующих операционных устройств цифровых вычислительных машин.

Цель изобретения - повышение быстродействия за счет сокращения времени вычисления элементарных функций.

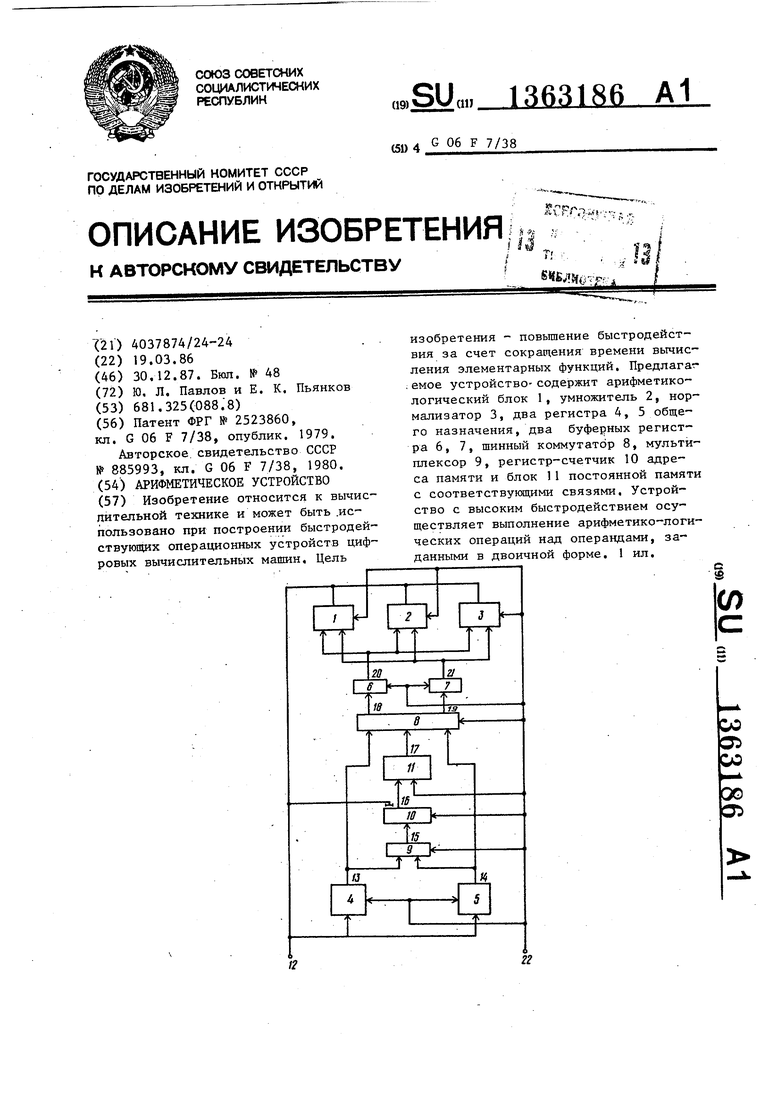

На чертеже представлена функциональная схема арифметического устрой ства,

Устройство, содержит арифметико- логический блок 1, умножитель 2, нормализатор 3, первый и второй регистры 4 и 5 общего назначения, первый и второй буферные регистры б и 7, шинный коммутатор 8, мультиплексор 9, регистр-счетчик 10 адреса памяти, блок II постоянной памяти, информационную шину 12, соединенную соответственно с выхо- дами арифметико-логического блока I умножителя 2, нормализатора 3, информационными входами регистров 4 и 5 общего назначения и с -управляющим выходом регистра-счетчика 10 адреса памяти, выход 13 регистра 4 обш,вго назначения соединен с первыми информационными входами мультиплексора 9 и шинного коммутатора 8, выход 14 регистра 5 общего назначения соединен со вторыми информаци- онными входами шинного коммутатора 8 и мультиплексора 9, выход 15 которого соединен с информационным входом регистра-счетчика 10 адреса памяти, адресный выход 16 котор ого соединен с адресным входом блока 11 постоянной памяти, информационный вы ход 17 которого соединен с третьим информационным входом шинного коммутатора 8, первый выход 18 которого соединенс информационным входо 1 .первого буферного регистра 6-, второй выход 19 шинного коммутатора В соединен с информационным входом второго буферного регистра 7, выход 20 первого буферного регистра 6 соединен с первыми информационными входами арифметико-логического блока 1, умножителя 2 и нормализатора 3, вторые информационные входы которых соединены с выходом 21 второго буферного регистра 7, входы разреше- -ния записи регистров 4 и 5 общего назначения, буферных регистров 6 и 7: синхровкоды арифметико-логического

631862

блока 1, умножителя 2, нормализатора 3, регистра-счетчика 10 адреса памяти, блока 1 постоянной памя- р. ти и управляющие входы шинного коммутатора 8 и мультиплексора 9 соединены соответственно с управляющей шиной 22 устройства.

Устройство работает следующим

10 образом,

Выполнение операции сложения, Эта операция выполняется арифметико- логическим блоком 1, Операция начинается с зациси исходных операндов

If в буферные регистры 6 и 7. В регистры 6 и 7 операнды могут быть записаны через шинный коммутатор 8 из. регистров 4 и 5 либо из блока 11 постоянной памяти, для чего по со20 ответствующим линиям управляющей шины 22 подаются соответствующие адреса регистров и команды управления шинным коммутатором 8. Одновременно по соотв етствующим линиям управляю25 щей шины 22 на арифметико-логический блок 1 подается код операций, например операции суммирования. Через такт работы устройства на выходы арифметико-логического блока 1

30 устанавливается значение суммы. Этот результат может быть выбран из устройства по информационной шине 12 либо записан в регистры 4 и 5, при . этом по управляющей шине 22 подаются соответствующие управляющие сигмаv5t5

лы,

Вып олнение операции умножения, , Эта операция выполняется умножителем 2, Сомножители- записываются в 40 буферные регистры 5 и 7, отсюда по информационным шинам 20 и 21 поступают на входы умножителя. Старшая и младшая части произведения хранятся в соответствующих внутренних регистрах умножителя 2 и могут быть считаны поочередно на информационную шину 12, для чего по шине 22 управления подается соответствующий код операции,

50 -..

Выполнение операции -сдвига. Сдвиг

осуществляется нормализатором 3 и операндом, записанным в регистре 7, Параметр сдвига подается либо по ши- gg не 20, либ9 по управляющей шине 22, по ней же подается соответствующий код операции. Результат сдвига появляется на выходе нормализатора 3 через такт работы устройства.

45

Выполнение операции нормализации. Эта операция выполняется нормализатором 3, Нормализуемый операнд поступает с регистра 7, одновременн по шине 22 поступает код операции. Через такт работы устройства мантиссу нормализованного числа можно считать с выхода нормализатора 3, а еще через такт можно считывать порядок нормализованного числа.

Выполнение операции деления. Операция деления выполняется в два этапа. На первом этапе производится вычисление функции обратной величин делителя. На втором - умножение делимого на обратную величину делителя. Операция вычисления функции обратной величины опирается на приведенные вьше операции: суммирование., вычитание, сдвиг, нормализация и умножение, а также на вспомогательное оборудование: блок 11 постоянной па мяти, регистр-счетчик 10 адреса памяти и мультиплексор 9. Исходные операнды, делимое и делитель находятся в регистрах 4 и 5. С этого момента начинается первый этап деления - нахождение обратной величины делителя.

Делитель через шинньш коммутатор 8 заносится в регистр 7 и по шине 21 поступает на вход нормализатора 3, который производит логический сдвиг влево на k+1 разряд, чем обе- спечивг ется получение величины т 2 , которая с выхода нормализатора 3 по шине 12 записывается в регистры 4 и 5, Одновременно с этим в регистр-счетчик 10 адреса памяти через мультиплексор 9 заносятся сташие k разрядов делителя, чем обеспечивается установка на адресных входах младшей части блока 11 постоянной памяти числа,.соответствующего X;, а на адресные входы старшей части ПО шине 22 управления подается код функции обратной величины. На выходе блока 11 постоянной .памяти устанавливается значение 1/х

В следуюш;ем такте работы устрой- ства производится анализ величины - щ. на нуль. Величина т-2 через шинный коммутатор 8 записывается в регистр 6 и по шине 20 поступает на вход арифметико-логического блока 1, который производит операцию сравнения на нуль. В случае по ложительного результата анализа,

т.е. т-2 . О, первый этап one-, рации деления на этом заканчивается. Значение 1/х; на выходе блока 11 побтоянной памяти будет искомым для функции обратной величины. Это значение через шинный коммутатор 8 записывается в регистр 7 и по шине 21 поступает на вход умножителя 2. Одно- временно делимое через шинный коммутатор 8 записывается в регистр 6 и по шине 20 поступает на второй вход умножителя 2, который производит операцию умножения, результат операции по шине 12 записывается в регистры 4 и 5. В случае отрицательного результата анализа, т.е. т-2 0, арифметико-логический блок .1 выполняет над присутствующим на его входе операндом га-2 , хранящимся в регистре 6 операцию дополнения, т.е. 1-т 2 , Результат этой операции с выхода,, блока -1 записывается в регистры 4 и 5. В следующем такте ве- личина 1-т 2 из регистров 4 и 5 и величина 1/х ; с выхода блока М постоянной памяти.через шинный коммутатор 8 записываются в регист- .ры 6 и 7 соответственно и по шине 20 и 21 подаются на вход умножителя 2, который производит операцию умножения, результат умножения записывается в регистры 4 и 5.

В следуюш;ем такте содержимое регистра-счетчика 10 адреса памяти увеличивается на единицу младшего разряда, чем обеспечивается получение на выходе блока постоянной памяти значения 1/Х;., которое через шинный коммутатор 8 записывается в регистр 7. Параллельно из регистров 4 и 5 значение записывается в регистр 6. По шине 20 и 21 эти значения поступают на входы умножителя 2, который производит операцию умножения , 1/х,-,, результат записывается по шине 12 в регистры 4 и 5. В следующем такте это значение mi2 - 1/х,-, , а

.параллельно с ним результат предыдущего умножения (l-m 2 ) 1/х; из регистров 4 или 5 записываются в регистры 6 и 7 соответственно и по шинам 20 и 21 поступают на-вход

ариф метико-логического блока 1, который производит операцию суммирования. На выходе блока 1 появляется искомая величина 1/х, которая по шине 12 заносится в регистры 4

и 5. На этом первый этап операции деления заканчивается, В следующем такте работы устройства значения делимого и функции обратной величины делителя с выходов регистров А и 5 через шинный коммутатор 8 заносятся в регистры 6 и 7 соответственно и по шинам 20 и 21 поступают на вход умножителя 2, Результат операции умножителя, являющийся конечным результатом операции деления записывается в регистры 4 и 5. На этом операция деления заканчивается.

Вычисление элементарных функций. Вычисление элементарных функций производится аналогично операции вычисления функции обратной величины с той лишь разницей, что на старшие разряды адреса блока 1 I постоянной памяти подается соответствующий код функции, определяющий зону ПЗУ, в которой находятся значения данной табулированной функции в опорных точках.

Повышение быстродействия арифметического устройства удается обеспечит за -счет сокращения времени выполнения операций вычисления элементарных функций.

Пример вычисления функции обратной величины.

Требуется вычислить функцию обратной величины заданную уравнением f(x) 1/х, где число х - нормировано, т, е, 2 X 1 и имеет ид

:( k 2 , где N - разрядность обрабатываемых операндов.

Интервал изменения аргумента 2 ; l разделить точками на 2 интервалов, где k - целое число меньше N. Длина каждого интервала (х,- ; х,,) составит

,.

1 - 2

.

а количество опорных точек р 2 +1, Поскольку значение в интервал изменения аргумента не входит, то количество опорных точек, для которых значение функции f(X;) определено и занесено в ПЗУ равно р , т,е, для адресации к ПЗУ необходимо k разрядов адреса, при этом емкость ПЗУ составит . N-разрядных чисел.

Подобное разбиение позволяет применить для вычисления функции обратной величины формулу для цифровой линейной интерполяции табулированной функции на малом интервале разбиения

п f (х;) + ) ) m + п

r,-(K«l)

где х; i X г х,,, m X - X, , п х,ч« - X,

m + п x,v, - х; 2 , тогда f,,, (l-m-2- ) - f (х;)+ f,;. , (Г)

Из данного выражения (1) видно, что операция вычисления функции обратной величины сводится к простым операциям сдвига, сложения и умнолСбппл (

I.

Таким образом, в предлагаемом арифметическом устройстве операция деления и вычисления обратной величины будет выполняться в среднем

за время на 40% меньше, чем в известном устройстве, а время вычисления элементарных функций будет варьироваться в тех же пределах, что и для функции обратной величины в зависимости от вида функций.

Формула изобретения

Арифметическое устройство, со-

держащее арифметико-логический блок, умножитель, нормализатор, первый и второй регистры общего назначения, первый и второй буферные регистры, мультиплексор и блок постоянной

памяти, причем выход первого буферного регистра соединен с первыми информационными входами арифметико- логического блока, умножителя и мализатора, входы разрешения записи

первого и второго регистров общего назначения, первого и второго буферных регистров , управляющие входы мультиплексора, арифметико-логического блока, умножителя и нормализатора соединены соответственно с управляющей шиной устройства, а выходы арифметико-логического блока, умножителя и нормализатора соединены соответственно с информационной

шиной устройства, отличающееся тем, что, с целью повышения быстродействия за счет сокращения времени вычисления элементарных функций, в него введены шинный .

коммутатор и регистр-счетчик адреса памяти, причем Информационные входы первого и второго регистров общего , назначения соединены соответственно с информационной шиной устройства.

7 13631868

выходы - соответственно с первым иравляющий вход блока постоянной па- вторым информационными входами шин- , мяти соединен с управляющей шиной

ного коммутатора и мультиплексора,устройства, первый и второй выходы

выход которого соединен с информаци- шинного коммутатора соединены соотонным входом регистра-счетчика адре-ветственно с информационными входами

са памяти, адресный выход которогопервого и второго буферных регис.тсоединен с младшим адресным входомров, выход второго буферного региблока постоянной памяти, управляющийстра соединен с вторыми ииформаци вуход - с информационной шиной уст- . Q онными входами арифметико-логическоройства, выход блока постоянной па-го блока, умножителя и нормализатомяти соединен с третьим информаци-ра, а синхровод регистра - счетонным входом тинного коммутатора,чика адреса памяти соединен с

управляющий вход которого соединенуправляющей шиной устройст с управляющей шиной устройства, уп-ва.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1980 |

|

SU885993A1 |

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1478213A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для решения системы алгебраических уравнений | 1981 |

|

SU966702A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

Изобретение относится к вычислительной технике и может быть .использовано при построении быстродей- ствующих операционных устройств цифровых вычислительных машин. Цель изобретения - повышение быстродействия за счет сокращения времени вычисления элементарных функций. Предлагаг ;емое устройство-содержит арифметико- логический блок 1, умножитель 2, нормализатор 3, два регистра 4, 5 общего назначения, два буферных регистра 6, 7, шинный коммутатор 8, мультиплексор 9, регистр-счетчик 10 адреса памяти и блок 11 постоянной памяти с соответствующими связями. Устройство с высоким быстродействием осуществляет выполнение арифметико-логических операций над операндами, заданными в двоичной форме. 1 ил. (Л со о: со 30 о:

| УЗЕЛ ПОДВЕСКИ КОЛЕСА АВТОМОБИЛЯ | 2009 |

|

RU2523860C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Авторское, свидетельство СССР № 885993, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-03-19—Подача