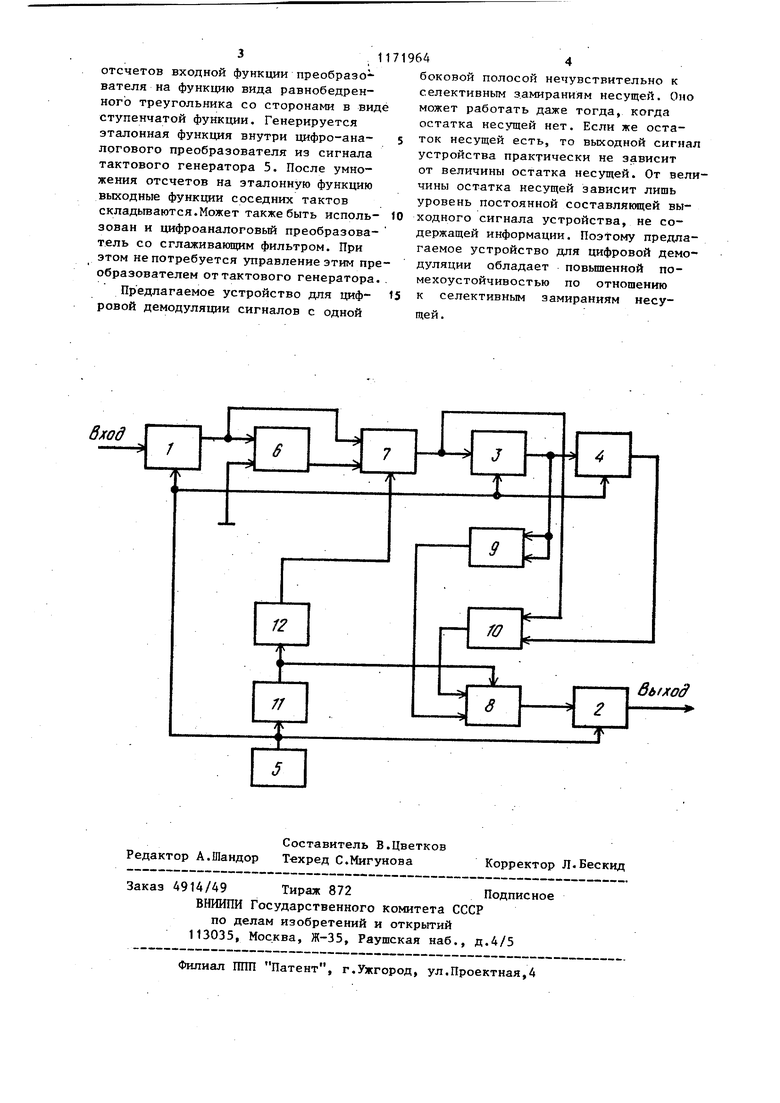

11 Изобретение относится к радиотехнике, в частности к технике связи, и может быть использовано в цифровых радиоприемных устройствах. Цель изобретения - повьшение помехоустойчивости по отношению к селективным замираниям несущей. На чертеже представлена структурная электрическая схема предлагаемого устройства д.дя цифровой демодуляции сигналов с рдной боковой полосой Устройство содержит аналого-цифро вой преобразователь 1, цифроаналоговый преобразователь 2., последователь но соединенные первый 3 и второй 4 элементы задержки, тактовьй генератор 5, цифровой вычитатель 6, первьй 7 и второй 8 коммутаторы, первьй 9 и второй 10 цифровые сумматоры, первьй 11 и второй 12 делители частоты на два. Устройство работает следующим образом. Входной сигнал поступает на сигнальньй вход аналого-цифрового преоб разователя 1, в котором подвергается дискретизации с периодом, равным нечетному числу четвертей периода несущей частоты. Последовательность выборок входного сигнала поступает на первый вход цифрового вычитателя 6. Первьй вход цифрового вычитателя 6 является входом вычитаемого. На второй вход цифрового вычитателя 6, т.е. на вход уменьшаемого, подается константа, равная нулю, так как данньй вход соединен с общей шиной. В результате на выходе цифрового вычитателя 6 получается последовательность выборок входного сигнала, как на выходе аналого-цифрового преобразователя 1, но с измененными на противоположные знаками во всех позициях. Первьй коммутатор 7 осуществляет переключение на свой выход обоих последовательностей вьШорок входного сигнала с периодом в 4 такта: в течение двух тактов берется отсчет с одного входа, в течение двух следующих - с другого. Такой режим работы коммутатора 7 обеспечивается подачей на его вход синхронизации импульсов с выхода второго делителя 12 частоты на два. Выходная последовательность выборок первого коммутатора 7 задерживается двумя, последовательно соединенными элементами за42держки 3 и 4. Каждьй элемент задержки 3 и 4 вносит задержку на один такт. На выходе первого цифрового сумматора 9 получается последовательность выборок, аналогичная последовательности выборок на выходе первого элемента 3 задержки, но с удвоенными значениями. На выходе второго сумматора 10 формируется последовательность выборок, отсчеты в которой равны удвоенным значениям, интерполируемым по формуле Х.(п) I X(n-i-l) + Х(п-1). (1) Выходы обоих цифровых сумматоров соединены с входами второго коммутатора 8, которьй осуществляет выборку на свой выход отсчетов с двух входов попеременно. На четных тактах он передает на свой выход сигнал с выхода одного цифрового сумматора, на нечетных - с выхода другого. Такой режим работы второго коммутатора 8 обеспечивается подачей на его вход синхронизации управляющих импульсов с выхода первого делителя.11 частоты на два. Выходная функция второго коммутатора 8 совпадает с модулирующим сигналом при любом такте. Выход второго коммутатора 8 соединен с входом цифроаналогового преобразователя 2. На выходе цифроаналогового преобразователя 2 получается модулирующий сигнал в аналоговой форме. Работа аналого-цифрового преобразователя 1, цифроаналогового преобразователя 2 и последовательно соединенных элементов 3 и 4 задержки происходит в темпе, задаваемом управляющими импульсами от тактового генератора 5. Б состав аналого-цифрового преобразователя 1 входит устройство выборки и хранения и кодировщик. Кроме того, в зависимости от способа вьтолнения аналого-цифрового преобразователя в его состав может войти и более высокочастотньй генератор, обеспечивающий функционирование преобразователя. В качестве цифро-аналогового преобразователя 2 может использоваться преобразователь, в котором для сглаживания выходной аналоговой функции используется прием аппроксимации линии, соединяющей два соседних отсчета ступенчатой функцией с большим числом ступеней. Для работы такого преобразователя осуществляется умножение

311

отсчетов входной функции преобразо вателя на функцию вида равнобедренного треугольника со сторонами в виде ступенчатой функции. Генерируется эталонная функция внутри цифро-аналогового преобразователя из сигнала тактового генератора 5. После умножения отсчетов на эталонную функцию выходные функции соседних тактов складьгеаются.Может также быть использован и цифроаналоговый преобразователь со сглаживающим фильтром. При этом не потребуется управление этим преобразователем от тактового генератора.

Предлагаемое устройство для цифровой демодуляции сигналов с одной

644

боковой полосой нечувствительно к селективньм замираниям несущей. Оно может работать даже тогда, когда остатка несущей нет. Если же остаток несущей есть, то выходной сигнал устройства практически не зависит от величины остатка несущей. От величины остатка несущей зависит лишь уровень постоянной составляющей выходного сигнала устройства, не содержащей информации. Поэтому предлагаемое устройство для цифровой демодуляции обладает повьппенной помехоустойчивостью по отношению

к селективным замираниям несущей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой демодуляции сигналов с одной боковой полосой | 1982 |

|

SU1095348A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ КРАТКОВРЕМЕННЫХ СИГНАЛОВ С МНОГОУРОВНЕВОЙ АБСОЛЮТНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ В УСЛОВИЯХ ЗАМИРАНИЙ | 2018 |

|

RU2684605C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ | 1991 |

|

RU2019049C1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1984 |

|

SU1223373A2 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Система передачи данных | 1986 |

|

SU1462507A1 |

| Устройство адаптивного приема дискретных сигналов | 1982 |

|

SU1113891A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

УСТРОЙСТВО ДНЯ ЦИФРОВОЙ ДЕМОДУЛЯЦИИ СИГНАЛОВ С ОДНОЙ БОКОВОЙ ПОЛОСОЙ, содержащее аналого-цифровой преобразователь, сигнальньй вход которого является вхрдом устройства, цифроаналоговый преобразователь, выход которого является выходом устройства, последовательно соединенные первый и второй элементы задержки и тактовьЁ генератор, выход которого соединен с входами синхронизации aiia-i лого-цифрового и цифроаналогового преобразователей, первого и второго элементов задержки, отличающееся тем, что, с целью повьшения помехоустойчивости по отношению к селективным замираниям несущей, в него введены цифровой вычйтатель. первый и второй коммутаторы, первьй и второй цифровые сумматоры и последовательно соединенные первый и второй делители частоты на два, при этом выход аналого-цифрового преобразователя соединен с первым входом цифрового вычитателя и первым входом первого коммутатора, второй вход которого соединен с выходом цифрового вычитателя, выход первого коммутатора подключен к входу первого элемента задержки и к первому входу второго цифрового сумматора, второй вход которого подсоединен к выходу второго эле § мента задержки, первый и второй входы первого цифрового сумматора объедине(Л ны и подключены к выходу первого элемента задержки, выходы первого и второго цифровых сумматоров подсоединены соответственно к первому и второму входам второго коммутатора, выход которого соединен с входом цифроаналогового преобразователя, входы синхронизации первого и второго коммутаторов подключены соответственно к вы ходам второго и первого делителей Од частоты на два, вход первого делителя частоты на два соединен с выходом тактового генератора, а второй вход цифрового вычитателя - с общей шиной.

i

toi

/2

П

I

ГО

Bbfxoff

8

| Френк П.Чиффи и др | |||

| Signal | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство для цифровой демодуляции сигналов с одной боковой полосой | 1982 |

|

SU1095348A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-07—Публикация

1983-07-08—Подача