Изобретение относится к регулирующим и управляющим системам общего назначения и может быть использовано для ис пытания, контроля и диагностики неисправностей устройств ввода - вывода двоичной информацииj представленной в виде кодовых комбинаций.

По основному авт.св. 1038926 известно устройство ДПЯЕ задания тестов , содержащее блок установки адреса, счетчик импульсов, дешифратор, первый формирователь иьтульсов,. генератор тактовых импульсов, второй формирователь импульсов, блок задания начального .кода,блок сумматоров, коммутатор, регистр числа,блок элементов И, схему И и блок управления, причем выходы блока установки адреса соединены с установочными s-входами счетчика импульсов, выходы которого подключены к входу дешифратора, соединенного своим выходом с первым входом второго формирователя импульсов, второй вход которого подключен к первому -выходу блока управления и к первому входу блока задания начального кода, а выход соединен с обнуляющим R-входом регистра числа и счетчика импульсов, а также с входом генератора тактовых импульсов и с входом второго формирователя импульсов, выход генератора тактовых импульсов подключен к счетному входу счетчика импульсов и к первому входу схемы И, втЬрой вход которой соединен с вторым выходом блока управления, а выход с С-входом регистра числа, выход второго формирователя импульсов подключен к второму входу блока задания начального кода и к управляющим входам блока элементов И, выходы блока установки начального кода соединены с первыми А-.входами блока сумматоров и через блок элементов И подаются на установочные 5-Бходы регистра числа, числовые s-выходы блока сумматоров подключены .к первым входам коммутатора, выход Pjg и вход РО переноса блока сумматоров соединены, выходы коммутаторов подключены к D-вкодам регистра числа, выходы которого соединены с втогмлми входами коммутаторов и вторыми В-входами блока сумматоров, управляющий вход коммутатора соединен с третьим выходе блока управления 1 .

Известно, что радиоэлектронные устройства с магнитной памятью,подвержены воздействию нескомпенсированных помех в выходной обмотке накопителя, приводящих к искажению информации в цепях считывания и разрушению ее в накопителе при регенерации. Помехи обусловлены, в частности , магнитной предысторией сердечников.

Известное техническое решение обеспечивает формирование тестов типа псевдослучайный., сдвиговый и постоянный коды. Однако эти тесты не обеспечивают проверку радиоэлектронных 5 блоков с учетом магнитной предыстории, т.е. известное устройство не позволяет проверить достоверно,точно и полно радиоэлектронные блоки с многоадресной магнитной памятью,что

0 ограничивает его применение.

Целью изобретения является расширение функционашьных возможностей устройства за счет повшнения достоверности и полноты контроля, диагнос5 тических возможностей проверки радиоэлектронных блоков с многоё1дресной магнитной, памятью.

Поставленная цель достигается тем, что в устройство для задания

0 тестов введен блок инверсии, содержгиций триггер, соединенный счетным входом с. выходом (Второго формирователя импульсов, а прякым выходом - с первым входом второго дополнитель5 ного элемента И, подключенного вторым входом к первому выводу первого ключа, а выходом - к первому входу третьего дополнительного элемента И и к входу первого элемента НЕ, соединенного выходом с первым вхо дом четвертого дополнительного элемента И и с первым входом пятого дополнительного элемента И, подключенного вторым входом к выходу второго элемента НЕ, связанного входом

5 с первым выводом второго ключа и со вторь входом третьего дополнительного элемента И, подключенного третьим входом к выходу первого разряда счетчика импульсов и ко входу

0 третьего элемента НЕ, соединенного - выходом со входом четвертого дополнительного элемента И, подключенного выходом к первому входу элемента ИЛИ-НЕ, связанного вторым и

5 третьим входами с выходами третьего и пятого дополнительных элементов И, а выходом - с первыми входами блока элементов ИСЮВОЧАЮЩЕЕ ИЛИ, подключенного вторыми входами к соответстп вующим выходам регистра числа, причем второй и третий; выводы первого и второго ключей подключены соответственно к шинам ключей Логическая 1 и Логический О.

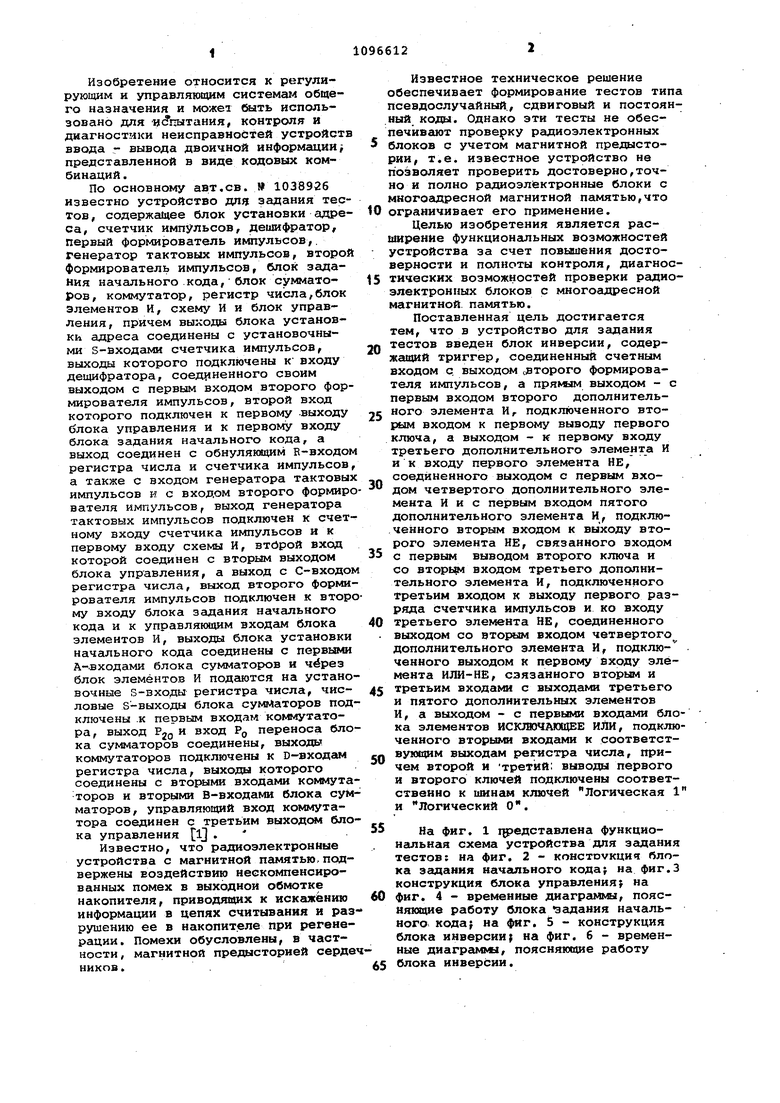

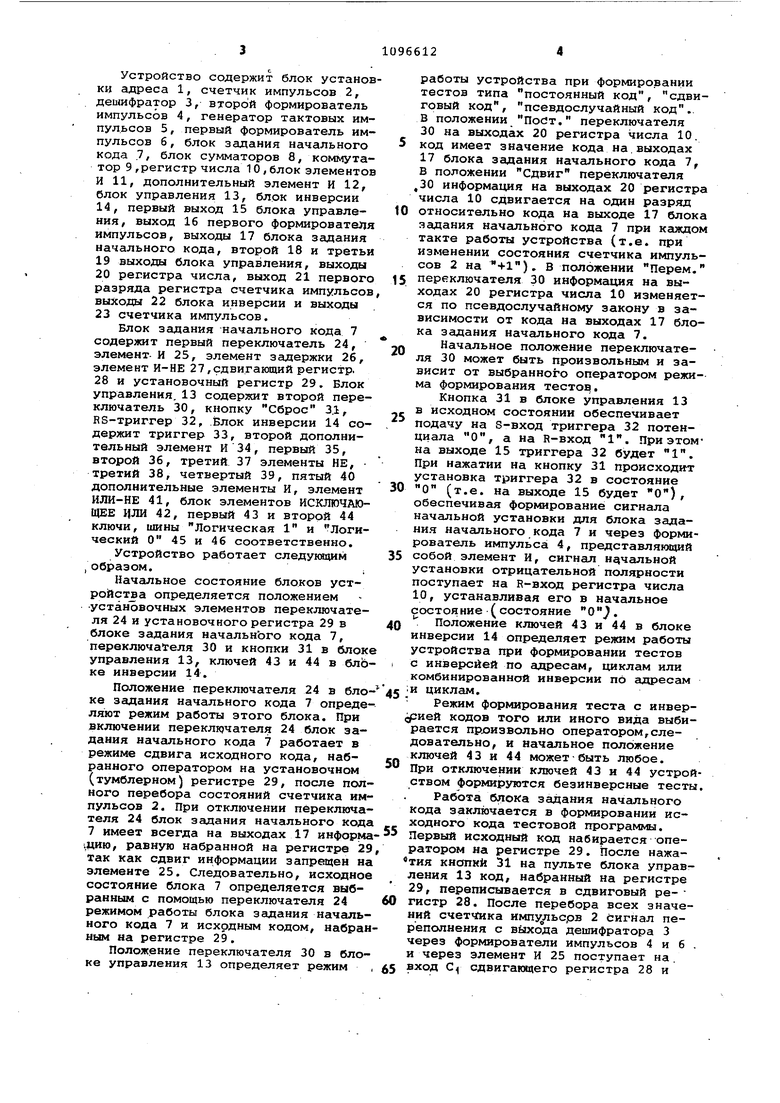

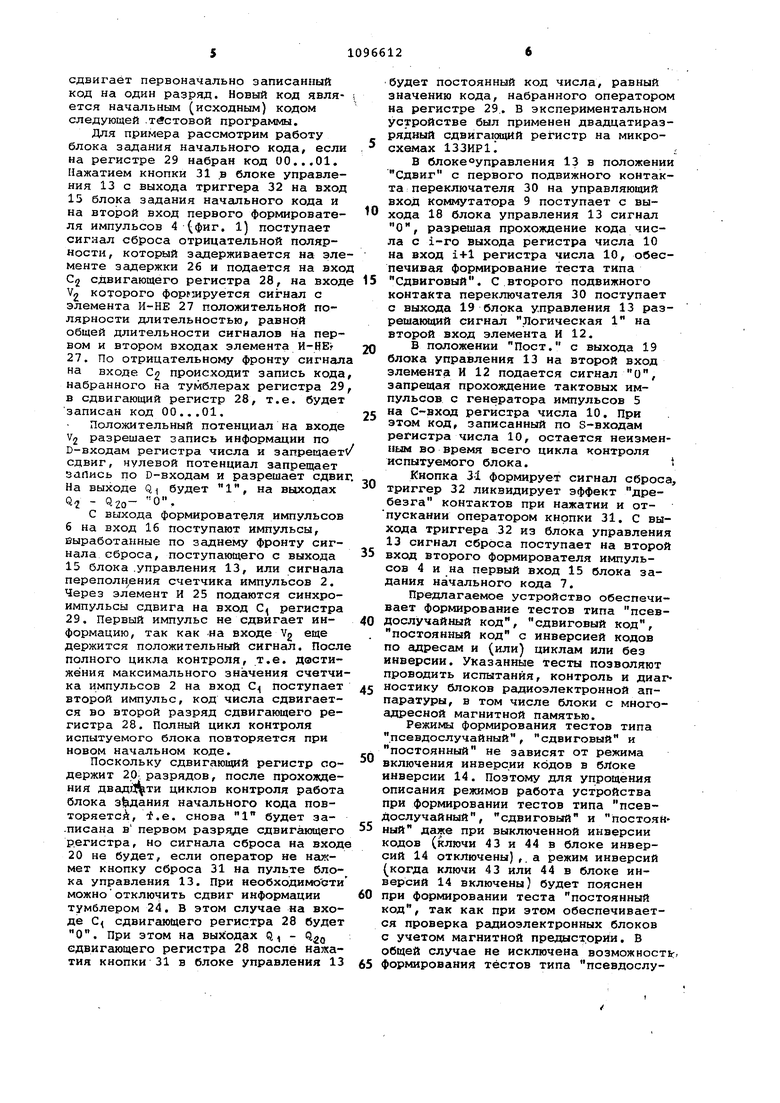

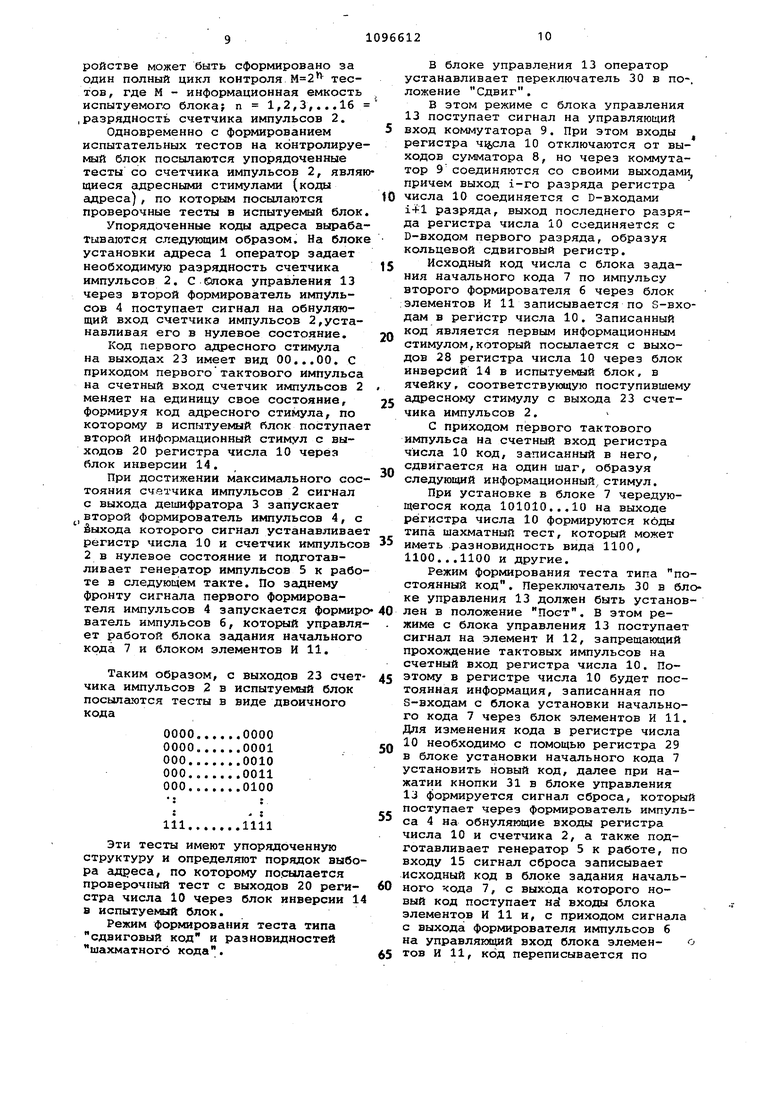

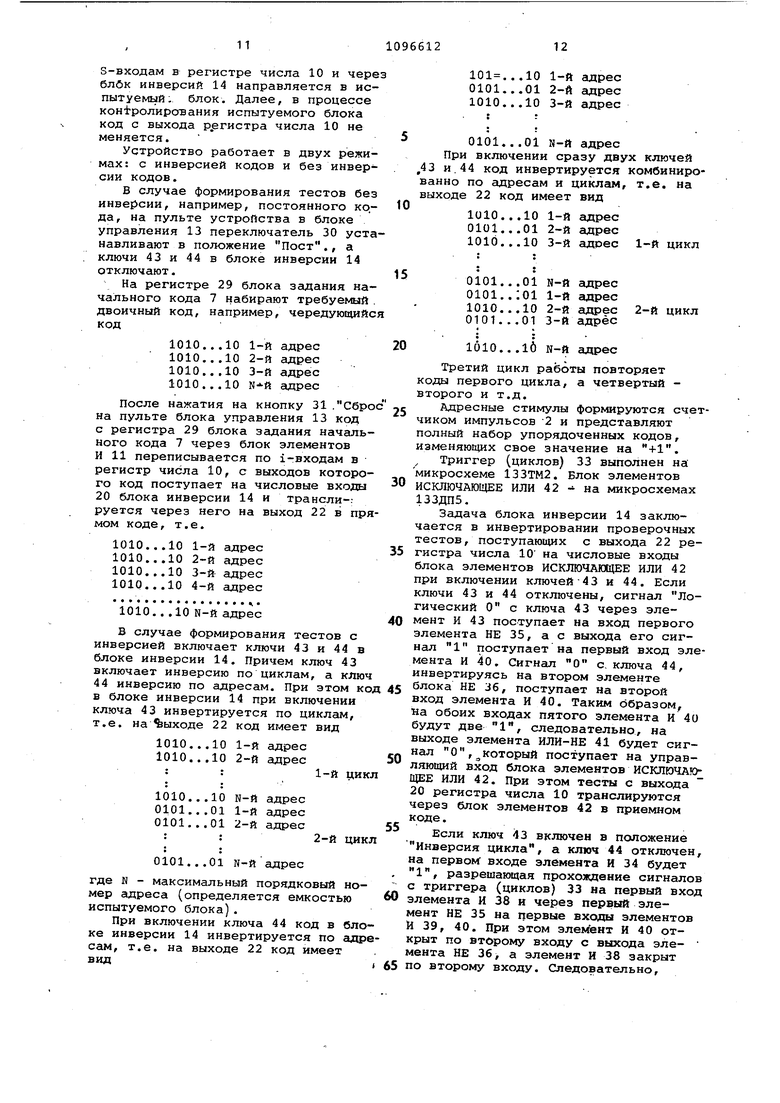

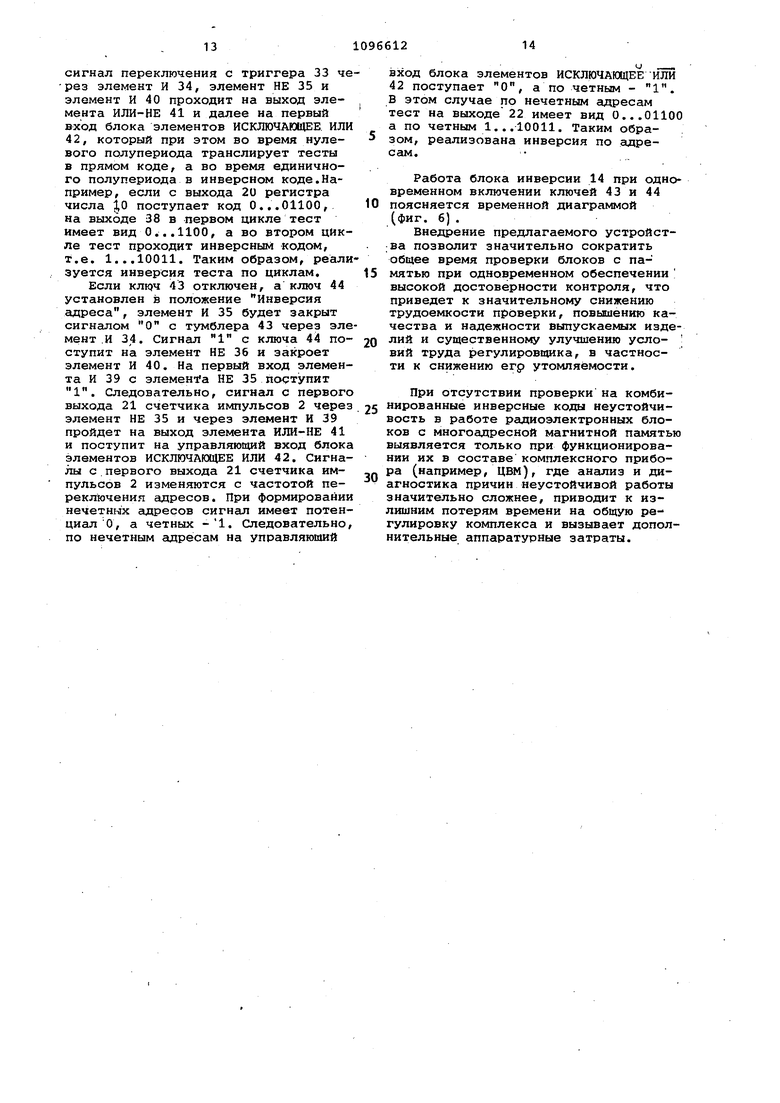

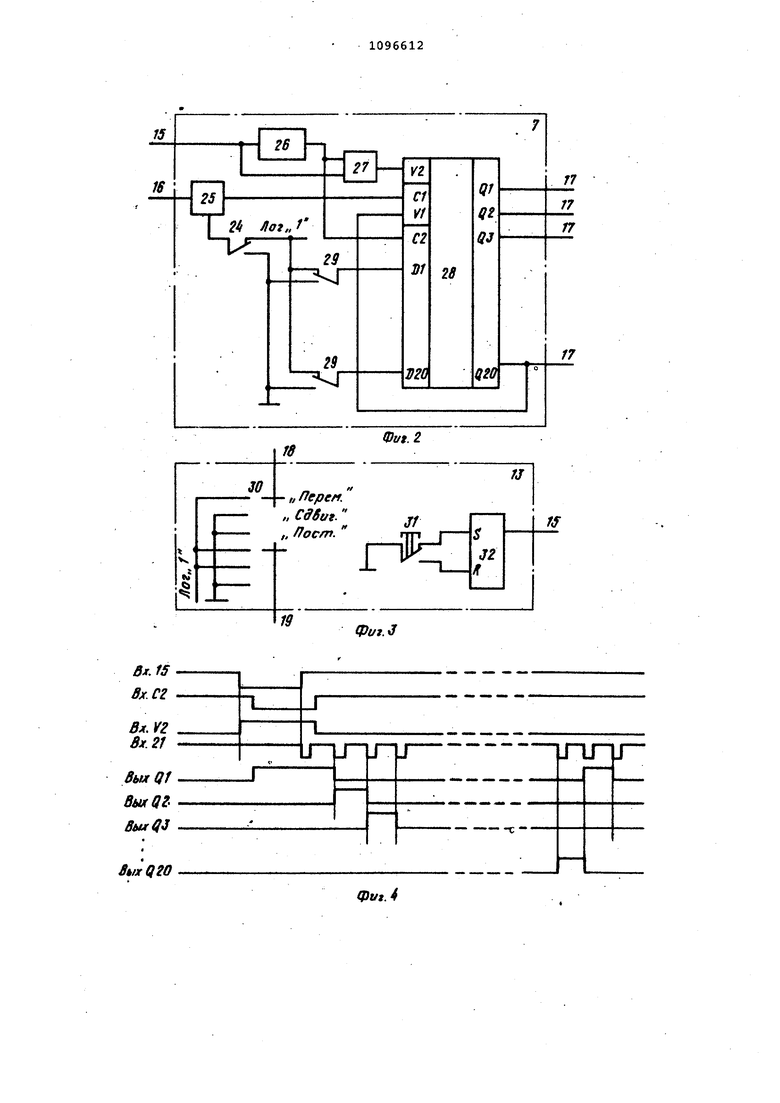

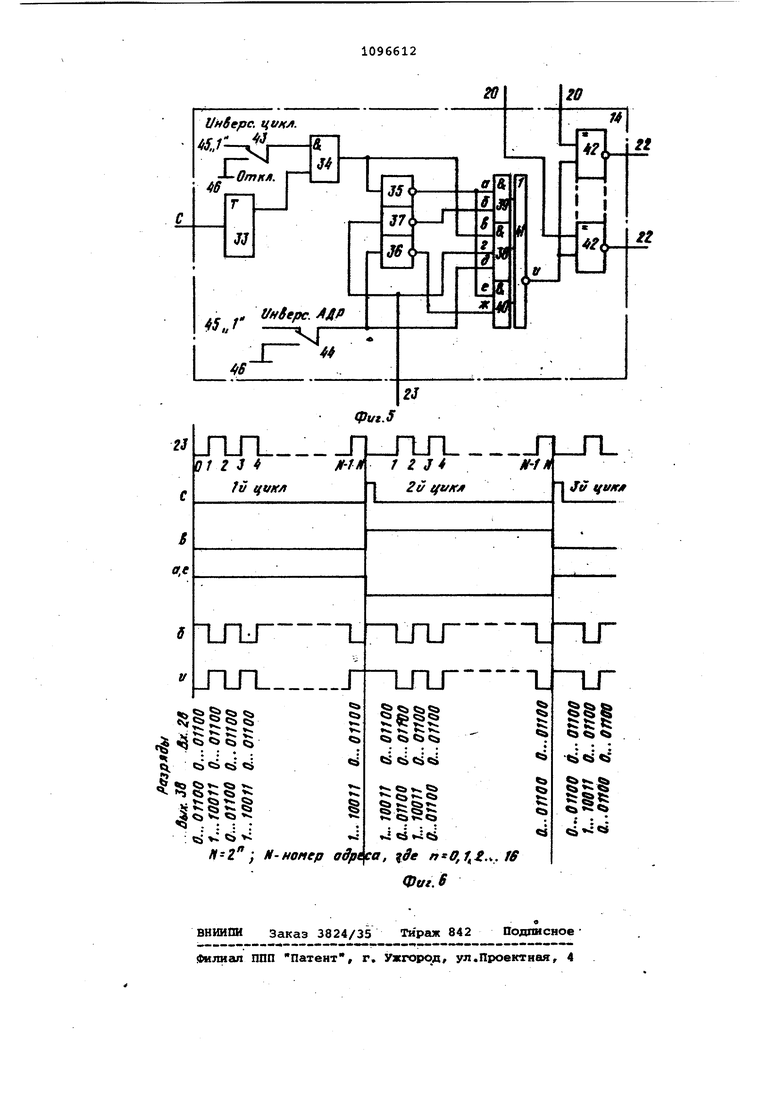

5 На фиг. 1 щ едставлена функциональная схема устройства для задания тестов; на фиг. 2 - констоукцич блока задания начального кода; на фиг.З конструкция блока управления на

0 фиг. 4 - временные диаграгфш, поясняющие работу блока -задания начального, кода; на фиг. 5 - конструкция блока инверсии; на фиг. 6 - временные диагрс м1«1, поясняющие работу

5 блока инверсии.

Устройство содержит блок установки адреса 1, счетчик импульсов 2, дешифратор 3, второй формирователь импульсов 4, генератор тактовых импульсов 5, первый формирователь импульсов б, блок задания начального кода .7, блок сумматоров 8, коммутатор 9 ,регистр числа 10, блок элементов И 11, дополнительный элемент И 12, блок управления 13, блок инверсии 14, первый выход 15 блока управления, выход 16 первого формировате/1я импульсов, выходы 17 блока задания начального кода, второй 18 и третьи

19выходы блока управления, выходы

20регистра числа, выход 21 первого разряда регистра счетчика импульсов, выходы 22 блока инверсии и выходы

23 счетчика импульсов.

Блок згшания -начального кода 7 содержит первый переключатель 24, элемент. И 25, элемент згшержки 26, элемент И-НЕ 27,сдвигающий регистр. 28 и установочный регистр 29, Блок управления. 13 содержит второй переключатель 30, кнопку Сброс 3.1, RS-триггер 32, Блок инверсии 14 содержит триггер 33, второй дополнительный элемент И 34, первый 35, второй 36, третий 37 элементы НЕ, третий 38, четвертый 39, пятый 40 дополнительные элементы И, элемент ИЛИ-НЕ 41, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42, первый 43 и второй 44 ключи, шины Логическая 1 и Логический О 45 и 46 соответственно.

Устройство работает следующим /образом.;

Начальное состояние блоков устpoftcTjia определяется положением установочных элементов переключателя 24 и установочного регистра 29 в блоке задания начальнЬго кода 7, переключателя 30 и кнопки 31 в блоке управления 13, ключей 43 и 44 в блоке инверсии 14.

Положение переключателя 24 в блоке задания начального кода 7 определяют режим работы этого блока. При включении переключателя 24 блок задания начального кода 7 работает в режиме сдвига исходного кода, набранного оператором на установочном (тумблерном) регистре 29, после полного перебора состояний счетчика импульсов 2. При отключении переключателя 24 блок задания начального кода 7 имеет всегда на выходах 17 информа,цию, равную набранной на регистре ;29 так как сдвиг информации запрещен на элементе 25. Следовательно, исходное состояние блока 7 определяется выбранным с помощью переключателя 24 режимом работы блока задания начального кода 7 и исходным кодом, набранным на регистре 29.

Положение переключателя 30 в блоке управления 13 определяет режим

работы устройства при формировании тестов типа постоянный код, сдвиговый код, псевдослучайный код.. В положении Поит. переключателя 30 на выходах 20 регистра числа 10. код имеет значение кода на.выходах 17 блока задания начального кода 7, В положении Сдвиг переключателя

,30 информация на выходах 20 регистр числа 10 сдвигается на один разряд относительно кода на выходе 17 блок задания начального кода 7 при Кс1ждо такте работы устройства (т.е. при изменении состояния счетчика импульсов 2 на -fl). В положении Перем. переключателя 30 информация на выходах 20 регистра числа 10 изменяется по псевдослучайному закону в зависимости от кода на выходах 17 блока задания начального кода 7.

Начальное положение переключателя 30 может быть произвольным и зависит от выбранного оператором режима формирования тесто.

Кнопка 31 в блоке управления 13 в исходном состоянии обеспечивает подачу на S-вход триггера 32 потенциала О, а на R-вход 1. При этомна выходе 15 триггера 32 будет 1. При нажатии на кнопку 31 происходит установка триггера 32 в состояние О (т.е. на выходе 15 будет О), обеспечивая формирование сигнала начальной установки для блока задания начального кода 7 и через формирователь импульса 4, представлякнций собой элемент И, сигнал нд чальной установки отрицательной полярности поступает на R-вход регистра числа 10, устанавливая его в начальное состояние (состояние 0.

Положение ключей 43 и 44 в блоке инверсии 14 определяет режим работы устройства при формировании тестов с инверсией по адресам, циклам или комбинированной инверсии по адресам

и циклам.

Режим формирования теста с инвер,:рией кодов того или иного вида выбирается пр.оизвольно оператором,следовательно, и начальное положение ключей 43 и 44 может-быть любое. При отключении ключей 43 и 44 устроством формируются безинверсные тесты

Работа блока задания начального кода заключается в формировании исходного кода тестовой программы. Первый исходный код набирается оператором на регистре 29. После нажа тия кнопки 31 на пульте блока управления 13 код, набранный на регистре 29, переписывается в сдвиговый ре- гистр 28. После перебора всех значений счетчсика лгшу/1ъсрв 2 сигнал переполнения с вьвсода дешифратора 3 через формирователи импульсов 4 и 6 и через элемент И 25 поступает на. вход Of сдвигающего регистра 28 и

сдвигает первоначально записанный код на один разряд. Новый код является начальным (исходным) кодом следующей .тестовой программы.

Для примера рассмотрим работу блока задания начального кода, если на регистре 29 набран код 00...01. Нажатием кнопки 31 ,в блоке управления 13 с выхода триггера 32 на вход 15 блока задания начального кода и на второй вход первого формирователя импульсов 4 (фиг, 1) поступает сигнал сброса отрицательной полярности, который задерживается на элементе задержки 26 и подается на вход Cj сдвигающего регистра 28, на входе Vg которого форрмруется сигнал с элемента И-НЕ 27 положительной полярности длительностью, равной общей длительности сигналов на первом и втором входах элемента И-НВг 27. По отрицательному фронту сигнггла на входе Cg происходит запись кода, набранного на тумблерах регистра 29, в сдвигающий регистр 28, т.е. будет записан код 00...01.

Положительный потенциал на входе Vj разрешает запись информации по D-входам регистра числа и запрещаете сдвиг, нулевой потенциал запрещает запись по D-входам и разрешает сдвиг На выходе Q, будет 1, на выходах Qj - QZO- О.

С выхода формирователя импульсов 6 на вход 16 поступают импульсы, выработанные по заднему фронту сигнала сброса, поступающего с выхода 15 блока .управления 13, или сигнала переполнуения счетчика импульсов 2. Через элемент И 25 подаются синхроимпульсы сдвига на вход С регистра 29. Первый импульс не сдвигает информацию, так как -на входе Vg еще держится положительный сигнал. После полного цикла контроля, т.е. достижения максимального значения счетчика импульсов 2 на вход С поступает второй импульс, код числа сдвигается во второй разряд сдвигающего регистра 28. Полный цикл контроля испытуемого блока повторяется при новом начальном коде.

Поскольку сдвигающий регистр содержит 20 разрядов, после прохождения двадй ти циклов контроля работа блока задания начального кода повторяетсА, i.e. снова 1 будет за.писана в первом разряде сдвигающего регистра, но сигнала сброса на входе 20 не будет, если оператор не нажмет кнопку сброса 31 на пульте блока управления 13. При иеобходимости можноотключить сдвиг информации тумблером 24. В этом случае на входе С сдвигающего регистра 28 будет О. При этом на выходах Q, - сдвигающего регистра 28 после нажатия кнопки 31 в блоке управления 13

будет постоянный код числа, равный значению кода, набранного оператором на регистре 29. В экспериментальном устройстве был применен двадцатиразрядный сдвигакицйй регистр на микро5 схемах 133ИР11;

В блоке°управления 13 в положении Сдвиг с первого подвижного контакта переключателя 30 на управляющий вход коммутатора 9 поступает с вы0 хода 18 блока управления 13 сигнал О, разрешая прохождение кода числа с i-ro выхода регистра числа 10 на вход i+1 регистра числа 10, обеспечивая формирование теста типа

5 Сдвиговый. С второго подвижного контакта переключателя 30 поступает с выхода 19 блока управления 13 разрешакхций сигнал Логическая 1 на второй вход элемента И 12.

Q В положении Пост. с выхода 19 блока управления 13 на второй вход элемента И 12 подается сигнал О, запрещая прохождение тактовых импульсов с генератора импульсов 5

5 на С-вход регистра числа 10. При этом код, записанный по s-входам регистра числа 10, остается неизменным во время всего цикла контроля испытуемого блока.

Кнопка 31 формирует сигнал сброса,

0 триггер 32 ликвидирует эффект дребезга контактов при нажатии и отпускании оператором кнопки 31. С выхода триггера 32 из блока управления 13 сигнсш сброса поступает на второй

5 вход второго формирователя импульсов 4 и на первый вход 15 блока задания начального кода 7.

Предлагаемое устройство обеспечивает формирование тестов типа псев0 Дослучайный код, сдвиговый код, . постоянный код с инверсией кодов по адресам и (или) циклам или без инверсии. Указанные тесты позволяют проводить испытания, контроль и диаг5 ностику блоков радиоэлектронной аппаратуры, в том числе блоки с многоадресной магнитной памятью.

Режимы формирования тестов типа псевдослучайный, сдвиговый и постоянный не зависят от режима

включения инверсии кодов в блоке инверсии 14. Поэтому для упрощения описания режимов работа устройства при формировании тестов типа псевдослучайный, сдвиговый и постоян5 ный даже при выключенной инверсии кодов (ключи 43 и 44 в блоке инверсий 14 отключены),. а режим инверсий (когда ключи 43 или 44 в блоке инверсий 14 включены) будет пояснен

0 при формировании теста постоянный код, так как при этом обеспечивается проверка радиоэлектронных блоков с учетом магнитной предыстории, в общей случае не исключена возможность:,

5 формирования тестов типа псевдослучайный код и сдвиговый код с ком бинацией инверсии по адресам и или циклам. Работа устройства без инверсии кодов. Ключи 43 и 44 в блоке инверсии 1 отключены, В этом случае с первого вывода ключа 43 Инверсия цикла на вход элемента И 34 поступает О следовательно, на выходе элемента И 34 будет также О, который подается на вход первого элемента НЕ 35 На его выходе будет 1, которая поступает на первый вход элемента И 40 с первого вывода ключа 44 Ин версия адреса, О подается на вхо элемента НЕ 36, с выхода которого 1, поступает на второй вход элемен та И.40.Так как на входах элемента И 40 будут потенциалы 1 , на выходе эле- Мента ИЛИ-НЕ 41будет О, который подается на управляющий вход блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42. В это случае коды через блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42 проходят с выходов 20 регистра числа 10 без измене ния. Поэтому можно считать, что при выключенных ключах 43 и 44 в блоке инверсии 14 формирование тестов заканчивается в регистре числа 10. Формирование теста типа псевдослучайный код. В блоке управления 13 переключатель 30 оператор Остана ливает в положение Перем. В этом случае с блока управления 13 посту, пает сигнал на управляющий вход ком мутатора 9, разрешающий прохождение двоичного числа с выхода блока сумматоров 8 на D-входы регистра числа 10 одновременно с блока управления 13 поступают сигналы разрешения на пер вый вход элемента И 12.Для приведе,ния устройства в исходное состояние в блоке управления 13 наяатием кноп ки 31 формируется сигнал сброса отрицательной полярности, который проходит через второй формирователь импульсов 4 и устанавливает в начальное состояние счетчик импульсов 2, регистр числа 10, генератор импульсов 5. Кроме того, сигнал сброса отрицательной полярности с в хода 15 блока управления 13 поступает для установки в исходное состо ние блока задания начального кода 7 в котором оператор предварительно набирает исходный код с помощью регистра 29. Исходный код с выходов 17 блока установки начального кода через блок элементов И 11 записывается в регистр числа 10, формируя двоичный код, который является первым испытательным информационным стимулом псевдослучайного теста. За тем тактовые импульсы с генератора импульсов 5 поступает на счетный вх счетчика импульсов 2 и через элемент И 12 на счетный вход регистра числа 10. Исходное число с блока задания начального кода 7 поступает на А-входы блока сумматоров 8, на вторые В-входм которого приходит двоичный код с выхода регистра числа ; В блоке сумматоров 8 происходит сложение исходного числа с кодом ранее записанным в регистр числа 10 с блока задания начального кода 7. Например, из блока задания начгшьного кода 7 поступает число 00011001 , набранное оператором ha тумблерном регистре 29 в блоке задания начального кода 7 (для примера взято восьмиразрядное слово),. которое является первым проверочным стимулом. Вторым проверочным стимулом является результат от сложения .000.11001. OOOllOOl 00110010 С выхода блока сумматоров 8 двоичный код транспортируется через коммутатор на D-входы регистра числа 10 и при поступлении первого тактового импульса с элемента И 12 записывается в него. Так заканчивается формирование второго информационного стимула, который с выходов 20 регистра числа 10 посылается через блок инверсии 14 в ксталтуемай блок и на вторые В-входы блока сумматоров 8, где происходит сложение результирующего кода с исходным кодом, т.е. 0.0.11.0.010. 00011001 01001011 При поступлении на счетный вход регистра числа 10 тактового импульса результат суммирования записывается через коммутатор 9 в регистр числа 10, образуя третий испытательный стимул тестов. Аналогично получен четвертый тест 0.100.1011. 00011001 oiiooiao Чтобы проанализировать полученные тесты выпишем их в порядке следования 00011001, 00110010, 01001011, 01100100. J Представленные тесты не имеют упорядоченной структуры, но строго детерминиро1заны во времени, т.е. могут быть повторены в той же послеовательности, что необходимо при контроле блоков апоминакицих уст-ройств, когда в г ервом цикле проверки осуществляется запись информации, а в следующем будет считывание. Та- . кие тесты носят название.псевдослуайные. Всего в предлагаемом устройстве может быть сформировано за один полный цикл контроля тестов, где М - информационная емкость испытуемого блока; п 1,2,3,...16 .разрядность счетчика импульсов 2. Одновременно с формированием испытательных тестов на контролируе мый блок посылаются упорядоченные тесты со счетчика импульсов 2, явля щиеся адресными стимулами (коды адреса), по которым посылаются проверочные тесты в испытуемый блок Упорядоченные коды адреса выраба тываются следующим образом. На блок установки адреса 1 оператор задает необходимую разрядность счетчика импульсов 2. С еиока управления 13 через второй формирователь импульсов 4 поступает сигнгш на обнуляющий вход счетчика импульсов 2,уста навливая его в нулевое состояние. Код первого адресного стимула на выходах 23 имеет вид 00...00. С приходом первоготактового импульс на счетный вход счетчик импульсов меняет на единицу свое состояние, формируя код адресного стимула, по которому в испытуемый блок поступа второй информационный стимул с выходов 20 регистра числа 10 черея блок инверсии 14. При достижении максимального со тояния счатчика импульсов 2 сигнал с выхода дешифратора 3 запускает , второй формирователь импульсов 4, ёыхода которого сигнал устанавлива регистр числа 10 и счетчик импульс 2 в нулевое состояние и подготавливает генератор импульсов 5 к раб те в следующем такте. По заднему фронту сигнала первого формирователя импульсов 4 запускается форми ватель импульсов 6, который управл ет работой блока згшания начальног кода 7 и блоком элементов И 11. Таким образом, с выходов 23 сче чика импульсов 2 в испытуемый блок посылаются тесты в виде двоичного кода 0000.0000 0000„0001 000..0010 000.......ООН 000.0100 1111111 Эти тесты имеют упорядоченную структуру и определяют порядок выб ра адреса, по которому по.сылается проверочный тест с выходов 20 реги стра числа 10 через блок инверсии в испытуемый блок. Режим формирования теста типа сдвиговый код и разновидностей шахматного кода. В блоке управления 13 оператор устанавливает переключатель 30 в по-, ложение Сдвиг. В этом режиме с блока управления 13 поступает сигнал на управляющий вход коммутатора 9. При этом входы регистра Ч14сла 10 отключаются от выходов сумматора 8, но через коммутатор 9 соединяются со своими выходами, причем выход i-ro разряда регистра числа 10 соединяется с D-входами i+1 разряда, выход последнего разряда регистра числа 10 соединяется с D-входом первого разряда, образуя кольцевой сдвиговый регистр. Исходный код числа с блока задания начального кода 7 по импульсу второго формирователя 6 через блок элементов И 11 записывается по S-входам в регистр числа 10. Записанный код является первым информационным стимулом,который посылается с выходов 28 регистра числа 10 через блок инверсий 14 в испытуемый блок, в ячейку, соответствующую поступившему адресному стимулу с выхода 23 счетчика импульсов 2. С приходом первого тактового импульса на счетный вход регистра числа 10 код, записанный в него, сдвигается на один шаг, образуя следующий информационный, стимул. При установке в блоке 7 чередующегося кода 101010...10 на выходе регистра числа 10 формируются коды типа шахматный тест, который может иметь разновидность вида 1100, 1100...1100 и другие. Режим формирования теста типа постоянный код. Переключатель 30 в блоке управления 13 должен быть установлен в положение Пост. В этом режиме с блока управления 13 поступает сигнал на элемент И 12, запрещающий прохождение тактовых импульсов на счетный вход регистра числа 10. Поэтому в регистре числа 10 будет постоянная информация, записанная по S-входам с блока установки начального кода 7 через блок элементов И 11. Для изменения кода в регистре числа 10 необходимо с помощью регистра 29 в блоке установки начального кода 7 установить новый код, дгшее при нажатии кнопки 31 в блоке управления 13 формируется сигнал сброса, который поступает через формирователь импульса 4 на обнуляющие входы регистра числа 10 и счетчика 2, а также подготавливает генератор 5 к работе, по входу 15 сигнал сброса записывает исходный код в блоке задания начального кода 7, с выхода которого новый код поступает ни входы блока элементов И 11 и, с приходом сигнала с выхода формирователя импульсов 6 на управляю1ций вход блока элемен- о тов и 11, код переписывается по S-входам в регистре числа 10 и чер блбк инверсий 14 направляется в ис пытуемый: блок. Далее, в процессе контролирования испытуемого блока код с выхода регистра числа 10 не меняется. Устройство работает в двух режи мах: с инверсией кодов и без инвер сии кодов. В случае формирования тестов бе инверсии, например, постоянного ко. да, на пульте устройства в блоке управления 13 переключатель 30 уст навливают в положение Пост., а ключи 43 и 44 в блоке инверсии 14 отключают. На регистре 29 блока задания на чального кода 7 набирают требуемый двоичный код, например, чередующий код 1010...10 1-й адрес 1010...10 2-й адрес 1010...10 3-й адрес 1010...10 адрес После нажатия на кнопку 31 .Сбр на пульте блока управления 13 код с регистра 29 блока згшания началь ного кода 7 через блок элементов И 11 переписывается по i-входам в регистр числа 10, с выходов которо го код поступает на числовые входы 20 блока инверсии 14 и трансли-.руется через него на выход 22 в пр мом коде, т.е. 1010...101-й адрес 1010...102-й адрес 1010...103-й адрес 1010...104-й адрес 1010.. .10 N-й адрес В случае формирования тестов с инверсией включает ключи 43 и 44 в блоке инверсии 14. Причем ключ 43 включает инверсию по циклам, а клю 44 инверсию по адресам. При этом к в блоке инверсии 14 при включении ключа 43 инвертируется по циклам, т.е. на %ыходе 22 код имеет вид 1010...10 1-й адрес 1010...10 2-й адрес 1-й ци 1010...10 N-й адрес 0101,..01 1-й адрес 0101...01 2-й адрес 2-й ци 0101...01 N-йадрес где N - максимальный порядковый но мер адреса (определяется емкостью испытуемого блока). При включении ключа 44 код в бл ке инверсии 14 инвертируется по ад сам, т.е. на выходе 22 код имеет вид , .10 1-й адрес ,.01 2-й адрес ,.10 3-й адрес 0101...01 N-й адрес При включении сразу двух ключей 43 и.44 код инвертируется комбинированно по адресам и циклам, т.е. на выходе 22 код имеет вид 1010.. .10 1-й адрес 0101...01 2-й адрес 1010...10 3-й адрес 1-й цикл : : 0101.. .01N-й адрес 0101..:011-й адрес 1010...102-й адрес 2-й цикл 0101. ..013-й адрес Г 1010...16 N-й адрес Третий цикл работы повторяет коды первого цикла, а четвертый второго и т.д. Адресные стимулы формируются счетчиком импульсов 2 и представляют полный набор упорядоченных кодов, изменяющих свое значение на +1. Триггер (циклов) 33 выполнен на микросхеме 133ТМ2. Блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42 - на микросхемах 133ДП5. Задача блока инверсии 14 заключается в инвертировании проверочных тестов, поступающих с выхода 22 регистра числа 10 на числовые входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42 при включении ключей43 и 44. Если ключи 43 и 44 отключены, сигнал Логический О с ключа 43 через элемент И 43 поступает на вход первого элемента НЕ 35, ас выхода его сигнал 1 поступает на первый вход элемента И 40. Сигнал О с, ключа 44, инвертируясь на втором элементе блока НЕ 36, поступает на второй вход элемента И 40. Таким образом, на обоих входах пятого элемента И 40 будут две 1, следовательно, на выходе элемента ИЛИ-НЕ 41 будет сигнал О,который поступает на управляющий вход блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42. При этом тесты с выхода 20 регистра числа 10 транслируются через блок элементов 42 в приемном коде. Если ключ 43 включен в положение Инверсия цикла, а ключ 44 отключен, на первом входе элемента И 34 будет 1, разрешающая прохождение сигналов с триггера (циклов) 33 на первый вход элемента И 3S и через первый элемент НЕ 35 на первые входы элементов И 39, 40. При этом элемент И 40 открыт по второму входу с выхода элемента НЕ 36, а элемент И 38 закрыт по второму входу. Следовательно,

сигнал переключения с триггера 33 че-рез элемент И 34, элемент НЕ 35 и элемент И 40 проходит на выход элемента ИЛИ-НЕ 41 и далее на первый вход блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42, который при этом во время нулевого полупериода транслирует тесты в прямом коде, а во время единичного полупериода в инверсном коде.Например, если с выхода 20 регистра числа i,0 поступает код 0...01100, на выходе 38 в первом цикле тест имеет вид 0...1100, а во втором цикле тест проходит инверсным кодом, т.е. 1...10011. Таким образом, реализуется инверсия теста по циклам.

Если кл1оч 43 отключен, а ключ 44 установлен в положение Инверсия адреса, элемент И 35 будет закрыт сигналом О с тумблера 43 через элемент И 34. Сигнал 1 с ключа 44 поступит на элемент НЕ 36 и закроет элемент И 40. На первый вход элемента И 39 с элемента НЕ 35 поступит 1. Следовательно, сигнал с первого выхода 21 счетчика импульсов 2 через элемент НЕ 35 и через элемент И 39 пройдет на выход элемента ИЛИ-НЕ 41 и поступит на управляющий вход блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42. Сигналы с первого выхода 21 счетчика импульсов 2 изменяются с частотой переключения адресов. При формировании нечетных адресов сигнал имеет потенциал О, а четных -1. Следовательно, по нечетным адресам на управляющий

вход блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 42 поступает О, а по четным - 1. В этом случае по нечетным адресам тест на выходе22 имеет вид 0...01100 а по четным 1. ..10011. Таким образом, реализована инверсия по адресам.

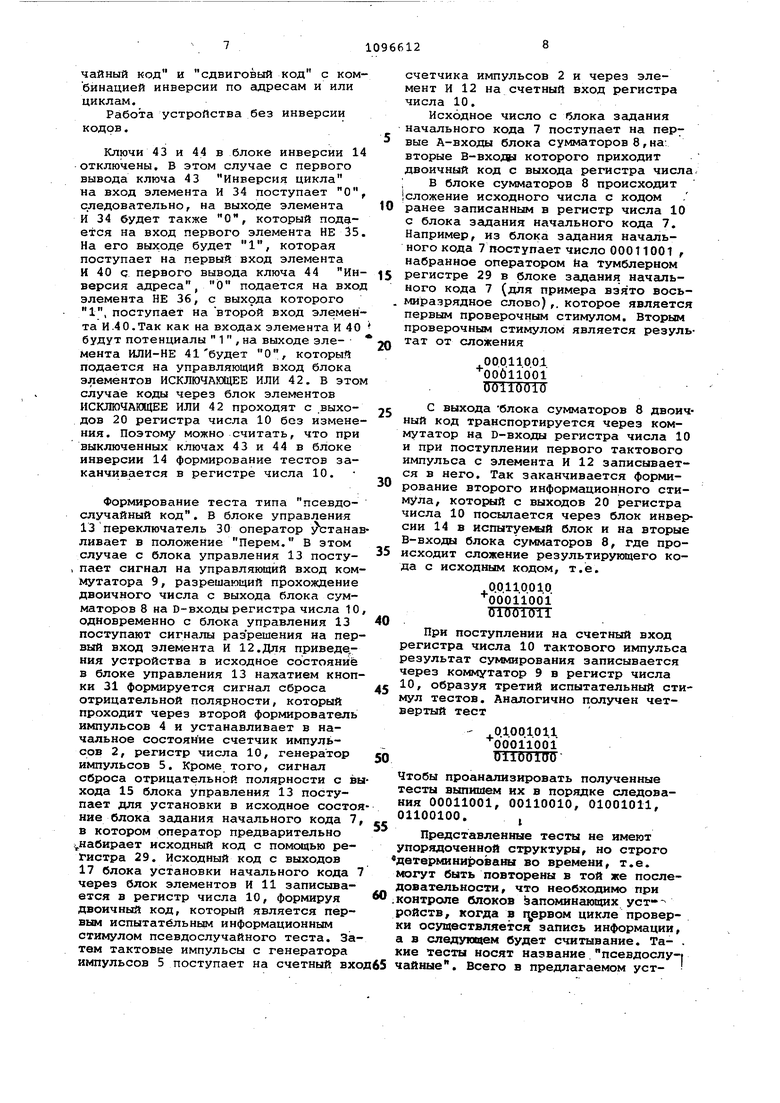

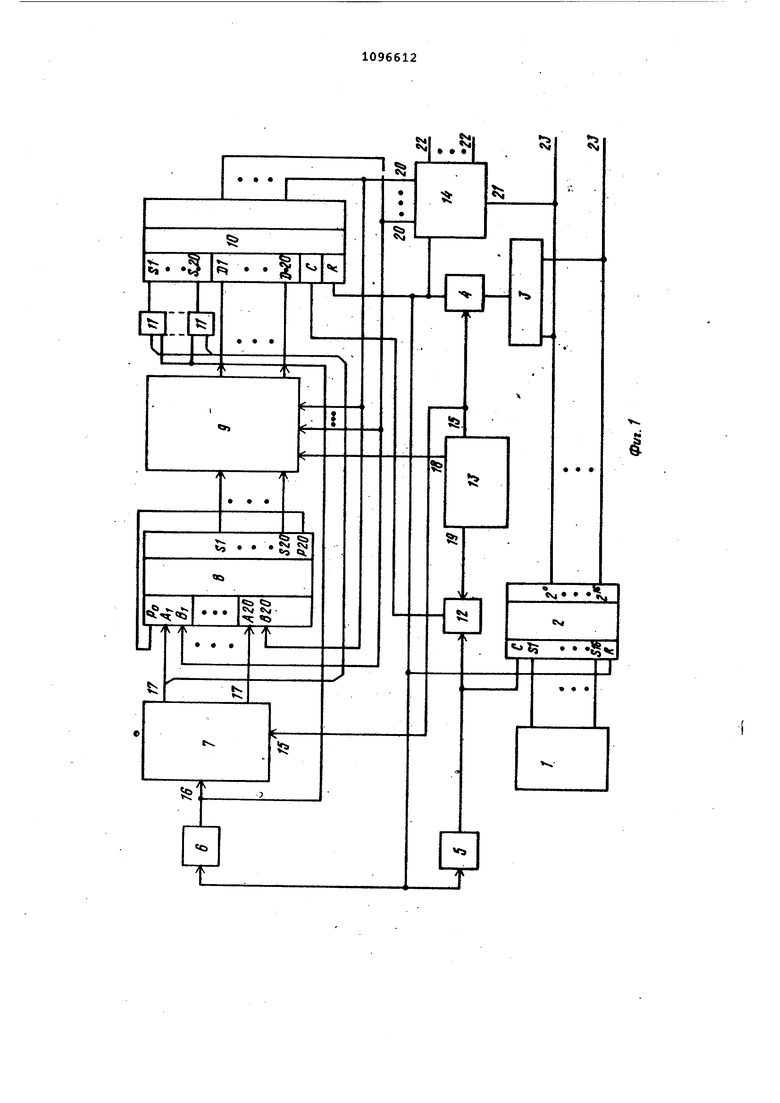

Работа блока инверсии 14 при одновременном включении ключей 43 и 44

0 поясняется временной диаграммой (фиг. 6).

Внедрение предлагаемого устройст;ва позволит значительно сократить общее время проверки блоков с па5 мятью при одновременном обеспечении высокой достоверности контроля, что приведет к значительному снижению трудоемкости проверки, повышению качества и надежности запускаемых изде0 ЛИЙ и существенному улучшению уелоВИЙ труда регулировщика, в частности к снижению егр утомляемости.

При отсутствии проверки на комби5 нированные инверсные коды неустойчивость в работе радиоэлектронных блоков с многоадресной магнитной пажитью выявляется только при функционировании их в составе комплексного прибо- ра (например, ЦВМ), где анализ и ди агностика причин неустойчивой работы значительно сложнее, приводит к излишним потерям времени на общую регулировку комплекса и вызывает дополнительные аппаратурные затраты.

18

- и fJepcM.

„ Сдвиг.г/

„ нJi I

/, f/OCfn.тгп I

Фаг, 2

fj

If

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Устройство для задания тестов | 1985 |

|

SU1290265A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для тестового контроля блоков радиоэлектронной аппаратуры | 1980 |

|

SU905887A1 |

УСТРОЙСТВО ДЛЯ ЗАДАНИЯ ТЕСТОВ ПО авт. св. 1038926, о т л ич ающе е с я тем, что, с целью расширения .функциональных возможностей устройства за счет повышения достоверности и полноты контроля устройства, в него введен блок ин версии, содержащий триггер, соединенный счетным входом с выходом второго формирователя импульсов, а прямым выходом - с первым входом второго дополнительного .элемента И, подключенного вторым входом к перваму выводу первого ключа, а выхо-;, дом - к первому входу третьего дополнительного элемента И и к входу первого элемента НЕ, соединенного выходом с первым входом четвертого дополнительного элемента И и с первым входом пятого дополнительного элемента И, подключенного вторым входом к выходу второго элемента НЕ, связанного входом с первым выводом второго ключа и с вторым входом третьего дополнительного элемента И, подключенного третьим входом к выходу первого разряда счетчика импульсов и к входу третьего элемента НЕ, соединенного выходом с вторым входом четвертого дополнительного элемента И, подключенного выходом к первому входу элемента ИЛИ-НЕ, связанного вторым и третьим i входами с выходами третьего и пятого дополнительных элементов И, (Л а выходом - с первыми входами блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенного вторыми входами к соответствующим выходам регистра числа, причем второй и третий выводы первого и второго ключей подключены соответственно с шинаМи Логическая 1 и Логический О.

19

ffx. 15

Вх.сг .

Bjt.VZ Вх.2Г

Выл Q1

дшигBbuQ3

SujfQ20

Фиг.

ггггг

- -- -с

фиг. 4

«

«

гг

инберс.ЛДР

fpvt.f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для задания тестов | 1981 |

|

SU1038926A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-06-07—Публикация

1982-04-12—Подача