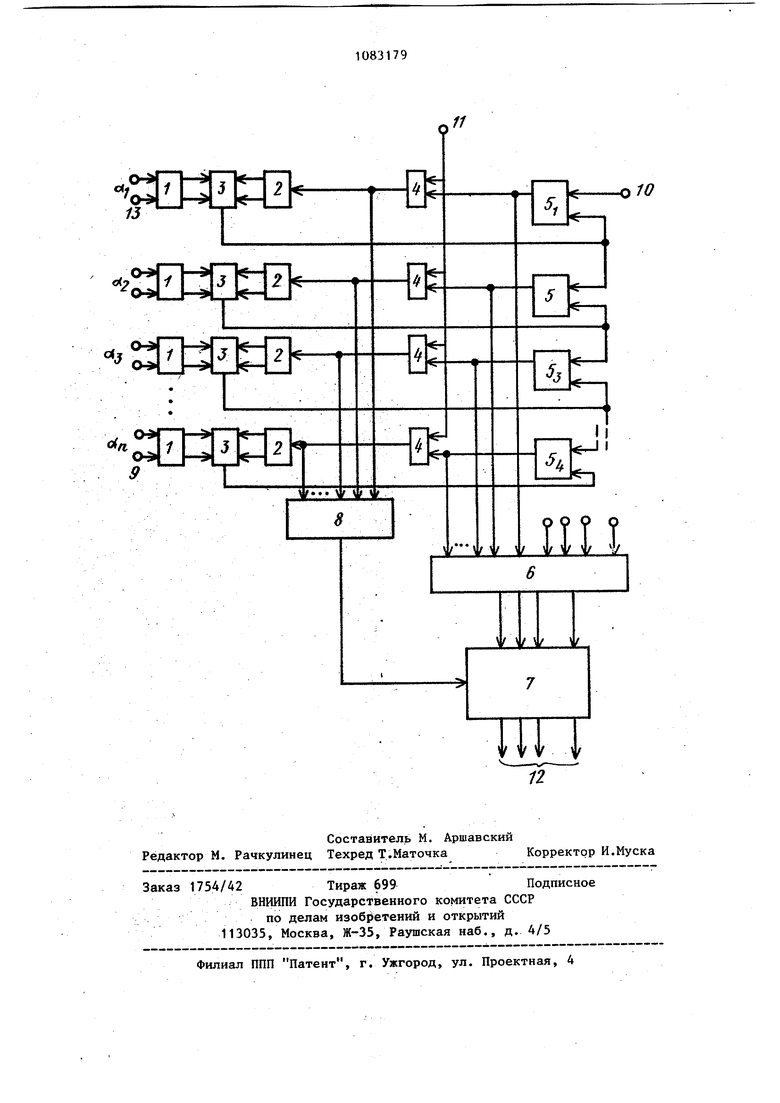

t Изобретение относится к вычисли тельной технике и может быть использовано при построении устройст сопряжения с вычислительными устро ,ствами, функционирующими в системе остаточных классов (СОЖ), а также в аппаратуре передачи данных, использующей коды СОК. Известно устройство для преобразования чисел из кода СОК в даоичный код, содержащее многовыходовый элемент И и суммирующие счетчики по числу оснований системь СОК, входы которых подключены к выходам блока управления и входу накапливающего счетчика . Недостаток данного устройства со тоит в том, что до подачи счетных импульсов в счетчики по модулю необходимо вносить значения аддитивных инверсий остатков кодового слова СОК по соответствующим основания что, в свою очередь,обуславливает не обходимость вычисления аддитивных инверсий. Кроме того, устройство характеризуется низким быстродействием. Наиболее близким к предлагаемому по технической сущности является преобразователь кода системы остаточных классов в двоичный код, содержащий суммирующие счетчики, вход ные регистры, схемы сравнения по ос нованиям СОК, двоичный счетчик, выход которого является выходом устройства, первый триггер, первый и второй злементы И, причем входы первого злемента И подключены соответственно к выходам схем сравнения кроме схемы сравнения по наибольшему основанию СОК, выходы каждого входного регистра подключены к первым группам входов соответствующих схем сравнения, вторые группы входов которых подключены к выходам соответствующих суммирующих счетчико по основаниям СОК,первый вход второго элемента И является входом тактовых импульсов, первый вход первого триг гера является входом пуска устрой ства, выход третьего злемента И подключен к счетному входу двоичног накапливающего счетчика, а первый вход - к выходу второго элемента И, первому входу четвертого элемента И и счетному входу суммирующего счетч ка по наибольшему основанию СОК, второй вход третьего элемента И под 79 к.пючен к второму входу четвертого элемента И, первый вход второго триггера подключен к первому входу первого триггера, второй вход которого подключен к входу пятого элемента И, единичный выход первого триггера подключен к второму входу второго элемента И, второй вход второго триггера и первый вход пятого элемента И объединены и подключены к выходу первого элемента И, а второй вход пятого элемента И подключен к выходу схемы сравнения по наибольшему основанию СОК 2. Недостаток известного преобразователя состоит в относительно низком быстродействии, поскольку максимальное число тактов преобразования составляет величину n-t 8, . Цель изобретения - повышение быстродействия преобразователя. Поставленная цель достигается тем, что в преобразователь непозиционного кода в двоичный код, содержапщй группу входных регистров, группу схем сравнения, группу элементов И и группу счетчиков по модулю, входы которых соединены соответственно с выходами элементов И группы, первые входы которых соединены с тактовым входом преобразователя, информационные входы которого соединены с входами входных регистров группы, выходы которых соединены с первыми входами соответствующих схем сравнения группы, вторые входы которых соединены с выходами соответствующих счетчиков по модулю группы, введены группа триггеров, элемент ИЛИ, коммутатор, накопительный сумматор по модулю, выходы которого являются выходами преобразователя, входы констант эквивалентов которого соединены с информационными входами коммутатора, выходы которого соединены с информационными входами накопительного сумматора по модулю, управляющий вход которого соединен с выходом элемента ИЛИ, входы которого соединены с выходами элементов И группы, вторые входы которых соеинены с выходами соответствующих триггеров группы и управляющими входами -коммутатора, выход i -и схемы сравнения группы ( -П ), где n - число модулей входного кода, соединен с нулевым входом i -го и единичным входом (+1)-го триггера группы, единичный вход первого триггера группы является входом пуска преобразователя. На чертеже приведена структурная схема предлагаемого преобразователя Преобразователь непозиционного кода в двоичный код содержит группу входных регистров 1, в которые заносятся остатки преобразуемого числа в СОК, группу счетчиков 2 по модулям, группу схем 3 сравнения, группу элементов И 4, группу тригге ров 5, коммутатор 6, накопительный, сумматор 7 по модулю, элемент ИЖ 8 информационный вход 10 пуска тактовый вход 11, выходы 12 съема преобразованного кода и входы 13 коэффициентов. Преобразователь работает следующим образом. В качестве алгоритма функциониро вания используется метод преобразования с помощью ортогональньпс базисов. Для СОК с основаниями Р Р. РП число А в числовом диапапзоне О-.П РЧ -1 однозначно представлено остатками Л (оС, ot ) . Согласно метода ортогональных базисов число А в- позиционной системе счисления представляется как А Cii B H-OC2B2 «-...+«(„В„, (1) где В коэффициент ортогонального базиса, которьй, в свою очередь.находится из соотношения1 коэффициент, выбираемый гП таким образом, чтобы 8j UmoaPjV Например, для СОК с основаниями , , и коэффициенты ортогонального базиса соответственно равны В 1001 , B:j и B, 192V В исходном состоянии счетчики 2 и выходной сумматор по модулю обну лены, триггеры 5 установлены в нул вое состояние. Остатки ,1162 ,... ОС по входам заносятся во входные регистры 1. Так как все триггеры 5 установлены в нулевые состояния, то нулевые потенциалы на их выходах, прикладываемые к управляющим входам схем 3 сравнения (не показано), запрещают появление на выходах сигналов сравнения, тем самым предотвращаются ложные запуски триггеров 5 в случае равенства хотя бы одного из остатков нулю. После подготовки преобразователя к работе на вход 10 поступает импульс запуска, который переводит триггер 5 в единичное состояние, разрешая тем самым сравнение содержимого регистра 1 с нулевым состоянием счетчика 2, соответствующего младшему основанию Р . Если значение первого остатка равно нулю, то сразу же по приходу разрешающего сигнала с триггера 5 на выходе схемы 3 сравнения появляется единичный сигнал, которьй сбрасывает триггер 5 в нулевое состояние и переводит его в единичное состояние. Если значение первого остатка -не равно нулю, то открьгоается элемент И 4 сигналом с триггера 5, и тактовые импульсы с входа 11 поступают через эле11|1ент И 4 на счетный вход первого счетчика 2 по модулю Р . Каждый тактовый импульс увеличивает содержимое первого счетчика по модулю на единицу. Одновременно управляющий сигнал с триггера 5 поступает на первый вход коммутатора 6, который подключает к информационньв 1 входам сумматора 7 по модулю группу входов. На эти входы подается значение соответствующего коэффициента ортогонального базиса, для приведенной СОК В,, 100%. Импульсы свыхода элемента И 4 через элемент ИЛИ 8 поступают на управляющий вход сумматора 7 по модулю, при этом с каждым пришедшим импульсом содержимое сумматора 7 по модулю увеличивается на величину коэффициента ортогонального базиса В... Когда содержимое первого счетчика 2 по модулю совпадает с содержимым первого регистра 1, на выходе схемы 3 сравнения появится импульс, который установит триггер 5 в нулевое состояние, запретив поступление тактовых импульсов через элемент И 4. Одновременно это импульс переводит триггер 5 в единичное состояние. При этом коммутатор 6 подключает к информационным входам сумматора 7 по модулю шины со значением коэффициента В. Поступающие импуль сы увеличивают содержимое.второго счетчика 2 по модулю и содержимое сумматора 7 по модулю на величину Работа преобразователя продолжается до тех пор, пока не будет достигнуто нулевое состояние всех триггеров 5. После этого тактовые импульсы не будут поступать ни на один из счетчиков 2 по модулю и на сумматор 7 по модулю. На этом процесс преобразования прекращается и его результат поступает на выход t2 преобразователя. Пусть в СОК с основаниями , , В 11 и Вд 13 число представляется остатками 064 2, oi и « Тогда после поступления импульса пуска на вход 10 до сброса триггера 5 на вход счетчика 2 по модулю поступают два импульса и содержимое сумматора 7 по модулю становится равным ОС В, 2 1001 2002. Далее поступают три импульса на вхо второго счетчика 2 по модулю, к содержимому сзч4матора 7 .по модулю добавляется величина и его содержимое становится равным 2002+2145 - 4147. После установки (В единичное состояние сумматора 7 сразу же сбрасывается и в единичное состояние устанавливается триггер 5 Содержимое сумматора 7 по модулю ув личивается на величину «1925 (17325)mod , а содержимое сумматора 7 по модулю становится 2310+4175 (6485) mod 5005 1452, что соответствует искомому результату. По сравнению с известньм предлагаемый преобразователь обладает более высоким быстродействием. В предлагаемом устройстве максимальное число тактов пре бразования составляет величину на каждом из г (по количеству оснований выбранной СОК) шагов преобразования. Таким образом, максимальное количество тактов преобразования предлагаемого преобразователя составляетn. () ЕР.- Выигрыш в быстродействии равен отношению . . . .51 Р:-п 1 Выигрьш в быстродействии для СОК основаниями Р 5, , Р 13 () можно представить в иде Ng.muy 398 12,375 раз. Пп ЧИПУ J сли эту СОК расширить одним основаием Р, 17, то 8.тах 5020 .,,/ А ТГ ля tU4,0. n-mov ° Таким образом, использование . зобретения позволяет повысить быстодействие предлагаемого преобразоателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь непозиционного кода в двоичный код | 1984 |

|

SU1179547A1 |

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

| Преобразователь кода системы остаточных классов в напряжение | 1983 |

|

SU1175034A1 |

| Устройство для преобразования чисел из кода системы остаточных классов в позиционный код с контролем ошибок | 1991 |

|

SU1797119A1 |

| Преобразователь позиционного кода в модулярный код | 1987 |

|

SU1460772A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1980 |

|

SU928339A1 |

ПРЕОБРАЗОВАТЕЛЬ НЕПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД, содержащий группу входных регистров, группу схем сравнения, группу элементов И и группу счетчиков по модулю, входы которых соединены соответственно с выходами элементов И группы, первые входы которых соединены с тактовым входом преобразователя, информаци- i онные входы которого соединены с входами входных регистров группы, выходы которых соединены с первыми входами соответствующих схем сравнения группы, вторые входа которых соединены с выходами соответствующих счетчиков по модулю группы, о тличающийся тем, что, с целью повышения, быстродействия преобразователя, в него введены группа триггеров, элемент ИЖ, коммутатор, накопительный сумматор по модулю, выходы которого являются выходами преобразователя, входы констант эквивалентов которого соединены с информационными входами коммутатора, выходы которого соединены с информационными входами накопительного сумматора по модулю, управляющий вход i которого соединен с выходом элемента ИЛИ, входы которого соединены с (Л выходами элементов И группы, вторые входы которых соединены с выходами соответствующих триггеров группы и управляющими входами коммутатора, выход -и схемы сравнения группы (-i 1 - П ) , где П - число модулей входного кода, соединен с нулевым входом i-го и единичным входом X) ((+1)-го триггера группы, едини ный 00 вход первого триггера группы является входом пуска преобразователя-. со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Обнаружение и исправление ошибок в дискретных устройствах | |||

| Под ред B.C | |||

| Толстякова | |||

| М., Советское радио, 1972, с | |||

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3350185,кл.С 06 F 5/02, 01.10.81 (прототип) | |||

Авторы

Даты

1984-03-30—Публикация

1982-12-07—Подача