элемента И блока управления, выходы третьего и четвертого коммутаторов соединены соответственно с входами первого и второго слагаемых второго сумматора по модулю, первый, второй и третий информационные входы пято-. го коммутатора соединены соответственно с выходами третьего, четвертого коммутаторов и с. выходом второго сумматора по модулю, выход счетчика блока управления соединен с управляющими входами коммутатора с первого по четвертый: выход первое го элемента И блока управления соединен с тактовым входом первого сумMiiTopa по модулю и через второй

элемент задержки блока управления с счетными входами первого и второго счетчиков, выход элемента ИЛИ блока управления соединен с входами обнуления первого и второго счетчиков, в блоке управления второй вход второго элемента.И соединен с входом одновибратора, нулевой выход которого соединен с третьим входом первого элемента И, единичный выход одновибратора соединен с вторым входом элемента ИЛИ и с сче ным входом счетчика , выход первого элемента задержки соединен с единичным входом тригге ра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Устройство для обнаружения ошибок в модулярном коде | 1985 |

|

SU1295528A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

| Преобразователь числа из двоичной системы счисления в систему остаточных классов | 1983 |

|

SU1125621A1 |

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

ПРЕОБРАЗОВАТЕЛЬ НЕПОЗИЦИОННОГО КОДА В ДВОИЧНЫЙ КОД, содержащий два счетчика, две схемы сравнения, первый сумматор по модулю, элемент И и блок управления,содержащий два элемента И,.триггер, первый элемент зaдepжкиj счетчик и схему сравнения, причем первый и второй входы первого элемента И блока управления соединены соответственно с выходом триггера и тактовым входом преобразователя, выход счетчика блока управления соединен с входом схемы сравнения блока управления, вьтход схемы сравнения блока управления и. выход элемента И соединены соответственно с первым и вторым входами второго элемента И блока управления, выход второго элемента И блока управления соединен с нулевым входом триггера блока управления, выходы первого и второго счетчиков соединены с первыми входами соответствующих схем сравнения, выходы которых соединены с соответствующими входами элемента И, выход первого сумматора по модулю является выходом результата преобразователя, отличающийся тем, что, с целью повышения быстродействия, в него введены второй сумматор по модулю, пять коммутаторов, а блок управления содержит одновибратор, второй элемент задержки и элемент ИЛИ, причем входы нечетных остатков преобразователя соединены с соответствующими информационными входами первого коммутатора, выход которого соединен с вторым входом первой схемы сравнения, входы четi ных остатков преобразователя соединены с соответствующими информаци(Я онными входами второго коммутатора, выход которого.соединен с вторым входом второй схемы сравнения, входы нечетных коэффициентов преобразователя соединены с соответствующими информационными входами третьего коммутатора, входы четных коэф sl фициентов преобразователя соедине ны с соответствующими информацион2 ными входами четвертого коммутатора, выходы первой и второй схем сравнения соединены с входами за прета соответствующих счетчиком и с соответствующими .управляющими входами пятого коммутатора, выход которого соединен с информационным входом первого сумматора по модулю, вход обнуления которого соединен с первым входом элемента ИЛИ, входом первого элемента задержки, входом обнуления счетчика блока управления и с входом запуска преобразователя, вход окончания работы которого соединен с выходом второго

1

Изобретение относится к вычислительной технике, а именно к вычислительным устройствам, функционирующим в системе остаточных классов (СОК), и может быть использовано для преобразования кодов.

Целью изобретения является повьппение быстродействия,

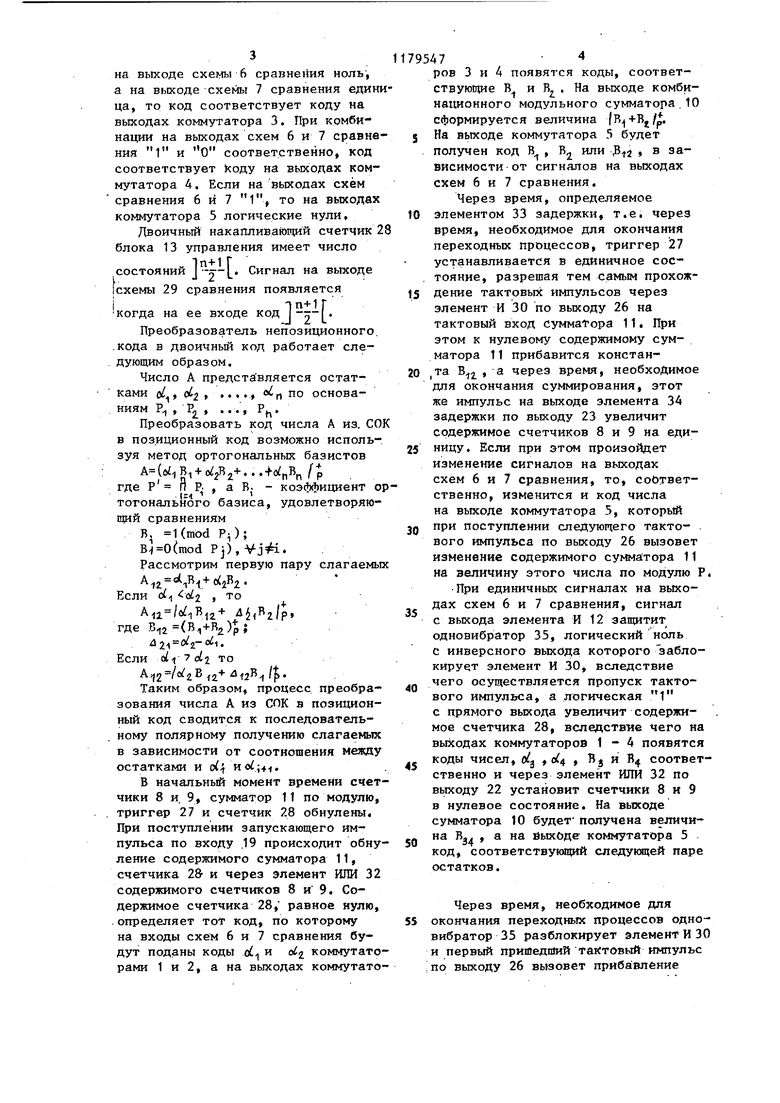

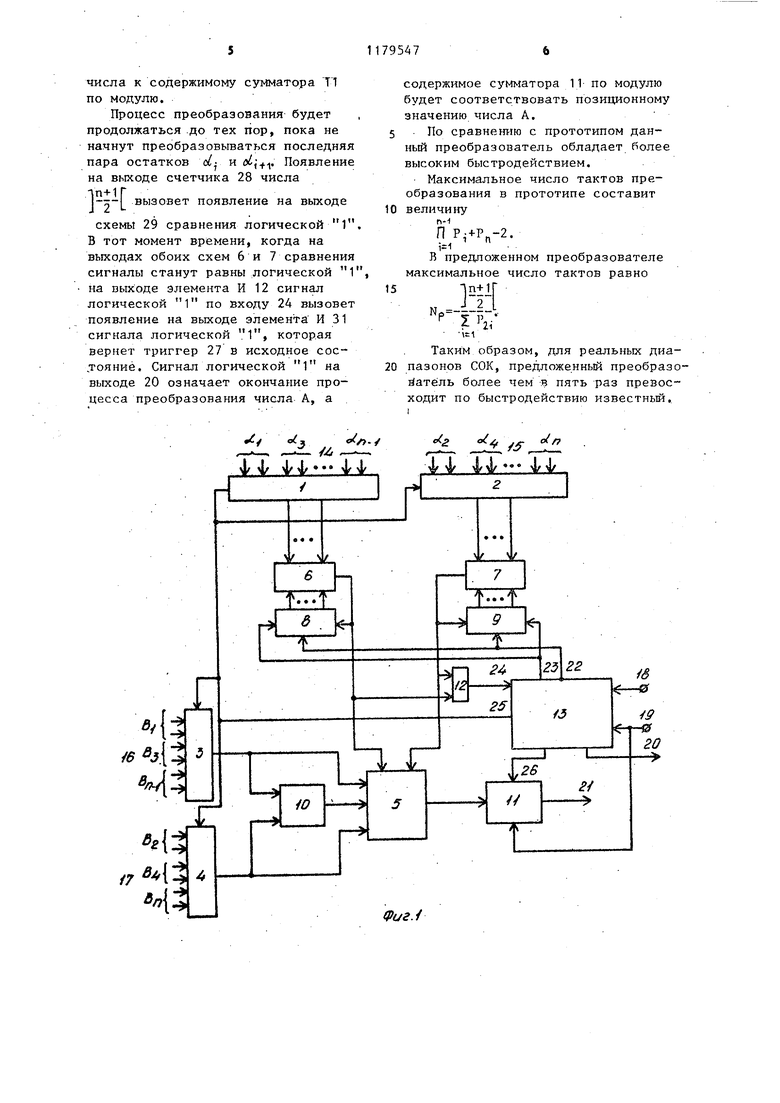

На фиг. 1 представлена схема преоСфазователя непозиционного кода в двоичный код; на фиг. 2 - схема блока управления.

Преобразователь непозиционного кода в двоичный код содержит коммутаторы 1-5, схемы 6 и 7 сравнения, счетчики 8 и 9, сумматоры 10 и 11 по модулю, элемент И 12, блок 13 управления, вхоДы 14 нечетных и 15 четных остатков преобразователя, входы 16 нечетных и 17 четных коэскЪициентов преобразователя, тактовый вход 18 преобразователя, вход 19 пуска преобразователя, выход 20 конец работы преобразователя, выход 21 результата преобразователя, выходы 22 и 23 блока управления, вход 24 блока управления, выходы 25 и 26 блока управления.

Блок 13 управления содержит триггер 27, счетчик 28, схему 29 сравнения, элементы И 30 и 31, элемент ИЛИ 32, элементы 33 и 34 задержки, одновибратор 35,

Каждый из коммутаторов 1 и 2 имеRi

групп входов, где п - чисет

ло основания выбранной СОК, по m - разрядов в каждой группе, где m lqg2Pj ; РП - наибольшее по величине основание.

Выходы коммутаторов 1 и 2 подключены к входам схем 6 и 7 сравнения соответственно. Если величина кодов подаваемых с выходов счетчиков 8 и 9, соответственно больше, то на выходах схем 6 и 7 сравнения формируется уровень логического О, если меньше или равно, то формируется уровень логической 1. Счетчики 8 и 9 представляют собой двоичные суммирую1цие счетчики. ,

Сумматор 10 является комбинационным сумматором по модулю tl.Ii Входы л-модульного сумматора 10 подключены к входам коммутаторов 3 и 4 соответственно, которые имеют

I S групп входов по разрядов

в каждой.

Выходы коммутатора 5 подключены к входам модульного сумматора 1 накапливакдцего типа по модулю , Причем если на выходах схем 6 и 7 сравнения нули, то код на выходах коммутатора 5 соответствует коду на выходах сумматора 10. Если

на выходе схемы 6 сравнения ноль, а на выходе схемы 7 сравнения единица, то код соответствует коду на выходах коммутатора 3. При комбинации на выходах схем 6 и 7 сравнения 1 и о соответственно, код соответствует Коду на выходах коммутатора 4. Если на выходах схем сравнения 6 и 7 1, то на выходах коммутатора 5 логические нули,

Двоичньй накапливанзщий счетчик 2 блока 13 управления имеет число

состояний Сигнал на выходе схемы 29 сравнения появляется

тп+П когда на ее входе код

Преобразователь непозиционного, кода в двоичный код работает следующим образом.

Число А представляется остатками 0/, п по основаниям Р , Р , ..., Р.

Преобразовать код числа А из. СОК в позиционный код возможно используя метод ортогональных базистов

, + где Р П I , а В. - коэффициент ортогонального базиса, удовлетворяющий сравнениям

В, 1(mod PV);

в)0(;тоа PJ), j.

Рассмотрим первую пару слагаемых

A,j (2B2 Если 1

, где B-,2(Bi+B2)p|

u ofi-oit, Если 7 oij то

A,j2 Б

Таким образом, процесс преобразования числа А из СОК в позиционный код сводится к последовательному полярному получению слагаемых в зависимости от соотношения между остатками и oi .

В начальный момент времени счетчики 8 и. 9, сумматор 11 по модулю, триггер 27 и счетчик 28 обнулены4 При поступлении запускающего импульса по входу .19 происходит обнуление содержимого сумматора 11, счетчика 28г к через элемент ИЛИ 32 содержимого счетчиков 8 и 9. Содержимое счетчика 28, равное нулю, определяет тот код по которому на входы схем 6 и 7 сравнения будут поданы коды о и коммутаторами 1 и 2, а на выходах коммутато79547 4

ров 3 и 4 появятся коды, соответствующие В и В. . На вькоде комбинационного модульного сумматора.10 сформируется величина (.

J На выходе коммутатора 5 будет . получен код В , В, или , в зависимости от сигналов на выходах схем 6 и 7 сравнения.

Через время, определяемое

10 элементом 33 задержки, т.е. через время, необходимое для окончания переходных процессов, триггер 27 устанавливается в единичное состояние, разрешая тем самым прохождение тактовых импульсов через элемент И 30 по вькоду 26 на тактовый вход сумматора 11 При этом к нулевому содержимому сумматора 11 прибавится констан20 , , а через время, необходимое для окончания суммирования, этот же импульс на выходе элемента ЗА задержки по выходу 23 увеличит содержимое счетчиков 8 и 9 на еди5 ниду. Если при этом произойдет изменение сигналов на выходах схем 6 и 7 сравнения, то, соответственно, изменится и код числа на выходе коммутатора 5, который

Q при поступлении следующего такто- . вого импульса по выходу 26 вызовет изменение содержимого сумматора 11 на величину этого числа по модулю Р,

При единичных сигналах на выходах схем 6 и 7 сравнения, сигнал

5 с выхода элемента И 12 защитит одновибратор 35, логический ноль с инверсного выхода которого заблокирует элемент И 30, вследствие

чего осуществляется пропуск тактового импульса, а логическая 1 с прямого выхода увеличит содержимое счетчика 28, вследствие чего на выходах коммутаторов 1 - 4 появятся коды чисел, 3 и В соответственно и через элемент ИЛИ 32 по вьпсоду 22 установит счетчики 8 и 9 в нулевое состояние. На выходе сумматора 10 будет получена величина В. , а на Выходе коммутатора 5 код, соответствующий следукяцей паре остатков.

Через время, необходимое для окончания переходных процессов одновибратор 35 разблокирует элемент И 30 и первый приведший тактовый импульс . по выходу 26 вызовет прибавление

числа к содержимому сумматора ТТ по модулю.

Процесс преобразования будет продолжаться .до тех пор, пока не начнут преобразовываться последняя пара остатков d- и (З,-.. Появление на выходе счетчика 28 числа ЛП+1Г j-T-L вызовет появление на выходе

схемы 29 сравнения логической 1 В тот момент времени, когда на выходах обоих схем 6 и 7 сравнения сигналы станут равны логической 1 на выходе элемента И 12 сигнал логической 1 по входу 24 вызовет появление на выходе элемента И 31 сигнала логической 1, которая вернет триггер 27 в исходное сос.тояниё. Сигнал логической 1 на выходе 20 означает окончание процесса преобразования числа А, а

V

содержимое сумматора 11 по модулю будет соответствовать позиционному значению числа А.

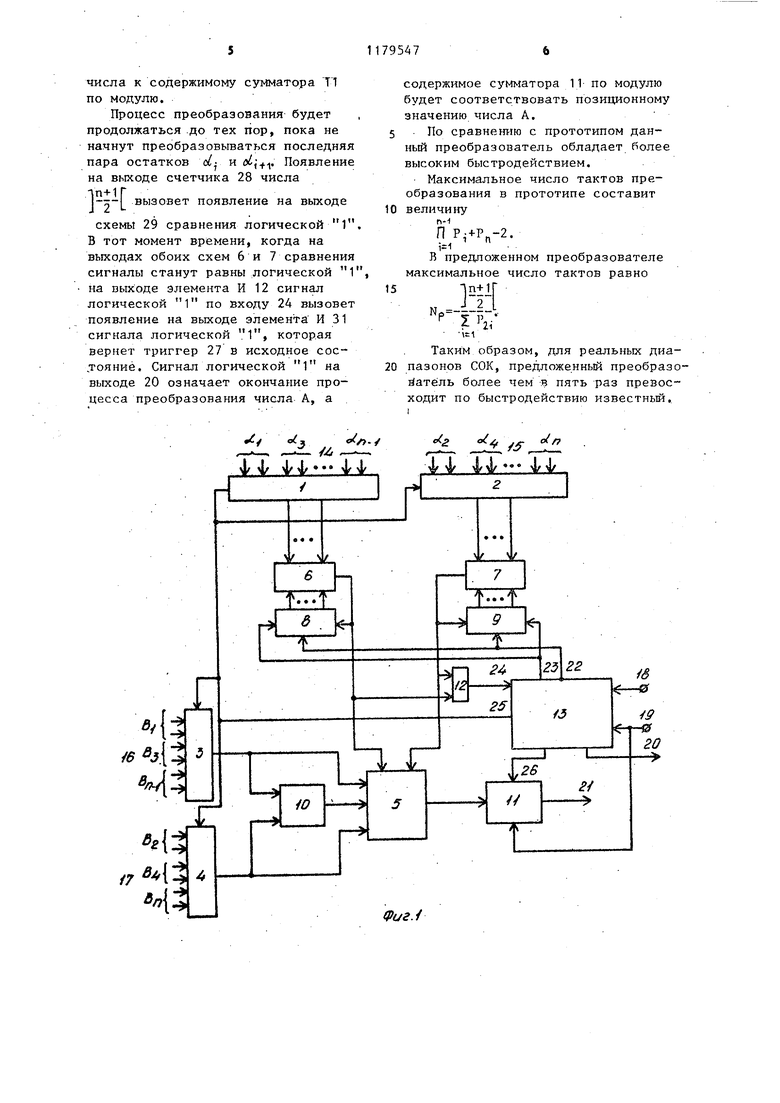

По сравнегтю с прототипом данный преобразователь обладает более высоким быстродействием.

Максимальное число тактов преобразования в прототипе составит

величину

.Р,-2.

В предложенном преобразователе максимальное число тактов равно -|п+1Г

Таким образом, для реальных диапазонов СОК, предложенный преобразователь более чем в пять раз превосходит по быстродействию известный.

К

о(,7

S

фф WW 1/4/

Фиг. г

| Толстяков B.C | |||

| Обнаружение и исправление ошибок в дискретных устройствах | |||

| М.: Советское радио, 1972, с | |||

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1981 |

|

SU991410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-04-18—Подача