узла свертки по модулю т соединены с первыми входами соответствующих сумматоров по модулю два группы, вторые входы которых объединены и соединены с выходом сумматора по мсдулю,два,..«ви«эДБ1 чётве15Того узла сло1ю,два, жен1|я nq, (|$ ЙЙ:оедйнены с первой

1ф1 П( ,

1.

;,, i . |- I

,,f К.. I ,,,Й ;

,v ,-иг,-««

группой входов третьего узла вычитания по модулю т, вторая группа входов которого соединена с выходами сумматоров по модулю два группы, выход третьего узла вычитания по модулю m соединен с вторым входом блока сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля по модулю умножения комплексных чисел | 1986 |

|

SU1386997A1 |

| Устройство для контроля умножения чисел по модулю | 1985 |

|

SU1259269A1 |

| Устройство для контроля по модулю умножения комплексных чисел | 1985 |

|

SU1285479A1 |

| Устройство для контроля по модулю @ умножения матриц чисел | 1984 |

|

SU1297053A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1348836A1 |

| Устройство для контроля по модулю три умножения комплексных чисел | 1987 |

|

SU1434438A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для контроля умножения по модулю | 1975 |

|

SU595737A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ т, содержащее регистры контрольных разрядов множимого и множителя, четыре узла сложения по модулю m, два узла вычитания по модулю in, узел умножения по модулю tn три узла свертки по модулю In, блок сравнения, причем вход первого узла свертки по модулю mобъединен с первым входом первого узла сложения по модулю m и является входом порядка множимого устройства, вход второго узла свертки по модулю т объединен с первым входом второго узла сложения по модулю m и является входом порядка множителя устройства, вторые входы первого и второго узловсложения по модулю гп являются входами мантиссы множимого и мноясителя устройства соответственно, выходы первого и второго узлов сложения по модулю fn соединены соответственно с информационными входами регистра контрольных разрядов множимого и регистра контрольных разрядов множителя, выходы которых соединены с первыми входами первого и второго узлов вычитания по модулю ГП соответственно, выход первого уэла свертки по модулю mсоединен с первым входом третьего узла сложения по модулю m и вторым входом первого узла вычитания по модулю т, выход которого соединен с первым входом узла умножения по модулю Гп, второй вход которого соединен с выходом второго узла вычитания по модулю два, второй вход которого соединен с выходом второго узла свертки по модулю in и вторым входом третьего узла сложения по модулю w, выход т которого соединен с первым входом четвертого узла сложения по модулю с т, второй вход которого соединен с выходом узла умножения по модулю hi, § выход третьего узла свертки по модулю m соединен с первым входом блока сравнения, выход которого является выходом неиспргвности устройства, вход третьего узла свертки по модуч лю .т является входом результата уст ройства, отличающееся тем, что, с целью повышения точности контроля, в него введены сумматор по модулю два, группа сумматоров по модулю два, четвертый узел свертки по модулю fn и третий узел вычитания по модулю m, причем первый и второй входы сумматора по модулю два являются соответственно входами знака множимого и множителя соответственно, вход четвертого узла свертки по модулю пг является входом отбрасываемых разрядов результата устройства, выходы контрольных разрядов четвертого

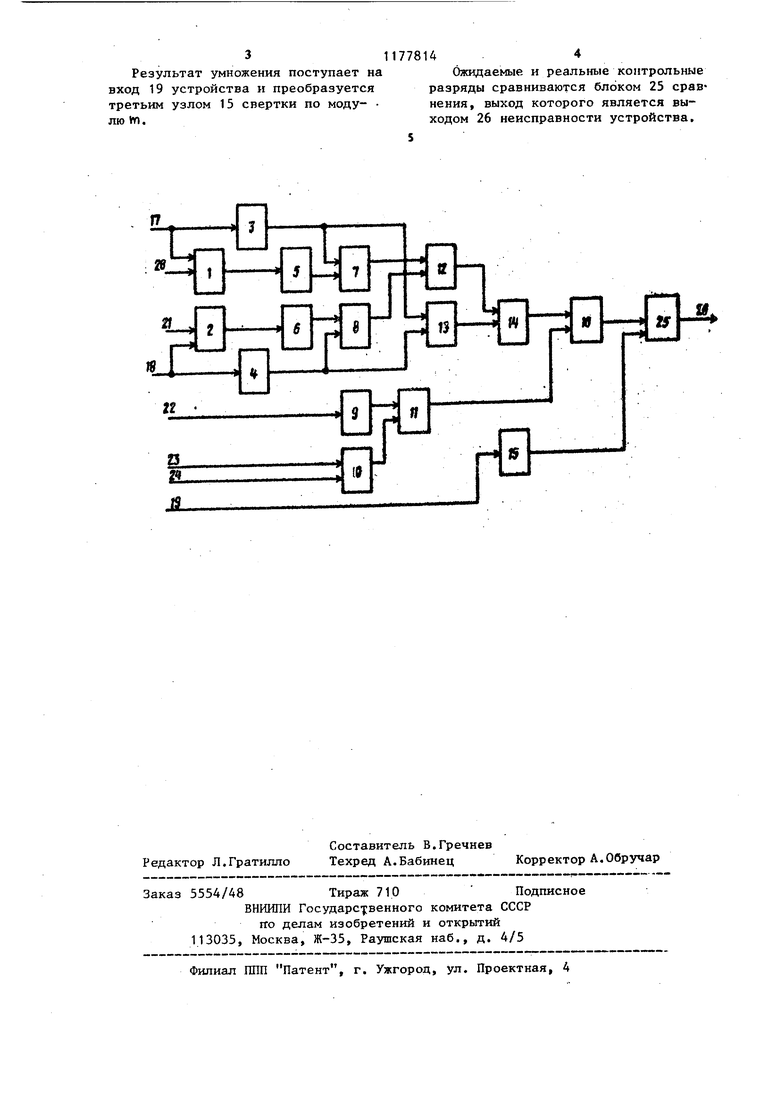

Изобретение относится к вычислительной технике и может быть исполь зовано в арифметических устройствах Целью изобретения является повышение точности контроля. На чертеже приведена структурная схема устройства для контроля умнож ния по модулю т. Устройство содержит первый узел сложения по модулю т, второй узел 2 сложения по модулю in, первый узел 3свертки по модулю ID, второй узел 4свертки по модулю т, регистры.5 и 6 контрольных разрядов множимого и множителя, первый узел 7 вычитания по модулю т, второй узел 8 вычитания по модулю т, четвертый узел 9 свертки по модулю т, сумматор 10 по модулю два, группу 11 сумматоров по модулю два, узел 12 умножения по модулю два, третий узел 13 сложения по модулю т, четвертый узел 14 слож ния по модулю In, третий узел 15 ки по модулю т, третий узел 16 вычитания по модулю ГГ), вход 17 порядк множимого устройства, вход 18 поряд ка множителя устройства, вход 19 результата устройства, входы 20 и 21 мантиссы множимого и множителя устройства, вход 22 отбрасываемых разрядов результата устройства, входы 23 и 24 знака множимого и мно жителя, блок 25 сравнения, выход 26 неисправности устройства. Устройство для контроля умножения чисел по модулю m работает еледунхцим образом. В начальный момент на входы 20 и 21 мантисс множимого, и множителя устройства поступают соответственно обратные коды мантиссы множимого и множителя, а на входы 17 и 18 устройства - обратные коды порядков множимого и множителя. Первый узел 1 сложения по модулю Гп осуществляет суммирование по модулю кодов мантиссы и порядка множимого, результат записывается на регистр 5 контрольных разрядов множимого, Второй узел 2 сложения по модулю ИЛ осуществляет суммирование по модулю кодов мантиссы и порядка множителя, результат Записьпзаетсяна регистр 6 контрольных разрядов множителя. Первый и второй узлы 7 и 8 вычитания по модулю m формируют соответственно контрольные разряды мантисс множимого и множителя с помощью первого и второго узлов 3 и 4 свертки по модулю т. Контрольные разряды мантисс множителя и множимого перемножаются узлом 12 умножения, формируя контрольные разряды мантиссы результата. Третий узел 13 сложения по модулю m формирует контрольные разряды порядка результата. Сумматор 10 по модулю два формирует код знака результата по кодам знака множимого и множителя, поступающим на входы 23 и 24 устройства. Четвертый узел 9 свертки по модулю гц формирует контрольные разряды отбрасываемой части результата, которые поступают на входы сумматоров по модулю два группы 11, где складываются с сигналом с выхода сумматора ТО по модулю два. Четвертый узел 14 сложения по модулю два и третий узел 16 вычитания по модулю m осуществляют формирование ожидаемых контрольных разрядов результата.

11778144

Результат умножения поступает на Ожидаемые и реальные контрольные вход 19 устройства и преобразуется разряды сравниваются блоком 25 сравтретьим узлом 15 свертки по моду- - „ения, выход которого является вы ходом 26 неисправности устройства.

17

и

№

21

CV

«.

гу

22

я

РиГ

| 1970 |

|

SU411454A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля умножения по модулю | 1975 |

|

SU595737A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-07—Публикация

1984-03-27—Подача