2

00

2

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностики цифровых устройств, в том числе содержащих элементы с тремя состояниями на входе.

Цель изобретения - упрощение сигнатурного анализатора.

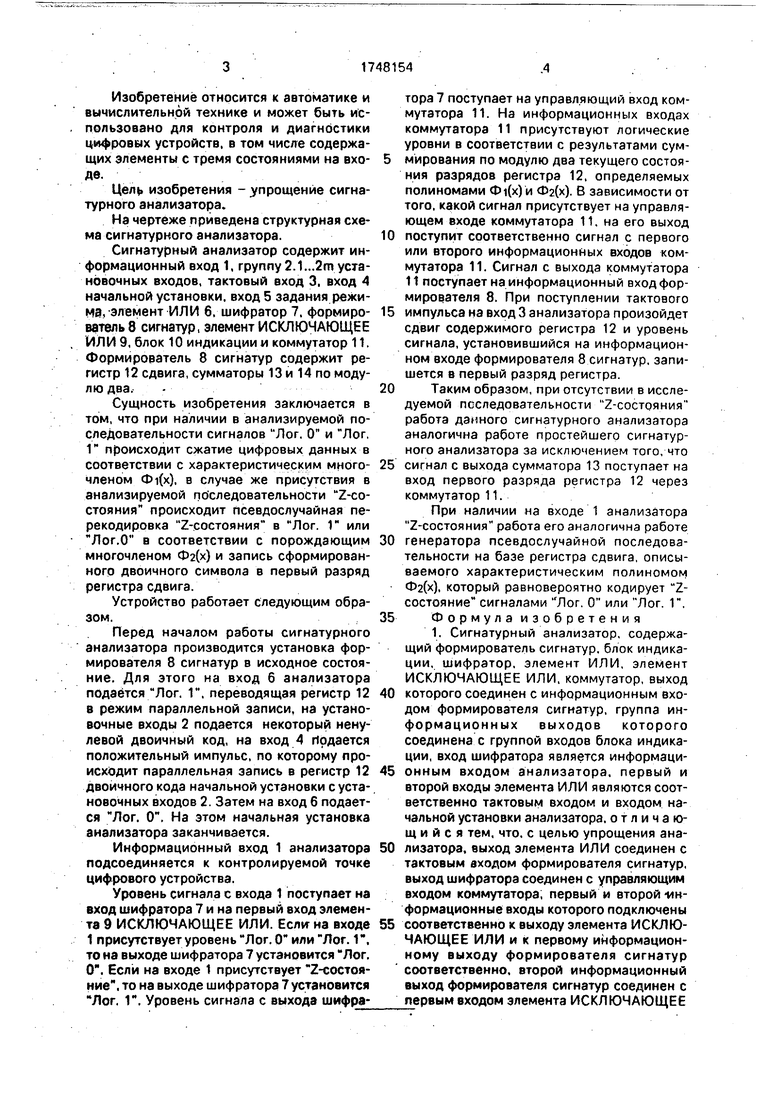

На чертеже приведена структурная схема сигнатурного анализатора.

Сигнатурный анализатор содержит информационный вход 1, группу 2.1...2т установочных входов, тактовый вход 3. вход 4 начальной установки, вход 5 задания режима,-элемент ИЛИ 6. шифратор 7. формирователь 8 сигнатур, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9, блок 10 индикации и коммутатор 11. Формирователь 8 сигнатур содержит регистр 12 сдвига, сумматоры 13 и 14 по модулю два.

Сущность изобретения заключается в том, что при наличии в анализируемой последовательности сигналов Лог. О и Лог. 1 происходит сжатие цифровых данных в соответствии с характеристическим многочленом Oi(x), в случае же присутствия в анализируемой последовательности Z-co- стояния происходит псевдослучайная перекодировка Z-состояния в Лог. Г или Лог.О в соответствии с порождающим многочленом Фа(х) и запись сформированного двоичного символа в первый разряд регистра сдвига.

Устройство работает следующим образом.

Перед началом работы сигнатурного анализатора производится установка формирователя 8 сигнатур в исходное состояние. Для этого на вход 6 анализатора подается Лог. 1, переводящая регистр 12 в режим параллельной записи, на установочные входы 2 подается некоторый ненулевой двоичный код, на вход А Подается положительный импульс, по которому происходит параллельная запись в регистр 12 двоичного кода начальной установки с установочных входов 2. Затем на вход б подается Лог. О. На этом начальная установка анализатора заканчивается.

Информационный вход 1 анализатора подсоединяется к контролируемой точке цифрового устройства.

Уровень сигнала с входа 1 поступает на вход шифратора 7 и на первый вход элемента 9 ИСКЛЮЧАЮЩЕЕ ИЛИ. Есл на входе 1 присутствует уровень Лог. О или Лог. 1. то на выходе шифратора 7 установится Лог. О. Если на входе 1 присутствует 2-состоя- ние, то на выходе шифратора 7 установится Лог. Г. Уровень сигнала с выхода шифратора 7 поступает на управляющий вход коммутатора 11. На информационных входах коммутатора 11 присутствуют логические уровни в соответствии с результатами суммирования по модулю два текущего состояния разрядов регистра 12, определяемых полиномами Oi(x) и Фа(х). В зависимости от того, какой сигнал присутствует на управляющем входе коммутатора 11. на его выход

поступит соответственно сигнал с первого или второго информационных входов коммутатора 11. Сигнал с выхода коммутатора 11 поступает на информационный вход формирователя 8. При поступлении тактового

импульса на вход 3 анализатора произойдет сдвиг содержимого регистра 12 и уровень сигнала, установившийся на информационном входе формирователя 8 сигнатур, запишется в первый разряд регистра.

Таким образом, при отсутствии в исследуемой последовательности Z-состояния работа данного сигнатурного анализатора аналогична работе простейшего сигнатурного анализатора за исключением того, что

сигнал с выхода сумматора 13 поступает на вход первого разряда регистра 12 через коммутатор 11.

При наличии на входе 1 анализатора Z-состояния работа его аналогична работе

генератора псевдослучайной последовательности на базе регистра сдвига, описываемого характеристическим полиномом Ф2(х), который равновероятно кодирует Z- состояние сигналами Лог. О или Лог. 1.

Формула изобретения

1. Сигнатурный анализатор, содержащий формирователь сигнатур, блок индикации, шифратор, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. коммутатор, выход

которого соединен с информационным входом формирователя сигнатур, группа информационных выходов которого соединена с группой входов блока индикации, вход шифратора является информационным входом анализатора, первый и второй входы элемента ИЛИ являются соответственно тактовым входом и входом начальной установки анализатора, отличающийся тем, что. с целью упрощения анализатора, выход элемента ИЛИ соединен с тактовым входом формирователя сигнатур, выход шифратора соединен с управляющим входом коммутатора, первый и второй информационные входы которого подключены

соответственно к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к первому информационному выходу формирователя сигнатур соответственно, второй информационный выход формирователя сигнатур соединен с

первым входом элемента ИСКЛЮЧАЮЩЕЕ

5 17481546

ИЛИ, второй вход которого подключен к ин-мирователя, группа входов параллельной

формационному входу анализатора, группазаписи и группа разрядных выходов регистустановочных входов формирователя сигна-ра сдвига образуют группу установочных

тур образует группу одноименных входоввходов и группу информационных выходов

анализатора, вход задания режима форми-5 формирователя соответственно, выходы

рователя сигнатур является одноименнымпервого и второго сумматоров по модулю

входом анализатора.два являются первым и вторым информаци2. Анализатор по п. 1,отличающий-онными выходами формирователя, разрядс я тем, что формирователь сигнатур содер-ные выходы регистра сдвига, номера

жит регистр сдвига и два сумматора по мо-10 которых соответствуют ненулевым коэффидулю два, информационный вход, входциентам первого и второго образующих

задания режима и тактовый вход регистрамногочленов, подключены к входам первого

сдвига образуют одноименные входы фор-и второго сумматоров по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1989 |

|

SU1649547A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор | 1986 |

|

SU1361555A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1998 |

|

RU2133057C1 |

| Сигнатурный анализатор | 1984 |

|

SU1179341A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для встроенного тестового контроля | 1986 |

|

SU1324029A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для встроенного контроля цифровых блоков | 1986 |

|

SU1397920A1 |

| Сигнатурный анализатор | 1986 |

|

SU1383360A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования цифровых устройств. Цель изобретения - упрощение устройства. Сигнатурный анализатор содержит элемент ИЛИ 6. шифратор 7, формирователь 8 сигнатур, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 9, блок 10 индикации и коммутатор 11. В формирователь сигнатур входят регистр 12 сдвига и сумматоры 13,14 по модулю два. При отсутствий в исследуемой последовательности Z-состояния работа устройства аналогична работе простейшего сигнатурного анализатора. При поступлении на информационный вход Z-состояния анализатор работает в режиме генератора псевдослучайной последовательности. 1 э.п. ф-лы, 1 ил.

| Сигнатурный анализатор | 1989 |

|

SU1649547A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| . | |||

Авторы

Даты

1992-07-15—Публикация

1990-05-21—Подача