(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ

УЗЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1984 |

|

SU1264186A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1148009A1 |

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для тестового диагностирования цифровых блоков | 1987 |

|

SU1622884A1 |

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

| Устройство для диагностики цифровых узлов | 1982 |

|

SU1071979A1 |

| Устройство для контроля электрического монтажа | 1986 |

|

SU1336037A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

1

Изобретение относится к автоматиЧескому контролю и может быть использовано для проверки дискретных объектов.

Известно устройство для контроля цифровых узлов, содержащее счетчик, выхода которого соединены с эталонным и контрольным блоками, выходы последних соединены с выходeiMK схем сравнения, выходы схем сравнения с блоком регистрации, а также содержащее генератор упрайляквдих сигналов выходы которого подключены к управЛ5ШЩИМ входам эталонного и контролируемого блоков l.

Нгшболее близким по технической сущности к предлагаемому устройству является устройство для контроля хщфровых узлов, содержащее генератор тестов, каждый выход которого является информационным выходом устройства и соединен с соответствующим входом эталонного цифрового узла, группой выходов подключенного к первой группе информационных входов блока сравнения, вторая группа информационных входов которого является группой информационных входов устройства, а группа выходов подключена к группе информационных входов

регнстрат ч а неисправностей, установочньй Bxogoi которого является установочшш входш устройства, а группа выходов соединена с первой группой инфотшионных входов блока индикгщии {2J

Недостатком устройства является ограниченная полнота контроля, вызяанная тем, что тест синтезируемый

0 генератором асввдсслучайного кода, является, в общем случае, неполным, а также недостаточная надежность устройства, вытекающая из отсутствия самоконтроля генератора тестов.

Цель изобретения - увеличение

5 полноты контроля и надежности устройства.

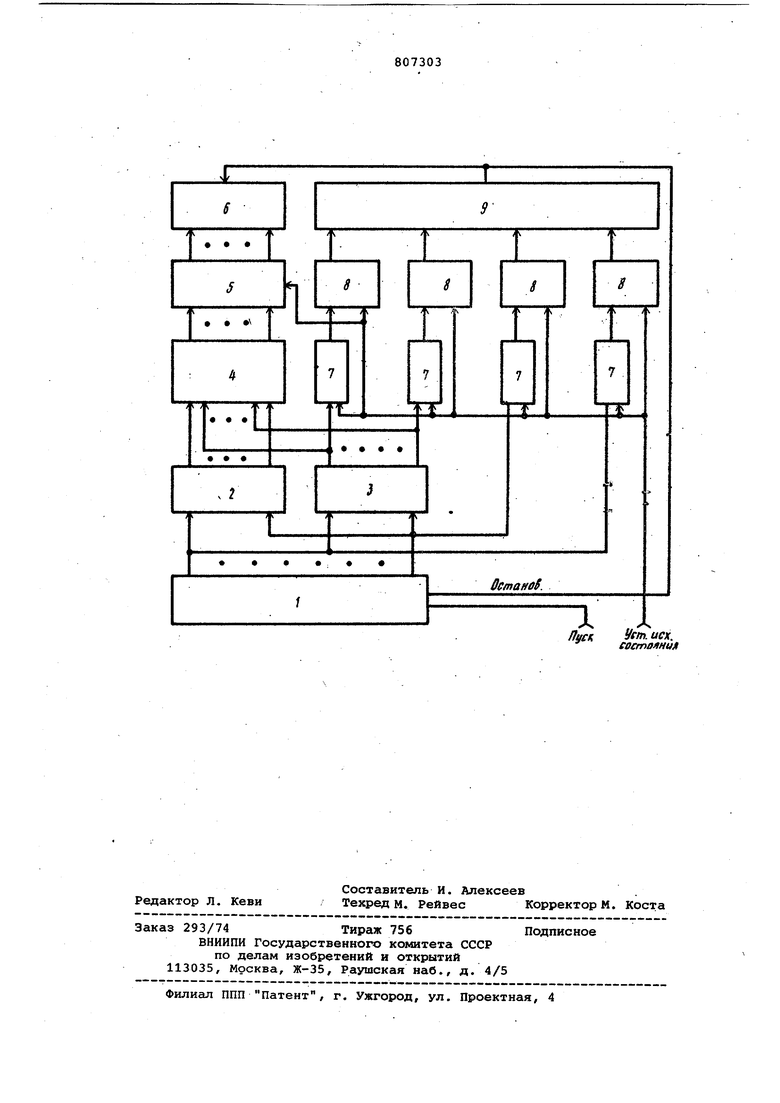

Указанная цель достигается тем, что устройство содержит элемеят И, а также триггеры и счетчики по чис0лу выходов эталонного цифрового узла, причш«, выходы эталонного цифрового узла подключены к информационным входам соответствующих счетчиков,

S выходами подЬоедииенных к инф н мацноншм входам соответствующих триггеров, установочные входы которах соединены с установочными входами соответствующих счетчиков, установоч|ным входом устройства, выходы триг0геров соответственно соединены с входами элемента И, выходом подключенного к второму информационному входу блока индикации и управляющему входу генератора тестов. На чертеже схематически представ ено устройство. Устройство содержит генератор 1 тестов, контрхэлируемый цифровой узе 2,эталоннЕлй цифровой узел 3, блок сравнения, регистратор 5 неисправностей , блок б индикации , счетчики 7, триггеры 8, элемент И 9. Входы установки исходно го состояния регис ратора 5, счетчиков 7, триггеров 8 соединены общей шиной для выполнени предварительного обнуления. Генерат 1 тестов вырабатывает входные последовательности, поступакицие на иде тичные входы контролируемого 2 и эталонного 3 узлов. Ответные реакци узлов сравниваются между собой блокем 4. Диагностическая информация записывается регистратором 5 и инди цируется на блоке б. Счетчики 7 про раммируются на ожидаемое количество единиц, поступающих с входов и выходов узла 3 и зависящих от последовательности входных воздействий, синхронизируемых генератором 1. В случае нарушения последовательности входных воздействий или появления неисправности вида const 1 или const О на входах узлов 2 или 3,соответствующие счетчики 7 не заполняются до прогр 1ммного значени и не вьшают единичный сигнал на соответствующие триггерял 8. В случае сигнала с элемента И 9 не по тупает на блок б, что указывает на возникновение неисправности. В случае отсутствия перечисленных неиспр ностей все счетчики вццают сигналы по их заполнению, которые описанным образом передаются на выход элемент И 9, откуда поступают на блок б для индикации генератора 1 для остановки контроля. Существенные отличительные признаки изобретения позволяют обеспечить повышение полноты контроля за счет пополнения списка неисправностей и надежности за счет, самоконтроля генератора 1 и узла 3. Формула изобретения Устройство для контроля цифровых узлов, содержащее генератор тестов, каждый выход которого является информационным выходом устройства и соединен с соответствующим входом эталонного цифрового зла, группой выходов подключенного к первой группе информационных входов блока сравнения, вторая группа информационных входов которого является группой информационных входов устройства, а группа выходов подключена к группе информационных входов регистрлтора неисправностей, установочный вход которого является установочным входом устройства, а группа выходов соединена с первой группой информационных входов блока индикации, о тличающееся тем, что, с целью увеличения полноты контроля и надежности устройства, оно содержит элемент И, а также триггеры и счетчики по числу выходов эталонного цифрового узла, причем, выходы эталонного цифрового узла подключены к информационным соответствующих триггеров, установочные входы которых соединены с установочными входами соответствующих счетчиков, установочным входом устройства, выходы триггеров соответственно соединены с входами элемента И, выходом подключенного к второму информационному входу блока индикации и управляющему входу генератора тестов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 441532, кл. G 06 F 11/04, 1974. 2.Аплен и др. Выбор контрольных кодов для проверки цифровых схем на сложных схемных платах. - Электроника, 1972, 15, (прототип).

Пуси у fin- чех. состмним

Авторы

Даты

1981-02-23—Публикация

1979-02-12—Подача